LABORATORIO DE ELECTRÓNICA DIGITAL Práctica 6

Anuncio

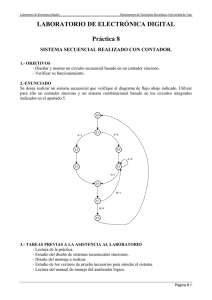

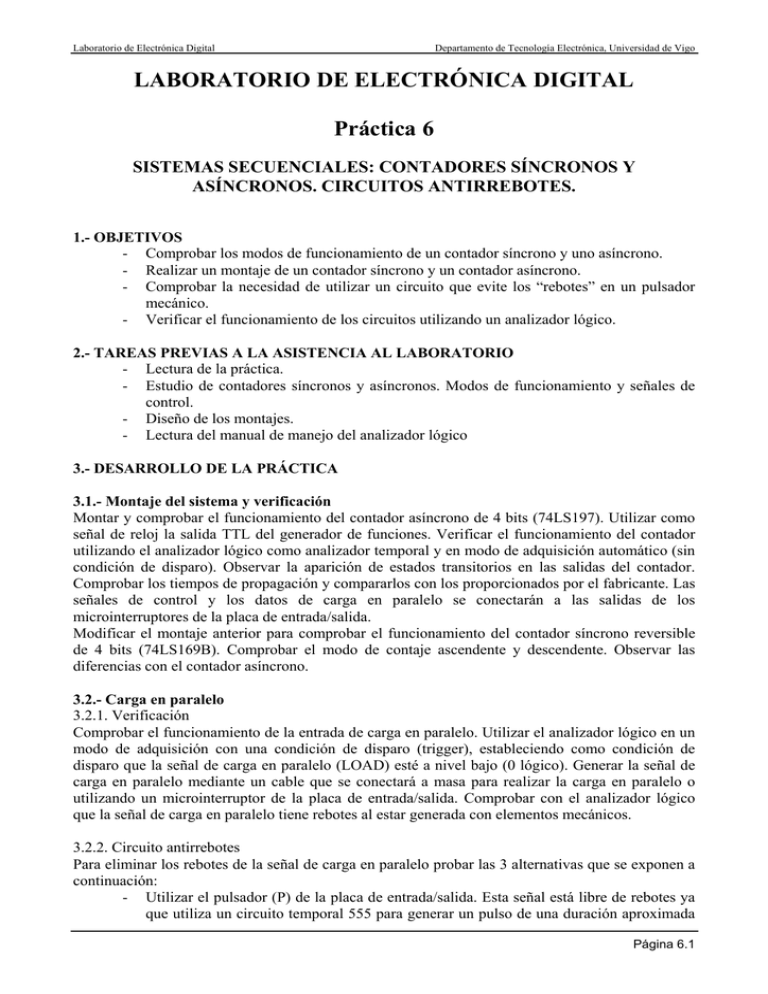

Laboratorio de Electrónica Digital Departamento de Tecnología Electrónica, Universidad de Vigo LABORATORIO DE ELECTRÓNICA DIGITAL Práctica 6 SISTEMAS SECUENCIALES: CONTADORES SÍNCRONOS Y ASÍNCRONOS. CIRCUITOS ANTIRREBOTES. 1.- OBJETIVOS - Comprobar los modos de funcionamiento de un contador síncrono y uno asíncrono. - Realizar un montaje de un contador síncrono y un contador asíncrono. - Comprobar la necesidad de utilizar un circuito que evite los “rebotes” en un pulsador mecánico. - Verificar el funcionamiento de los circuitos utilizando un analizador lógico. 2.- TAREAS PREVIAS A LA ASISTENCIA AL LABORATORIO - Lectura de la práctica. - Estudio de contadores síncronos y asíncronos. Modos de funcionamiento y señales de control. - Diseño de los montajes. - Lectura del manual de manejo del analizador lógico 3.- DESARROLLO DE LA PRÁCTICA 3.1.- Montaje del sistema y verificación Montar y comprobar el funcionamiento del contador asíncrono de 4 bits (74LS197). Utilizar como señal de reloj la salida TTL del generador de funciones. Verificar el funcionamiento del contador utilizando el analizador lógico como analizador temporal y en modo de adquisición automático (sin condición de disparo). Observar la aparición de estados transitorios en las salidas del contador. Comprobar los tiempos de propagación y compararlos con los proporcionados por el fabricante. Las señales de control y los datos de carga en paralelo se conectarán a las salidas de los microinterruptores de la placa de entrada/salida. Modificar el montaje anterior para comprobar el funcionamiento del contador síncrono reversible de 4 bits (74LS169B). Comprobar el modo de contaje ascendente y descendente. Observar las diferencias con el contador asíncrono. 3.2.- Carga en paralelo 3.2.1. Verificación Comprobar el funcionamiento de la entrada de carga en paralelo. Utilizar el analizador lógico en un modo de adquisición con una condición de disparo (trigger), estableciendo como condición de disparo que la señal de carga en paralelo (LOAD) esté a nivel bajo (0 lógico). Generar la señal de carga en paralelo mediante un cable que se conectará a masa para realizar la carga en paralelo o utilizando un microinterruptor de la placa de entrada/salida. Comprobar con el analizador lógico que la señal de carga en paralelo tiene rebotes al estar generada con elementos mecánicos. 3.2.2. Circuito antirrebotes Para eliminar los rebotes de la señal de carga en paralelo probar las 3 alternativas que se exponen a continuación: - Utilizar el pulsador (P) de la placa de entrada/salida. Esta señal está libre de rebotes ya que utiliza un circuito temporal 555 para generar un pulso de una duración aproximada Página 6.1 Laboratorio de Electrónica Digital Departamento de Tecnología Electrónica, Universidad de Vigo de 1 s (ver documentación de la tarjeta de entradas y salidas). Cada vez que se pulsa el pulsador P se genera un pulso a nivel alto, por lo que esta señal habrá que pasarla por una puerta inversora para que active la carga en paralelo del contador (activa a nivel bajo). - Utilizar el circuito antirrebotes de la figura: VCC 820 1 2 Salida 74LS14 1.8k 10u Cuando se conecta el cable a la alimentación, el condensador se carga a la tensión de +5 V y a la salida de la puerta inversora se detectará un 0 que realizará la carga en paralelo del contador. En el momento que se desconecte el cable de la alimentación y se deje al aire, el condensador empezará a descargarse por la resistencia con una constante de tiempo de 18 ms. En el momento que el valor de tensión baje del umbral de detección de un 0 en la entrada de la puerta, esta conmutará su salida a un 1 y la señal de carga en paralelo dejará de ser activa permitiendo la evolución del contador. - Eliminar los rebotes de esta señal utilizando el circuito de la figura: Página 6.2 Laboratorio de Electrónica Digital Departamento de Tecnología Electrónica, Universidad de Vigo 4.- MATERIAL PARA LA REALIZACIÓN DE LA PRÁCTICA Circuitos Integrados: Unidades 1 1 1 1 Modelo 74LS197 74LS169B 74LS14 74LS00 Descripción Contador asíncrono de 4 bits. Contador síncrono reversible de 4 bits. 6 inversores con histéresis 4 puertas NAND de 2 entradas. 5.- UBICACIÓN DE LOS CIRCUITOS INTEGRADOS EN LA PLACA 74LS00 74LS197 74LS169 74LS14 Página 6.3