Examen final junio 2010, RESUELTO

Anuncio

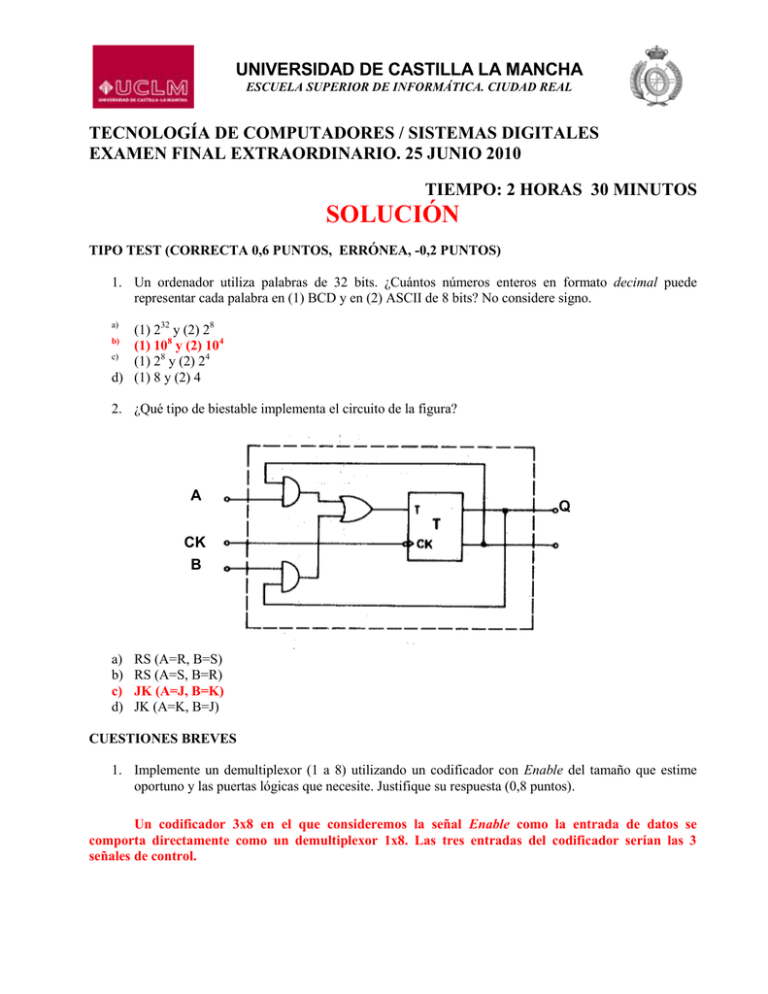

UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL TECNOLOGÍA DE COMPUTADORES / SISTEMAS DIGITALES EXAMEN FINAL EXTRAORDINARIO. 25 JUNIO 2010 TIEMPO: 2 HORAS 30 MINUTOS SOLUCIÓN TIPO TEST (CORRECTA 0,6 PUNTOS, ERRÓNEA, -0,2 PUNTOS) 1. Un ordenador utiliza palabras de 32 bits. ¿Cuántos números enteros en formato decimal puede representar cada palabra en (1) BCD y en (2) ASCII de 8 bits? No considere signo. a) (1) 232 y (2) 28 (1) 108 y (2) 104 c) (1) 28 y (2) 24 d) (1) 8 y (2) 4 b) 2. ¿Qué tipo de biestable implementa el circuito de la figura? A Q CK B a) b) c) d) RS (A=R, B=S) RS (A=S, B=R) JK (A=J, B=K) JK (A=K, B=J) CUESTIONES BREVES 1. Implemente un demultiplexor (1 a 8) utilizando un codificador con Enable del tamaño que estime oportuno y las puertas lógicas que necesite. Justifique su respuesta (0,8 puntos). Un codificador 3x8 en el que consideremos la señal Enable como la entrada de datos se comporta directamente como un demultiplexor 1x8. Las tres entradas del codificador serían las 3 señales de control. UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL 2. En la figura se representa el diagrama de bloques del sistema de encendido y apagado de un proyector de vídeo. La señal S (Start/Stop) debe poner en marcha tanto la bombilla de proyección (L) como el ventilador (V) que protege su funcionamiento. Cuando esta señal se desactiva, se apaga la luz pero el ventilador debe seguir encendido durante 2 minutos para asegurar el adecuado enfriamiento de la bombilla. Para ello se introduce el módulo temporizador, cuyo diseño está fuera del alcance de este problema, y que funciona capturando los cambios de la señal S de la siguiente forma: Si S pasa de 0 a 1, el temporizador (T) permanece inactivo. Si S pasa de 1 a 0, el temporizador (T) se activa, permaneciendo así 2 minutos, pasados los cuales se desactiva. Teniendo en cuenta el funcionamiento descrito, diseñe el bloque combinacional (L/C) utilizando el menor número de puertas lógicas. (1,0 punto). S L L/C T V Temp. S T L V 0 0 0 0 0 1 0 1 1 0 1 1 1 1 X X L=S V= S + T UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL PROBLEMA Nº 1 En un grupo de gente se analizan los grupos sanguíneos existentes para establecer la compatibilidad donante-receptor. Los resultados muestran que los grupos existentes son el O-, AB+, AB- y B-. Se debe diseñar un circuito combinacional capaz de proporcionar una salida F que indique la compatibilidad entre un donante y un receptor. Las entradas del circuito combinacional son el grupo sanguíneo del donante (que se debe codificar con 2 bits D1 y D0) y el grupo sanguíneo del receptor (que se debe codificar con 2 bits R1 y R0). Para establecer la compatibilidad se sabe que: Una persona del grupo 0- puede ser donante para un receptor de cualquier grupo, pero sólo puede ser receptor de un donante 0-. Una persona del grupo AB+ solo puede ser donante para un receptor del grupo AB+, pero puede ser receptor de un donante de cualquier grupo. Una persona del grupo AB- puede ser donante para un receptor de los grupos AB- o AB+, y puede ser receptor de un donante 0-, B- y AB-. Una persona del grupo B- puede ser donante para un receptor de los grupos B-, AB- y AB+, y puede ser receptor de un donante 0- o B-. a) Definir la codificación de los grupos sanguíneos tanto del donante como del receptor (0,4 puntos). b) Encontrar la función lógica simplificada que proporciona la salida F para establecer la compatibilidad donante-receptor mediante suma de productos (1,0 punto). c) Dibujar el circuito combinacional resultante mediante puertas lógicas (0,6 puntos). a) Grupo sanguíneo OAB+ ABB- Donante D1 D0 0 0 0 1 1 0 1 1 Receptor R1 R0 0 0 0 1 1 0 1 1 UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL b) D1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 D0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 R1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 R0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 1 1 1 1 0 1 0 0 0 1 1 0 0 1 1 1 D1 D0 00 01 11 10 1 1 1 1 0 1 0 0 0 1 1 1 0 1 0 1 R1 R0 00 01 11 10 F c) D1 D0 R1 R0 D1 R1 R0 D1 D0 R1 UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL PROBLEMA Nº 2 Se desea diseñar un circuito secuencial que controle el sintonizador de un televisor que permite ver tanto canales analógicos como digitales. El sintonizador dispone de 3 canales digitales numerados de 1 a 3, y de 3 canales analógicos, numerados también de 1 a 3. El circuito secuencial tendrá dos entradas binarias E1 y E0 que estarán normalmente a 00, salvo cuando se pulse en el mando a distancia una tecla de 1 a 3, para elegir algún canal de los 3 posibles, en cuyo caso se pondrán respectivamente a 01, 10 y 11 durante un tiempo suficiente para que la entrada le llegue al circuito secuencial diseñado. También dispondrá de tres salidas F2, F1 y F0 que funcionarán de la forma siguiente: Si F2 es 0 se le indicará al sintonizador que el canal es analógico, mientras que si F 2 es 1, se le indicará que el canal es digital. El número de canal, tanto si es analógico como si es digital, se expresará con las salidas F1 F0 en binario, siendo F1 el bit más significativo. Obsérvese que no existe el canal 0. F2 E1 E0 CIRCUITO SECUENCIAL A DISEÑAR F1 F0 SINTONIZADOR TELEVISOR El sistema se inicializará siempre con el canal 1 analógico, pero una vez en él se puede cambiar a cualquier otro canal analógico simplemente pulsando la tecla correspondiente. En caso de pulsar la tecla del mismo canal en que se está en el momento, se cambia de analógico a digital o viceversa en el mismo número de canal. Por ejemplo, si se está viendo el canal 2 digital y se pulsa la tecla 2, se pasa al canal 2 analógico. Además, ésta es la única forma de cambiar de sistema (analógico digital). Se pide: a) Diagrama de estados (0,6 puntos). b) Tabla de verdad usando los biestables indicados (1,0 punto). c) Implementación de la excitación del biestable 2 con un MUX 8x1 (0,4 puntos). d) Implementación de la excitación del biestable 1 con un DEC 4x16 (0,4 puntos). e) Implementación de la excitación del biestable 0 con puertas lógicas (0,3 puntos cada función). NOTA: Es necesario respetar los siguientes criterios: En la definición de estados, usar la siguiente notación: qnX siendo n un número de 1 a 3, ambos incluidos, que expresa el número de canal, y haciendo X=A para referirse a canales analógicos y X=D para referirse a canales digitales. Por ejemplo, el canal 2 analógico se representaría q2A. En la codificación de estados, usar el biestable más significativo Q2 para codificar si el canal es analógico o digital, con valores respectivos 0 y 1, y el resto de biestables para codificar en binario el número de canal, haciendo coincidir el número de canal con su representación binaria. Es decir, el canal 2, por ejemplo, se representaría con Q1Q0=10. UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL Tal como se desprende del enunciado, la definición y codificación de estados, no pedida, pero necesaria para realizar el problema, es: Q2 0 0 0 0 1 1 1 1 q1A q2A q3A q1D q2D q3D Q1 0 0 1 1 0 0 1 1 Q0 0 1 0 1 0 1 0 1 Significado F2 F1 F0 No usado Canal 1 analógico Canal 2 analógico Canal 3 analógico 0 0 0 0 1 1 1 0 1 1 1 1 0 1 1 1 0 0 No usado Canal 1 digital Canal 2 digital Canal 3 digital a) Diagrama de estados. Al ser un autómata de Moore, no se escribe la salida, ya que está asociada al estado, según se observa en la tabla anterior. 00 00 01 q1A 01 01 11 00 q1D 01 10 01 10 q2A 10 q3A 00 q2D 10 11 10 10 11 11 11 q3D 00 00 11 01 UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL b) TABLA PARA RESPONDER AL APARTADO B DEL PROBLEMA NÚMERO 2 ENTRADAS E1 E0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 ESTADOS ACTUALES Q2(t) Q1(t) Q0(t) 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 ESTADOS PRÓXIMOS SALIDAS Q2(t+1) Q1(t+1) Q0(t+1) F2 F1 X 0 0 0 X 1 1 1 X 1 0 0 X 0 1 1 X 0 1 0 X 1 0 1 X 0 0 1 X 1 1 0 X 0 1 1 X 0 1 1 X 0 0 0 X 0 0 0 X 1 1 1 X 1 1 1 X 1 1 1 X 1 1 1 X 1 0 1 X 1 0 1 X 1 1 1 X 1 1 1 X 0 0 0 X 0 0 0 X 1 1 1 X 1 1 1 X 0 0 0 X 1 1 1 X 1 0 0 X 0 1 1 X 0 1 0 X 1 0 1 X 0 0 1 X 1 1 0 X 0 1 1 X 0 1 1 X 0 0 0 X 0 0 0 X 1 1 1 X 1 1 1 X 1 1 1 X 1 1 1 F0 X 1 0 1 X 1 0 1 X 1 1 1 X 1 1 1 X 0 0 0 X 0 0 0 X 1 1 1 X 1 1 1 D2 X 0 0 0 X 1 1 1 X 1 0 0 X 0 1 1 X 0 1 0 X 1 0 1 X 0 0 1 X 1 1 0 EXCITACIÓN BIESTABLES T1 J0 X 0 0 0 X 0 0 0 X 0 1 1 X 0 1 1 X 1 0 0 X 1 0 0 X 1 0 0 X 1 0 0 X X 0 X X X 0 X X X 1 X X X 1 X X X 0 X X X 0 X X X 1 X X X 1 X K0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 0 X 1 X 1 X 1 X 1 X 0 X 0 X 0 X 0 UNIVERSIDAD DE CASTILLA LA MANCHA ESCUELA SUPERIOR DE INFORMÁTICA. CIUDAD REAL c) Implementación de la excitación del biestable 2 0 0 1 1 Q1 Q1 Q0 Q0 2 Q1 Q0 6 Q1 Q0 7 3 4 MUX 8x1 D2 5 2 1 0 E1 E0 Q2 d) Implementación de la excitación del biestable 1 0 0 Q1 5 1 Q2 2 E0 7 DEC 4x16 PUERTA 8 10 T1 OR 12 3 E1 14 15 e) Implementación de la excitación del biestable 0 X X X X X X X X X X X X 0 1 1 0 0 1 1 0 X X X X J0 = E0 X X X X X X X X X X X X 0 0 0 1 0 0 0 1 X X X X X X X X 0 0 0 1 0 0 0 1 K0 = E1 E0 X X X X