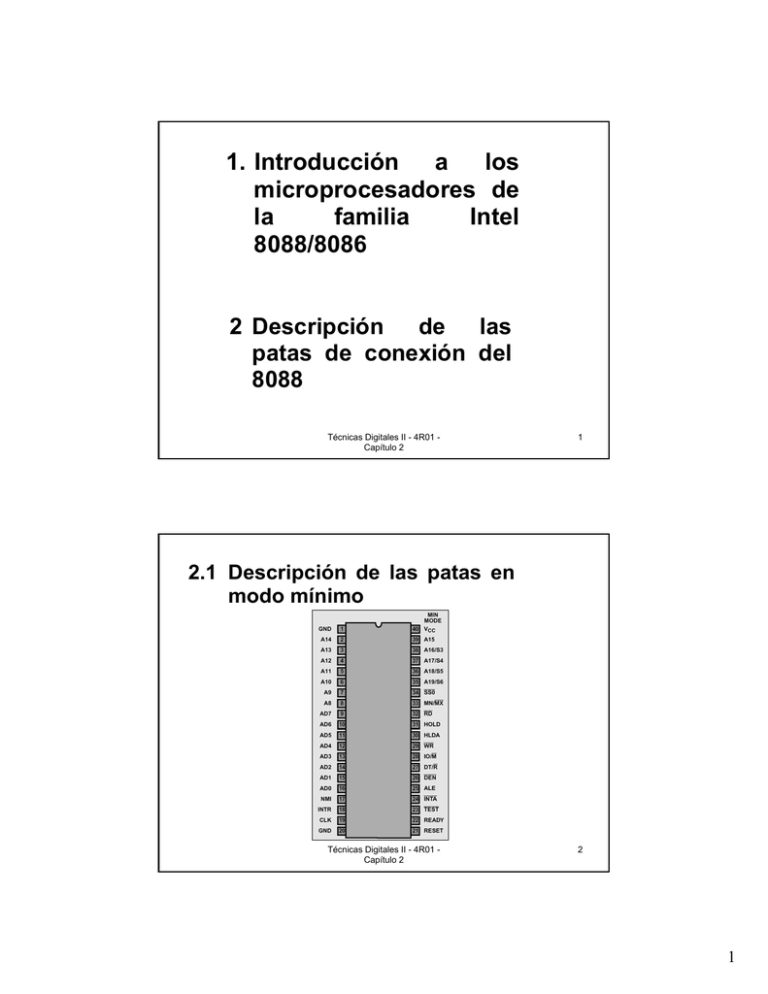

1. Introducción a los microprocesadores de la familia Intel 8088/8086

Anuncio

1. Introducción a los microprocesadores de la familia Intel 8088/8086 2 Descripción de las patas de conexión del 8088 Técnicas Digitales II - 4R01 Capítulo 2 1 2.1 Descripción de las patas en modo mínimo Técnicas Digitales II - 4R01 Capítulo 2 2 1 Conexión en modo mínimo Vcc 33 17 De lóg. control De lóg. control U3 X1 Cristal 15 MHz 16 X2 4 6 RDY1 3 RDY2 Vcc 7 AEN1 14 AEN2 1 EFI R1 15 CSYNC 13 ASYNC F/C 11 RES 5 READY 8 CLK 10 RESET 2 PCLK 12 OSC 22 19 21 18 U1 MN AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 A16/S3 A17/S4 A18/S5 A19/S6 READY CLK RESET INTR C1 8284 Power on Reset SSO 30 31 17 23 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 39 38 37 36 35 34 26 DEN 27 DT/R 28 IO/M 32 RD 29 WR 25 ALE 24 INTA HLDA HOLD NMI TEST 3 4 7 8 13 14 17 18 1 11 2 3 4 5 6 7 8 9 19 1 U2 D0 D1 D2 D3 D4 D5 D6 D7 Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 2 5 6 9 12 15 16 19 Parte baja del bus de direcciones demultiplexado OC G 74HC373 U4 A1 A2 A3 A4 A5 A6 A7 A8 B1 B2 B3 B4 B5 B6 B7 B8 18 17 16 15 14 13 12 11 Bus de datos G DIR 74HC245 Parte del bus de control 8088MIN Técnicas Digitales II - 4R01 Capítulo 2 /S2 /S1 /S0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 0 1 1 1 0 1 1 1 0 1 3 Ciclo de máquina Reconocimiento de interrupción (Ver Cap. 3) Lectura de E/S Escritura de E/S Halt Búsqueda de código de operación Lectura de Memoria Escritura de Memoria Inactivo Técnicas Digitales II - 4R01 Capítulo 2 4 2 2.6 Bus Local y Multimaster BUFFER 8088 Datos Gen. de Reloj 8284 LATCH Direcciones 8089 u 8087 8288 Control Técnicas Digitales II - 4R01 Capítulo 2 5 2.7 Multiprocesamiento 8284 8284 Lógica 8088 8086 8288 8289 8288 Lógica 8288 8289 Lógica Bus que permite conectar varias μcomputad. Memorias y Puertas comunes Técnicas Digitales II - 4R01 Capítulo 2 6 3 T1 T2 T3 T4 Clk ALE AD0-AD7 A0-7 D0-D7 A8-A15 /RD Técnicas Digitales II - 4R01 Capítulo 2 T1 T2 T3 7 T4 Clk ALE AD0-AD7 A0-7 D0-D7 A8-A15 /WR Técnicas Digitales II - 4R01 Capítulo 2 8 4 4. Arquitectura interna de un 8088 Técnicas Digitales II - 4R01 Capítulo 2 AX Registro acumulador, puede dividirse en AH y AL (8 bits cada uno). BX Registro base, puede dividirse en BH y BL. CX Registro contador, puede dividirse en CH y CL. DX Registro de datos, puede dividirse en DH y DL. SP Puntero de pila (no se puede subdividir). BP Puntero base (no se puede subdividir). SI Puntero índice fuente (no se puede subdividir). DI Puntero índice destino (no se puede subdividir). Técnicas Digitales II - 4R01 Capítulo 2 9 10 5 Registro Operación AX Multiplicación y división de palabras. E/S de 16 bits AL Multiplicación y división de bytes. E/S de 8 bits. XLAT. Aritmética decimal. AH Multiplicación y división de bytes BX Puntero. Base de XLAT. CX Operaciones de cadenas (strings). Lazos. CL Desplazamiento de variables. Rotaciones DX Multiplicación y división de Direccionamiento indirecto de E/S. palabras. Técnicas Digitales II - 4R01 Capítulo 2 11 Técnicas Digitales II - 4R01 Capítulo 2 12 6 S15 S0 O0 O15 A19 A0 Técnicas Digitales II - 4R01 Capítulo 2 13 Técnicas Digitales II - 4R01 Capítulo 2 14 7 Técnicas Digitales II - 4R01 Capítulo 2 15 5. Reset y Mapeo de Memoria U1 17 16 C2 Vcc R1 33 U6 C1 4 6 3 7 14 1 15 13 11 X1 READY CLK RESET X2 PCLK RDY1 RDY2 AEN1 AEN2 EFI CSYNC ASYNC F/C OSC 5 8 10 22 19 21 2 18 MN READY CLK RESET INTR 12 RES 8284 S1 C3 AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 A16/S3 A17/S4 A18/S5 A19/S6 SSO 30 31 17 23 DEN DT/R IO/M HLDA HOLD NMI TEST RD WR ALE INTA 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 39 38 37 36 35 34 26 27 28 32 29 25 24 U4 1 2 3 A B C Vcc 6 4 5 G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 /CS0 /CS1 /CS Programa 74HC138 8088MIN Técnicas Digitales II - 4R01 Capítulo 2 16 8 6. Manejo de entradas y salidas U1 33 22 19 21 18 MN READY CLK RESET INTR AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7 A8 A9 A10 A11 A12 A13 A14 A15 A16/S3 A17/S4 A18/S5 A19/S6 SSO 30 31 17 23 DEN DT/R IO/M HLDA HOLD NMI TEST RD WR ALE INTA 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 39 38 37 36 35 34 26 27 28 U4 1 2 3 6 4 5 A B C G1 G2A G2B Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 15 14 13 12 11 10 9 7 /CS0 /CS1 /CS2 /CS3 74HC138 32 29 25 24 8088MIN Técnicas Digitales II - 4R01 Capítulo 2 17 7. Modos de direccionamiento del 8086/8088 Registro indirecto: 1.- [BX] 2.- [DI]. 3.- [SI]. Esto debe leerse como que BX, DI o SI apuntan a memoria. Basado: 4.- desp8[BX] ; BX apunta a memoria con un desplazamiento de 8 bits 5.- desp8[BP] ; BP apunta a memoria con un desplazamiento de 8 bits 6.- desp16[BX] ; Idem 16 bits 7.- desp16[BP] Técnicas Digitales II - 4R01 Capítulo 2 18 9 7. Modos de direccionamiento del 8086/8088 Indexado: 8.- desp8[SI] 9.- desp8[DI] 10.- desp16[SI] 11.- desp16[DI]. Basado-indexado: 12.- [BX+SI] ; Dirección apuntada por la suma de BX + SI (sin afectar a ninguno de los dos). 13.- [BX+DI] 14.- [BP+SI] 15.- [BP+DI]. Técnicas Digitales II - 4R01 Capítulo 2 19 7. Modos de direccionamiento del 8086/8088 Basado-indexado con desplazamiento: 16.- desp8[BX+SI] ; Dirección de memoria apuntada por la suma de BX + SI con un desplazamiento de 8 bits. 17.- desp8[BX+DI] 18.- desp8[BP+SI] 19.- desp8[BP+DI] 20.- desp16[BX+SI] ; Idem con desplazamiento de 16 bits 21.- desp16[BX+DI] 22.- desp16[BP+SI] 23.- desp16[BP+DI]. Directo: 24.- [desp16]. Técnicas Digitales II - 4R01 Capítulo 2 20 10 Técnicas Digitales II - 4R01 Capítulo 2 21 8. Repertorio de Instrucción Nemónico Significado Formato Operación Flags Afect. MOV Movimiento MOV D,F (F) → (D) Ninguno Destino Fuente Memoria Acumulador Acumulador Memoria Registro Registro Registro Memoria Memoria Registro Registro Inmediato Memoria Inmediato Registro Segm. Reg. 16 bits Registro Segm. Mem. 16 bits Reg 16 bits Registro Segm. Mem 16 bits Registro Segm. Técnicas Digitales II - 4R01 Capítulo 2 22 11 Nemónico IN OUT Significado Entrada Salida MOV DX,789AH IN AL,DX IN AX,DX OUT 60H,AL OUT 60H,AX Formato IN An,F OUT D,An ; ; ; ; ; ; ; ; ; ; ; ; Operación (F) → (An) (An) → (D) Flags Afect. Ninguno Ninguno Se inicializa DX para apuntar a 789AH Se lleva al registro AL el contenido de la puerta 789AH Se lleva a AL el contenido de la puerta 789AH y a AH el de la puerta 789BH. DX no se altera. Se enviará a la puerta 60H el contenido de AL. Se sacará por la puerta 60H el contenido de AL y por la 61H el de AH. Técnicas Digitales II - 4R01 Capítulo 2 23 Nemónico Significado Formato Operación Flags Afect. XCHG Intercambio XCHG D,F (F) ↔ (D) Ninguno Destino Fuente Acumulador Reg. 16 Memoria Registro Registro Registro Registro Memoria Técnicas Digitales II - 4R01 Capítulo 2 24 12 Nemónico Significado Formato Operación Flags Afect XLAT Traducción XLAT (DS:(AL)+(BX)) → (AL) Ninguno Byte de la tabla Contenido de la tabla 00 Equivalente ASCII del EBCDIC 00 01 Idem del EBCDIC 01 02 Idem del EBCDIC 02 .... .... FE Idem del EBCDIC FE FF Idem del EBCDIC FF Técnicas Digitales II - 4R01 Capítulo 2 25 Cadenas • LODS: Cargar elemento de cadena en AL e incrementa SI XOR XOR MOV MOV BX,BX AH,AH CX,10 SI,1234H LACITO: LODSB ADD BX,AX LOOP LACITO Técnicas Digitales II - 4R01 Capítulo 2 26 13 Cadenas • STOS: Cargar elemento AL en cadena e incrementa SI MOV AL,0 MOV CX,10 MOV SI,1234H LACITO: STOSB LOOP LACITO Técnicas Digitales II - 4R01 Capítulo 2 27 Cadenas • MOVS: Mueve un byte o word desde DS:SI a ES:DI y SI++, DI++ (ó SI--, DI--) MOV MOV MOV MOV MOV MOV REP DX,1000H DS,DX ES,DX DI,2345H SI,1234H CX,100 MOVSB Técnicas Digitales II - 4R01 Capítulo 2 28 14 Cadenas • SCAS: Busca en una cadena ES:DI, el contenido de AL MOV MOV MOV REPNE JE ….. AL,23H DI,1234H CX,100 SCASB ENCONTRADO ENCONTRADO: Técnicas Digitales II - 4R01 Capítulo 2 29 Cadenas • CMPS: Compara dos cadenas ES:DI CON DS:SI e incrementa los punteros MOV MOV MOV REPE JE ….. DI,1234H SI,6789H CX,100 CMPSW ENCONTRADO ENCONTRADO: Técnicas Digitales II - 4R01 Capítulo 2 30 15 Cadenas • STOS: Cargar elemento AL en cadena e incrementa SI MOV AL,0 MOV CX,10 MOV SI,1234H LACITO: STOSB LOOP LACITO Técnicas Digitales II - 4R01 Capítulo 2 31 Cadenas • MOVS: Mueve un byte o word desde DS:SI a ES:DI y SI++, DI++ MOV MOV MOV MOV MOV MOV REP DX,1000H DS,DX ES,DX DI,2345H SI,1234H CX,100 MOVSB Técnicas Digitales II - 4R01 Capítulo 2 32 16 ADD ADC INC AAA DAA Suma Suma de byte o palabra Suma de byte o palabra con el estado del acarreo anterior Incrementar en 1 byte o palabra Ajuste ASCII de la suma. Ajuste decimal de la suma Sustracción SUB Resta de byte o palabra. SBB Resta de byte o palabra con el préstamo de la operación anterior. DEC Decrementar en 1 un byte o palabra. NEG Complementar byte o palabra. AAS Ajuste ASCII de la resta. DAS Ajuste decimal de la resta. Técnicas Digitales II - 4R01 Capítulo 2 MUL IMUL AAM 33 Multiplicación Producto de bytes o palabras no signadas. Producto de bytes o palabras enteras. Ajuste ASCII del producto. División DIV Cociente de bytes o palabras no signadas. IDIV Cociente de bytes o palabras enteras. AAD Ajuste ASCII del cociente. CBW Convierte byte a palabra. CWD Convierte palabra a doble palabra. Técnicas Digitales II - 4R01 Capítulo 2 34 17 Nemónico Significado Formato ADD Suma ADD D,F ADD Suma ADD D,F Operación (F)+ (D) → (D) Flags afectados AF, CF, OF, SF, ZF, PF Carry → (CF) (F)+(D)+ (CF) → AF, CF, OF, SF, ZF, PF (D) Carry → (CF) Incrementar en 1 Ajuste suma la AAA AF, CF, OF, SF, ZF, PF DAA Ajuste decimal de la DAA suma AF, CF, OF, SF, ZF, PF ASCII INC D (D) + 1 → (D) INC AAA de Técnicas Digitales II - 4R01 Capítulo 2 Destino Registro Registro Memoria Registro Memoria Acumulador OF, SF, ZF, AF, PF 35 Fuente Registro Memoria Registro Inmediato Inmediato Inmediato Destino Reg 16 Reg 8 Memoria Técnicas Digitales II - 4R01 Capítulo 2 36 18 Nemónico Significado MUL Producto (no signado) DIV Cociente (no signado) IMUL IDIV AAM AAD CBW CWD Formato Operación MUL F (AL)*(F8)→(AX) 1.DIV F ((AX)/(F8))→ (AL) Si vale 0FFH, se generará una interrupción de división por 0. (Ver Cap. 3). Resto → (AH). 2.((DX,AX)/(F16))→(AX) Si vale 0FFFFH, se generará una interrupción de división por 0. Ver Cap. 3. Resto → (DX) Producto entero (signado) IMUL F (AL)*(F8)→(AX) 1.Cociente entero (signado) IDIV F ((AX)/(F8))→ (AL) Resto → (AH). 2.((DX,AX)/(F16))→(AX) Si es positiva y > 7FFFH o si es negativo y < 8001H, se generará una interrupción de división por 0. Resto → (DX) Ajuste de AL para el AAM ((AL)/10)) → (AH) producto. Resto ((AL)/10) → (AL) Ajuste de AX para el AAD (AH)*10) + (AL) → (AL) cociente. 00 → (AH) Convertir byte a palabra CBW El bit más significativo de AL se repite en todo AH Convertir palabra a doble CWD El bit más significativo de palabra (32 bits) AX se repite en todo DX Técnicas Digitales II - 4R01 Capítulo 2 Flags afectados AF, CF, OF, SF, ZF, PF AF, CF, OF, SF, ZF, PF AF, CF, OF, SF, ZF, PF AF, CF, OF, SF, ZF, PF OF, SF, ZF, AF, PF OF, SF, ZF, AF, PF Ninguno Ninguno 37 Registro 8 bits Registro 16 bits Memoria 8 bits Memoria 16 bits Técnicas Digitales II - 4R01 Capítulo 2 38 19 Nemónico Significado AND AND lógica Formato Operación AND D,F (F).(D) → (D) OR OR inclusiva lógica OR D,F (F) + (D) → (D) XOR OR exclusiva lógica XOR D,F (F) ⊕ (D) → (D) NOT NOT lógica NOT D (/D) → (D) Destino Registro Registro Memoria Registro Memoria Acumulador Flags afectados CF, OF, SF, ZF, PF AF indefinido CF, OF, SF, ZF, PF AF indefinido CF, OF, SF, ZF, PF AF indefinido Ninguno Fuente Registro Memoria Registro Inmediato Inmediato Inmediato Destino Registro Memoria Técnicas Digitales II - 4R01 Capítulo 2 Nemónico JMP Significado Salto incondicional Formato JMP operando Operación Salto a la dirección indicada en Operando. 39 Flags afectados Ninguno Fuente Short Near Far Puntero en memoria 16 bits Puntero Registro 16 bits Puntero en memoria 32 bits Nemónico Significado Jcc Salto condicional Formato Operación Flags afectados Ninguno Jcc Salto a la dirección operando indicada en Operando si se verifica el estado de los flags del código de condición.. Técnicas Digitales II - 4R01 Capítulo 2 40 20 Nemónico JA JAE JB JBE JC JCXZ JE JG JGE JL JLE JNA JNAE JNB JNBE JNC JNE JNG JNGE JNL JNLE JNO JNP JNS JNZ JO JP JPE JPO JS JZ Significado above (por encima) NO signado. above or equal (encima o igual) below (por debajo) below or equal acarreo registro CX=0 igual mayor o greater (signado) mayor o igual menor o less (signado) menor o igual not above not above or equal not below not below nor equal not carry not equal not greater not greater or equal not less not less or equal not overflow not parity not sign (no negativo) not zero overflow parity parity even (par) parity odd (impar) sign (positivo) zero Condición CF=0, ZF=0 CF=0 CF=1 CF=1 ó ZF=1 CF=1 (CF ó ZF) = 0 ZF=1 ZF=0 y SF=OF (overflow) SF=OF (SF ⊕ OF)=1 ((SF ⊕ OF)=1)+ZF)=1 CF=1 ó ZF=1 CF=1 CF=0 CF=0 y ZF=0 CF=0 ZF=0 ((SF ⊕ OF)=1)+ZF)=1 (SF ⊕ OF)=1 SF=OF ZF=0 y SF=OF OF=0 PF=0 SF=0 ZF=0 OF=1 P=1 PF=1 PF=0 SF=1 ZF=1 Técnicas Digitales II - 4R01 Capítulo 2 41 80186/80188 Generador de Reloj Incorporado Modos de bajo consumo 2 Canales de DMA 3 Temporizadores de 16 bits Lógica de selección de Memoria y E/S Refresco de Memoria Dinámica incorporado Generador de Wait States incorporado Controlador de bus local incorporado Técnicas Digitales II - 4R01 Capítulo 2 42 21 Técnicas Digitales II - 4R01 Capítulo 2 43 Técnicas Digitales II - 4R01 Capítulo 2 44 22