material

Anuncio

Arquitecturas Paralelas

Carlos Figueira

Última actualización: Diciembre 1996

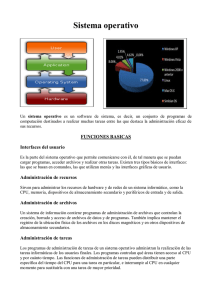

Contents

1 Generalidades sobre Paralelismo

1.1 Aplicaciones del paralelismo . . . . . . . . . . . . . . . .

1.2 Supercomputación en Venezuela . . . . . . . . . . . . . .

1.3 Mecanismos paa lograr mayor desempeño a nivel de HW

1.4 Taxonomı́a sencilla de computadoras . . . . . . . . . . .

1.5 Observaciones sobre diseños de nuevas máquinas . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4

4

4

5

5

5

2 Introducción

2.1 Desempeño: latencia y ancho de banda . . . . . . . . . . . . . . . . . . . . . . . . .

2.2 Ley de Amdahl . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.3 ¿Cómo medimos el desempeño de un computador para poder compararlo con otro?

2.4 Programas para medir desempeño . . . . . . . . . . . . . . . . . . . . . . . . . . .

2.5 Otros errores y/o suposiciones incorrectas comunes en la medida de desempeño . .

2.6 Bibliografı́a . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

7

7

7

8

9

10

11

3 Pipelining y máquinas vectoriales

3.1 Factores que limitan speedup ideal de un pipeline

3.2 Complicaciones adicionales en manejo de pipeline

3.3 Más velocidad aún . . . . . . . . . . . . . . . . .

3.4 Falacias . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

12

12

15

15

16

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

4 Máquinas vectoriales

4.1 Arquitecturas vectoriales . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 ¿ Cómo guardar matrices en un banco de mem. intercaladas de forma

y por columna sea lo más rápido posible? . . . . . . . . . . . . . . . .

4.3 ¿Qué otros tipos de accesos se utilizan? . . . . . . . . . . . . . . . . .

4.4 Arquitecturas basadas en reg. vect . . . . . . . . . . . . . . . . . . . .

4.5 Mejoras a máquinas vect. . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Métricas adicionales para medir desempeño de maqs vect. . . . . . . .

4.7 Trampas y falacias . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

. . . .

que el

. . . .

. . . .

. . . .

. . . .

. . . .

. . . .

. . . . . . . . .

acceso por fila

. . . . . . . . .

. . . . . . . . .

. . . . . . . . .

. . . . . . . . .

. . . . . . . . .

. . . . . . . . .

5 Sub-sistema de memoria

5.1 Cache . . . . . . . . . . . . . . . . . . .

5.2 Organización de un cache . . . . . . . .

5.3 Polı́ticas a definir para manejo de cache

5.4 Problemas abiertos . . . . . . . . . . . .

5.5 Efecto de las fallas . . . . . . . . . . . .

5.6 Cache en arq. vectoriales . . . . . . . .

5.7 Polı́ticas de actualización de mem. ppal

5.8 Cache y E/S . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

1

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

17

17

18

18

19

19

20

21

22

22

22

23

23

23

23

24

24

6 CASO MAQUINA VECTORIAL: CRAY

6.1 CRAY Y-MP C90 . . . . . . . . . . . . . . . . . . . . . .

6.1.1 Generalidades . . . . . . . . . . . . . . . . . . . . .

6.1.2 Pipelining and segmentation . . . . . . . . . . . .

6.1.3 Sección de comunicación inter-procesadores (ICS) .

6.1.4 Sección de cómputo del CPU . . . . . . . . . . . .

6.2 Sección de control del CPU . . . . . . . . . . . . . . . . .

6.3 Procesamiento paralelo . . . . . . . . . . . . . . . . . . . .

6.3.1 Memoria . . . . . . . . . . . . . . . . . . . . . . . .

6.3.2 I/O . . . . . . . . . . . . . . . . . . . . . . . . . .

6.4 Programación . . . . . . . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

26

26

26

26

26

26

27

27

27

27

28

7 Cray Y-MP E

28

7.1 Generalidades . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7.1.1 Diferencias con C90 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

8 CRAY-1

28

8.1 CRAY-2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.2 CRAY-3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8.3 CRAY X-MP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

9 Introducción a MIMD

9.1 Definición y objetivos . . . . . .

9.2 Modelos de desempeño . . . . . .

9.3 Granularidad . . . . . . . . . . .

9.4 Conclusiones sobre el desempeño

9.5 Taxonomı́a de MIMD . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

30

30

30

31

31

32

10 Redes de Interconexión

10.0.1 Introducción . . . . . . . . . . . .

10.1 Buses . . . . . . . . . . . . . . . . . . . .

10.2 Conmutadores de barras cruzadas o x-bar

10.3 Redes Multi-etapas . . . . . . . . . . . . .

10.3.1 Red de Clos . . . . . . . . . . . . .

10.3.2 Red de Benes̆ . . . . . . . . . . . .

10.3.3 Redes Banyan . . . . . . . . . . . .

10.3.4 Desempeño y ancho de banda . . .

10.3.5 Conclusión redes multi-etapas . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

34

34

34

35

36

37

37

37

37

37

11 MIMD Memoria Compartida

11.1 Técnicas de sincronización .

11.1.1 Test and Set . . . .

11.1.2 Incr y decr. . . . . .

11.1.3 Compare and Swap .

11.1.4 Fetch and Add . . .

11.2 Barreras . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

38

38

38

39

39

39

40

12 MIMD Memoria Distribuida

12.1 La comunicación . . . . . .

12.2 Enrutamiento . . . . . . . .

12.3 Topologı́as fijas . . . . . . .

12.3.1 Topologı́as comunes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

41

41

42

44

44

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

13 MIMD: Esquemas Hı́bridos

13.1 Motivación . . . . . . . . . . . . . . . . . . . .

13.2 Implementación de coherencia dinámica . . . .

13.3 Sistemas basados en directorios . . . . . . . . .

13.3.1 Directorios centralizados vs distribuidos

13.4 Latencia en accesos remotos . . . . . . . . . . .

13.4.1 Modelos de consistencia relajados . . . .

13.4.2 Prefetching . . . . . . . . . . . . . . . .

13.4.3 Multithreading . . . . . . . . . . . . . .

13.5 Problemas de la asincronı́a . . . . . . . . . . . .

13.6 Soporte para Sistemas Operativos . . . . . . . .

13.7 Casos . . . . . . . . . . . . . . . . . . . . . . .

13.7.1 DASH . . . . . . . . . . . . . . . . . . .

13.7.2 Alewife . . . . . . . . . . . . . . . . . .

13.7.3 KSR-1 . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

46

46

47

48

48

49

49

49

50

50

50

51

51

51

52

14 Subsistema de Entrada/Salida:

14.1 Esquema tı́pico de dispositivos de E/S . .

14.1.1 Caracterización de la carga de E/S

14.2 Benchmarks en el mundo de E/S . . . . .

14.2.1 Aplicaciones . . . . . . . . . . . . .

14.2.2 Sintéticos . . . . . . . . . . . . . .

14.3 Discos . . . . . . . . . . . . . . . . . . . .

14.4 Arreglo o baterı́a de discos . . . . . . . . .

14.4.1 Niveles de RAID . . . . . . . . . .

14.4.2 Comparación de niveles de RAID .

14.5 Caso MIMD: iPSC/2 . . . . . . . . . . . .

14.6 Otros casos . . . . . . . . . . . . . . . . .

14.6.1 CM-2 . . . . . . . . . . . . . . . .

14.6.2 CRAY Y-MP C90 . . . . . . . . .

14.7 Misceláneas . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

53

53

53

55

55

56

56

56

56

57

57

57

57

57

58

15 Máquinas SIMD

15.1 Arreglos de Procesadores

15.2 Experiencias en SIMD . .

15.3 Caso: el CM-2 . . . . . .

15.3.1 Procesador . . . .

15.3.2 Comunicaciones . .

15.3.3 I/O . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

59

59

60

60

60

61

61

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

1

Generalidades sobre Paralelismo

archivo: general.tex

[1 clase]

Contenido

Aplicaciones del paralelismo — Grandes desafı́os — Supercomputación en Venezuela — Mecanismos para

lograr mayor desempeño a nivel de harware — Taxonomı́a elemental de computadores — Observaciones

sobre diseños de nuevas máquinas

1.1

Aplicaciones del paralelismo

¿ Qué pbs. se corren en para.?

¿ Cómo se mejora el desempeño en Supercomputadoras?

• Laboratorios virtuales ( 3er paradigma de ciencia, junto a exper. y teorı́a)

• Manufactura: robótica, control de sistemas, diseño de plantas

• Economı́a: modelos socio-económicos

• Medicina: Procesos bioquı́micos, diseño de medicamentos y fármacos, investigación genética, diseño de

prótesis y herramientas para colocarlas

• Quı́mica computacional: diseño de catalizadores, membrana, nuevos materiales

• Ingenierı́a

–

–

–

–

Diseño de automóviles (choques), aviones

Análisis de estructuras

Seguridad de plantas nucleares

Modelaje de redes de transmisión de electricidad

Grandes desafı́os en supercomputación.

1.2

Supercomputación en Venezuela

La industria petrolera

Algunas aplicaciones iniciales no eran de interés en Vzla, e.g.: licitaciones para pozos. Pero en cambio:

Exploración

• 2 millones de LOC en Geofı́sica,INTEVEP.

• Procesamiento de imágenes sı́smicas (2D vs. 3D) 3D influye en flujo de caja al recuperar grandes

volúmenes más rápido (es decir, primero el más grande, p.e.)

Recuperación Pozos estructurales vs. reactores termoquı́micos / Modelos de percolación (autámatas celulares) / Modelaje de yacimientos (grids heterogéneos) (30.000 lı́neas - black oil sim.) / Petroquı́mica

y derivados (quı́mica computacional).

Refinación El modelo SIMPAR (modelo de área) / Modelos son realmente lineales? Los ceros ...

Otras industrias CVG / Electricidad — Edelca (powergrid ...) / Banca (sist. dist. de alta disponibilidad.

Modelo de inversión y carteras de activos)

1.3

Mecanismos paa lograr mayor desempeño a nivel de HW

Varios procesadores:

Conexión ¿C?ómo conectarlos entre sı́?

Memoria Esquema de memoria compartida / Distribuı́da / Hı́brido

I/O ¿ Cómo se accesa ?

Multiplicidad de unidades funcionando en cada CPU

• varias ULAS

• varios sumadores, mult., etc., independientes (superscalar) => uso de marcadores (scoreboards) para

llevar cuenta de registros y unidades funcionales requeridas

• unidades “paralelas” (sumador par. en vez de bit-serial, comp. paralelo, etc) esto no lo veremos

• segmentación encauzada en CPU

Ciclos más cortos para instrucciones más frecuentes (RISC, también op. más comunes tienen long.

más corta)

Solapamiento de op. CPU y E/S (E/S ind.): Controladores de E/S. DMA

Uso de jerarquı́a de memoria Registros — Cache — Mem ppal — mem sec.

El CPU suele ser 1000 veces más rápido que mem ppal.

Problemas tı́picos de jerarquı́a

• Cómo tener la inf. requerida en CACHE

• Coherencia/actualización de CACHE y mem. ppal

1.4

Taxonomı́a sencilla de computadoras

Flynn: SISD, SIMD, MISD (?), MIMD (SM/DM). (Pb: Vectorial?)

En qué nos concentraremos durante el curso: Paralelismo peq., moderado y masivo

La Ley de Amdahl vs. paralelismo masivo: los resultados de Gustafson

1.5

Observaciones sobre diseños de nuevas máquinas

o ¿Cómo puede fracasar una máquina antes de salir?

Un nuevo diseño debe tomar en cuenta:

Funcionalidad requerida

• soporte SO: UNIX, tam. de mem, manejo de mem. virtual, cambio de contexto

• soporte lenguaje

• pto flotante

• someterse a estandares: pto flotante (IEEE,DEC,IBM), I/O bus (VME,SCSI,Futurebus), Redes

– Ethernet

Costo

Tiempo de diseño diseños complejos tardan más

Sobrevivir tendencias

• hardware: capa. de DRAM: multiplica por 4 c/ 3 años. Chips de 4MB

• de softw.: req. de memoria crece de 1.5 a 2 por año => bits de direccionamiento se consumen a

0.5 a 1 bit anual (razón de abandono de muchas arq.), mejoras de compiladores

• mejoras en áreas:

Supercomp. mejoran 19% por año

Mainframes 16%

Mini

20 %

Micro

26 %

Ejemplo planifica para una compañı́a y un fabricante le ofrece una nueva máquina que será 2x más rápida

que las máq. de hoy, pero que saldrá en 3 años.

Si es un micro, en 3 años la ind. tendrá 1.263 ≈ 2. Conclusión: no es ninguna ganga.

2

Introducción

archivo: int.tex

[2 clases aprox.]

Contenido

¿Qué es paralelismo? — ¿Por qué paralelismo? — Paralelismo vs. Sist. Distribuidos — Tipos de paralelismo (resp. al número de proc.) — Orientación del curso — Cursos paralelismo USB — Niveles de

aprovechamiento de máquinas paralelas

Desempeño: latencia y ancho de banda — Ley de Amdahl — Medidas de desempeño: MIPS, MFlops —

Falacias — Benchmarks — Bibliografı́a

Mejoras Para mayor motivación, incorporar info sobre limitación inherente del secuencial: lentitud de

evolución (curva de aumento del reloj de 25% por año, ley de Moore sobre avances de 60% anual en la

densidad de chips). Estudiar los artı́culos de Gordon Bell en ACM del 89 [Bel89] y del 92 [Bel92] sobre

futuro de la supercomputación, y [SC91] sobre arquitectura en general.

2.1

Desempeño: latencia y ancho de banda

Recordar objetivos:

• Maximizar desempeño en una máquina

• Decidir entre dos arquitecturas

• Diseño de arquitecturas de mayor desempeño

¿Qué es el desempeño (performance)?

• Visión del programador: tiempo de respuesta/tiempo de ejecución/latencia

• Visión de un director de centro: cantidad de trabajos por hora/throughput/ancho de banda (BW)

Ejemplo: ¿Cuáles de las siguientes mejoras se reflejan en la latencia, ancho de banda o ambos (resp. a

sist. monoprocesador)?

Reloj más rápido: Ambos

1 Procesador por tarea: sólo BW

Procesamiento en par. de programs cientı́ficos: Ambos

BW y latencia no son completamente indptes.. Por ejemplo, un PIPELINE a nivel de tareas mejora BW

pero no latencia. Generalmente empeora. Nos concentraremos en latencia.

2.2

Ley de Amdahl

Principio de diseño para mejorar desempeño: acelerar el caso común (operaciones más frec.) Para cuantificar

esto, usaremos la Ley de Amdahl (1966 o 67):

Speedup

=

T. de ejec. sin usar aceleramiento

T. de ejec. acelerado

Ejemplo 1 Que mejora se obtiene si incorporamos un mecanismo que permite correr 10 veces más rapidamente, pero sólo se puede usar la mitad del tiempo:

Speedup =

Ttotal

1

=

Ttotal

0.5 +

+ 2×10

Ttotal

2

0.5

10

≈ 1.8

Ejemplo 2 Se mejora velocida del CPU 5x sin afectar tiempo de I/O, pero cuesta 5x. El CPU se usa

sólo 50% del tiempo (el resto espera por I/O). El costo del CPU es 30% del costo del sistema. Basado en

costo/beneficio ¿vale la pena la mejora?

Speedup= 0.5+1 0.5 =1.67

5

Costo nueva maq.=( 31 × 5) + 23 =2.33 × Costo vieja maq.

El costo aumenta más rapidamente que el speedup: no vale la pena!

2.3

¿Cómo medimos el desempeño de un computador para poder compararlo

con otro?

Preguntar

MIPS

pico: poco representativo. Toma la más rápida!

sostenido: en qué programa?

Contraejemplo: RISC vs. CISC. Se pierde la noción de tiempo total de ejecución.

Ejemplo de falacia del MIPS: Supongamos una arq. load/store, cuya mezcla de instr. en una carga

representativa viene dada por:

Instr.

Frecuencia No. de ciclos que tarda

Load

20%

2

Opr. ULA

40%

1

Store

12%

2

Branch

28%

2

Se construye un compilador optimizante que logra reducir las inst. ULA en 50%. Con un reloj de 20 ns.,

compare los MIPS del código no optimizado con los del optimizado.

El tiempo que tarda una instrucción promedio en ciclos por reloj (CPI) es

X

CP I =

f reci × ciclos/instri

i:Instruc

M IP S

=

ciclos/seg

CP I × 106

50M Hz

M IP Sviejo = (0.2∗2+0.4∗1+0.12∗2+0.28∗2)∗10

=50/16=31.25

6

50M Hz

M IP Snuevo = (2/8∗2+2/8∗1+1.2/8∗2+2.8/8∗2)∗106 =50/16=28.57

La compilación optimizante empeora el desempeño ? Dónde está el error?

Resp: El nuevo ejecuta menos instrucciones.

El tiempo CPU viejo es (No. Inst viejo)/(MIPS viejo 106 ) = 32 (No. Inst viejo) ns El tiempo CPU nuevo

es (0.8)(No. Inst viejo)/(MIPS nuevo 106 ) = 28 (No. Inst viejo) ns

Los fabricantes suelen publicar los MIPS de la siguiente manera:

• MIPS sin derivación Meaningless Indicator of Processor Speed.

• MIPS nativo (como el calculado antes): es necesrio completar con el nombre del programa usado, del

# de instr. ensamblador por # de instr. lenguaje “standard” (e.g. C).

• MIPS pico

• MIPS relativo, por ejemplo, VAX MIPS, relativo a la VAX 11/780. Para que tenga sentido habrı́a que

especificar con qué programa se hizo la medición, qué versiones de compilador y sistema, etc.

MFlops = (# de flops en un programa)/(Tiempo de ejecución * 106 )

Mide operaciones flotantes, no instrucciones . Intenta independizarse del problema del # de ciclos

por instrucción. Solo tiene sentido para programas instensivos en cálculo pto. flotante, sino absurdo (ej:

compiladores).

Inconvenientes:

√

• Diverso set de operaciones. CRAY-2 no tiene div, mientras que 68882 tiene div y .

• Heterogeneidad en tiempo de ejecución, por ejemplo, entre + y *. Una solución propuesta es normalizarlas (Normalized vs. native MFlops).

Peso propuesto

ADD,SUB,COMPARE,MULT

1

√

DIVIDE,

4

EXP,SIN

8

Ej: DEC 3100 corriendo SPICE. Nativo = 1.2 / Normalized = 1.7

Conclusión:

usar?

2.4

la medición de desempeño depende del programa ejecutado. La pregunta es qué programa

Programas para medir desempeño

Mi carga promedio (my program mix): es lo ideal pero es poco realista, puesto que:

• ¿cómo (y quién) corre el programa en todas las máqs disponibles?

• ¿quién entona el programa? ¿cuánto se entona?

Programa real representativo

que cumpla con las siguientes caracterı́sticas:

• Escrito en lenguaje de alto nivel (portable)

• Representativo de algún estilo de prog. o carga (eg: prog. numérica)

• medición es fácil

• amplia distribución

Propuestos a nivel de supercomputación por un grupo de universidades y compañı́as: Perfect Club. Es

un conjunto abierto de programas/algoritmos.

A nivel general: SPEC (Systems Performance Evaluation Cooperative Effort), propuesto por un grupo

que incluye practicamente todas las compañı́as importantes (IBM,ATT, SUN, DEC, etc). SPEC es un

conjunto de 10 programas de amplia difusión: GNU C, Circuit simulator, Monte Carlo sim., LISP interpreter,

Numerical kernels, etc.

Kernels: Son pequeños pedazos de programas muy utilizados que han sido extraı́dos para medir desempeño. Ejemplos son los “Livermore Loops” (24 lazos internos de comp. num. en fı́sica) y “Linpack”.

Linpack es un paquete de programas para álgebra lineal, el cuál suele utilizar BLAS (Basic Linear

Algebra Subrotines). Las subrutinas de BLAS operan sobre arreglos unidimensionales y están escritas

en ensamblador1 de cada máquina para max. perf. Existen varias versiones: simple y doble precisión,

rolled/unrolled loops (para maq. vect. rolled es mejor!).

Los inconvenientes de LINPACK son: no tiene div, no usa func. mat (sin,cos, etc), casi todo el tiempo

en una función (saxpy)2 , y baja localidad de datos.

Tpoy benchmarks No son nada representativos! Ej: criba de Erastótenes, Puzzle, Quicksort. Además

adolecen de una serie de fallas:

• 33% inst. ejecutadas son asig. de const.

• 5% asig. con result. de una expr.

• no hay “while”

• 50% son eval. control de lazos

• Solo trabaja enteros

• 58% variables son locales

• Son tan pequeños que la rata de hit de datso/inst es practicamente 100%.

Sintéticos: Tratan de combinar en un programa una mezcla de instrucciones que se considera “representativa”. Ej: Whetstones (en 1976-Algol 60, hoy en FORTRAN y PASCAL), tomado por estadı́sticas en un

centro de cómputo. Peculiaridades: alto porc. de flotantes, 50% del tiempo ejecuta librerı́as mat., pocas

variables locales (si se asignan var. glob a reg.— lo cual es muy raro —, el perf explota), alta local. de inst.

Otro ejemplo: Dhrystones. Condsidera explic. pbs de loclaidad, caece de operacioens flotantes, hasta

40% en func. sobre strings, si se usa versión anterior a 2.1, un eliminador de “dead code” puede descartar

hasta 25%!

2.5

Otros errores y/o suposiciones incorrectas comunes en la medida de desempeño

• Afirmaciones tales como: tamaño igual velocidad, velocidad del reloj.

• CPI puede calcularse de la mezcla de inst. y los tiempos de ejecución del mismo (e.g.: no toma en

cuenta jerarquı́a de memoria, ineficiencia de pipeline)

• Desempeño pico: solo garantiza la velocidad que nunca se superará. Ejemplo:

CRAY X-MP Hitachi

Mejor caso

2.6 sec

1.3 sec Hitachi 105% más rapido

FFT vect.

3.9 sec

7.7 sec CRAY 97

• ¿Qué se puede concluir entre dos maq. que se superan mutuamente en problemas diferentes?

1 Si

no existe en versión ensamblador sino FORTRAN, la perdida de desempeño puede ser hasta de 50%.

pequeño cache tendrá una alta rata de hits.

2 Un

2.6

Bibliografı́a

• [HB84] es un libro general, aunque un poco viejo. Los principios expuestos siguen siendo válidos,

aunque los ejemplos citados son de máquinas por lo general obsoletas. La parte multi-procesadores es

muy pobre.

• [AG89] trata de cubrir las áreas de principios y generalidades del procesamiento paralelo (”Foundations”), la parte de software y finalmente la de arquitectura. No entra en profundidad en ninguna de

ellas pero dá una visión general del área. No cubre vectoriales. En arquitecturas es un compendio de

máquinas paralelas.

• [PH90] es utilizado esencialmente en sus capı́tulos relativos al desempeño, vector processors, pipelining,

memory hierarchy y I/O. No trata las arquitecturas MIMD.

• [Sto90] es otra referencia. Analiza en profundidad el sub-sistema de memoria.

• Revistas especializadas: IEEE Computer, CACM, IEEE T. on P and D Syst, SIGCA, J. of Par and

Dist. Comp, I. Journal on Supercomputing. En particular artı́culos como [Bel89, Bel92], [SC91] y

otros tantos en benchmarking [Wei90], números especiales como [ACM92], etc.

3

Pipelining y máquinas vectoriales

archivo: pipeline.tex

[2 clases]

Fundamento Incremento de velocidad por etapa del cauce.

Sea un pipeline de k etapas (de igual duración)

Speedupn =

Tseq

nk

Tk = k+(n−1)

El término k en el denominador es el tiempo que tarda en llenar el pipe. Notese que cuando n k y

n → ∞ =⇒Speedup → k

Es decir, a mayor etapas, “más paralelismo”, i.e. mayor throughput de instrucciones

Qué podemos encauzar para mejorar velocidad de ejecución?

En 1 procesador

• El ciclo de instrucciones

• Operaciones aritméticas: hasta 14 etapas en CRAY-1 . hasta 26 en CYBER 205

• Operaciones vectoriales

En sistema de procesadores MIMD (organizado por SW) y Arq. Sistólicas

3.1

Factores que limitan speedup ideal de un pipeline

Propagación de reloj a todas las etapas:

Acceso de memoria:

En la tecnologı́a actual esto limita a entre 10 y 20 etapas.

Sea una máquina RISC sencilla, LOAD/STORE, una instrucción por palabra

1. Inst. Fetch – prefetch

2. Dec – decode y operand register fetch

3. Exec – ejecución y cálculo de dire.

4. MEM – accesar operandos en memoria (sólo si instr. LOADS/STORES)

5. WB – guardar resultados en registro

Instr.

Instr.

Instr.

Instr.

1

2

3

4

IF

Dec

Exe

Mem

WB

|-AM--|-----|-----|-AM--|-----|

|-AM--|-----|-----|-AM--|-----|

|-AM--|-----|-----|-AM--|-----|

|-AM--|-----|-----|-AM--|-----|

La memoria debe tener capacidad de ejecutar 2 accesos por ciclo.

Soluciones:

• Uso de cache (depende de una buena localidad)

• Separación de cache de instr. y datos

• Requerimientos de lograr pipeline de accesos (por ejemplo, que pasa si hay falla en cache?)

=⇒ el potencial cuello de botella es movido al subsistema de memoria

Azares estructurales (Structural Hazards)

En la multiplicación de punto flot. hay operaciones sobre la ULA que son costosas, p.e, el shift: es

preferible varias etapas shift de un ciclo a 1 completa de k ciclos. Una multiplicación flotante está dividida

en varias operaciones: suma de los exponentes; generación de los productos parciales de las mantisas (multiplicación); suma de los productos parciales; redondeo al numero de bits según la precesisión; renormalizar

el resultado.

Sumar expon.

Multip. manti

Sumar. prod. parc.

Renormalizar

Redondear

t=1

X

2

3

4

X

X

X

X

5

6

X

7

X

X

Pero si vienen dos sumas seguidas X y Y, se produce un conflicto de uso

Sumar expon.

Multip. mant.

Sumar. prod..

Renormalizar

Redondear

t=1

X

2

Y

X

3

4

XY

X

Y

XY

5

Y

X

6

7

Y

X

X

Y

=⇒ Introducir retardos (burbujas, pausas) para evitar conflictos estructurales. Otra técnica es la greedy

que lanza una operación al momento que no haya conflicto. La técnica basada en vectores de colisión (que

dá resultados buenos), que permiten

• Determinar en c/ paso si el comenzar otra operación conducirı́a a un conflicto posterior

• Determinar el ciclo de comienzo de instr. que maximiza el thruput de instr. (ver Hwang y Briggs,

Stone, etc. para más detalles). Por ejemplo, es posible que una retardo mayor induzca un mejor

desempeño.

Elóptimo se obtiene introduciendo retardos entre etapas de manera apropiada.

Esta técnica nos permite que, dada una situación potencial de aparición de colisiones, como obtener el

máximo desempeño en tales condiciones. Sin embargo, el mayor desempeño se logra si logramos evitar tales

colisiones, por ejemplo:

• Replicando elementos/recursos crı́ticos del HW

• Cambiando el orden de operaciones. Ej: no permitir dos sumas seguidas suma→suma →load =⇒suma→load

→suma. Esto es generalmente responsabilidad del compilador optimizante.

Dependencias (Azares de datos)

Una dependencia de datos puede producir también burbujas. Ej:

ADD R1,R2,R3

(R1 ←− R1+R3)

SUB R4,R1,R5

(R4 ←− R1 – R5)

ADD

SUB

t=1

2

3

4

5

._______._______._______._______._______.

Fetch

Dec

R2+R3

[Mem]

R1 <._______._______._______._______._______.

Fetch

Dec

R1-R5

[Mem]

R4 <-

En t=4, el nuevo valor de R1 por el ADD aún no ha sido actualizado, por lo que el valor usado en SUB

es erróneo.

Solución: forwarding o bypassing. El resultado de la ULA siempre es realimentado al latch de entrada

de la ULA. El HW detecta si la entrada de la próxima instr. debe ser tomada del latch o de los registros.

Inconv. Implementación de bypasses tiene su costo en HW.

Otra solución es mediante reordenamiento de código (trabajo del compilador)

Ej: A ←−B + C

LD R1,B

.Fetch

.Dec

.Ej

.←B

.R1 ← .

LD R2,C

.

.Fetch

.Dec

.Ej

.←C

.R2 ← .

ADD R3,R1,R2.

.Fetch

.Dec

.burb.

.R1+R2 .mem

.R3 ← .

ST R3,A

.

.

.Fetch

.burb.

.Dec

.Ej

.

.

Podrı́a enviarse directamente el resultado del add a memoria sin pasar por R3.

En general, la reexpedición interna busca evitar accesos a memoria innecesarios:

1. R1 −→Mx −→R2 =⇒R1 −→

.

• −→Mx

• −→R2

2. Mx −→R1 Mx −→R1 =⇒Mx −→R1 −→R2

3. R1 −→Mx R2 −→Mx =⇒R2 −→Mx

También el compilador podrı́a tratar de evitar LD seguido por instrucciones que usan inmediatamente el

valor.

Ej: Supongamos que 20% de instr. son LD y 50% de las veces al LD le sigue una instr. que requiere el

res. de la carga. Si la burbuja es de 1 ciclo ¿Cuánta velocidad se pierde?

3

0.8 × 1 + 4 0.2 × 1.5 = 1.1=⇒10%de retraso

Si no hay orden posible que arregle el pb, introducir nop, ie, burbuja, lo cual es más barato que HW

especial.

(en vectoriales veremos otra solución a este problema a nivel de la algoritmica, p.e.: cyclic reduction)

Otros azares de datos se producen en los accesos a la memoria. Estos, por la inyterdependencia, pueden

también producir burbujas en el pipe:

RAW : Leer después de escribir puede traer interlock ya que puede no estar actualizada la memoria cuando

empieza la lectura.

WAR : si la lectura no ha terminado y se manda a escribir hay carrera critica

WAW : carrera crı́tica

RAR : No trae problemas.

Bifurcaciones (Azares de control)

Problema: la próxima inst. buscada, puede no ser la próxima a no ser ejecutada. Ej:

ADD R1,R2,R3

BZ

R1, α

...

α : ...

Hwang and Briggs citan que pipelining puede perder 30-40% efectividad por pbs. de bifurcación

Soluciones: Delayed Branching / Bifurcaciones pronosticadas / Historia de bifurcaciones

3 80%

4 20%

de las veces no hay pb.

de las veces son LD, de las cuales 50promedio para una carga

Delayed Branching: Cambiar orden de instrucciones.Ej:

ADD R1,R2,R3

BZ

R4, α

...

α : ...

se cambia a

BZ

R1, α

ADD R1,R2,R3

...

α : ...

eg: RS6000, basado en observaciones que rara vez se salta sobre una condición recién calculada(!)

Pronosticar la bifurcación a tomar (adivinar camino a tomar): Si salto hacia atrás (fácil de reconocer

por offset negativo), pronosticar hacia atrás =⇒probablemente sea un lazo, los cuales generalmente se ejecutan más de una vez.

BZ — suponer que no da cero

Esta estrategia da resultado en parte porque la inst. a buscar debe estar en el cache (en general). También

por el uso de res. temp. — no se obliga a escribir el resultado hasta que se sepa a ciencia cierta que el

pronóstico es valedero

Historia de bifurcaciones En BP y BN (igualmente probable; depende del compilador) ¿ Hacia donde

salto? podrı́a dejarme convencer por frec. hist. previa a corto plazo. Como los caches se adaptan bien al

comportamoento en hist. reciente, podemos tomar las ideas

Inst. addr

|

|---->

Branch ad.

aaa

bbb

...

Target addres

yyy

xxx

...

Si la instrucción está en el cache, se toma el valor (último utilizado) y se actualiza luego de ejecutada con

el valor real (no el predicho). Si no está, incorporarla al cache con la dirección de branch tomada (polı́tica

de reemplazo?)

Esta idea aún no ha sido muy usada en la práctica (solo IBM 3090 mode. 400, 1986) pero suena razonable

dados las caract/costos de HW actuales (ver Stone p. 175).

H y B sugieren manejo de 2 mem. cache: una por alternativa de salto =⇒engorroso!

3.2

Complicaciones adicionales en manejo de pipeline

Manejo preciso de interrupciones según standard IEEE En realidad, la secuencia ADD SUB de la

pag. 13 puede conducir a carrera crı́tica si ocurre interrupción a mediados de ejecución. Al cambiar orden

de ejecución ADD −→DIV por DIV −→ADD, y ambas producen trap, ¿Cuál se trabaja primero? ¿Por qué?

Para trabajar correctamente el VAX 8800 requiere 4 PC: Program counter, Current Program Counter, IBox

Starting Address, EBox Starting Address5

Aparte, encolar resultados: adelantar los pipes hasta que se puede usar (history file y future file)

Heterogeneidad en duración de inst.: En la Vax una inst. puede llevar de 1 a 100s ciclos =⇒ventajas

de RISC (aunque VAX 8800 lo que hace es pipeline the micro-engine!!)

3.3

Más velocidad aún

Introducir delays para alargar # de etapas: Si suma tarda 3 ciclos, convertirlo en 3 etapas de 1 ciclo

=⇒Cada inst. tarda más pero completamos en cada instr. (ver Stone)

5 Sirven

para saber para cada instrucción donde está en proceso pipeline, 1 PC por etapa!

Loop Unrolling

Máquinas superescalares Ejecutan más de una instr. a la vez, eg: una de pto flot. y una entero. El

manejo de interrupciones requiere aún más cuidado. Ej:

• en SPARC, instr. enteras no causan pb porque terminan pero op. flot. se limitan a 2, y aún ası́, son

imprecisas

• dejar entrar al ALU una instr. solo si las que ya están en ALU no pueden causar interrup. (no es muy

razonable por costo para cosas poco frecuentes)

Encadenar pipelines * seguido de +. (ver máq. vectoriales)

3.4

Falacias

El diseño del set de instr. de las m. es indep. de supipelining:

No, por complicaciones de

• Instrucciones de tamaño variable =⇒Imbalance en etapas, retardos y complican detección de azares.

• Modelos de direcc. sofisticados (post-incr, multiple acceso a mem)

Incrementar el # de etapas del pipe siempre incr. desempeño No, por pbs técnicos de reloj. No,

por mayor dependencia de lazos. Ej: en 14 Livermore Loops (agregar gráfica)

Evaluar un esquema de pipeline con código no-optimizado El código optimizado es más difı́cil de

alterar o reordenar para pipeline. Algunos autores encuentran que ene lc ódigo optim. hay 20% menos

thruput.

4

Máquinas vectoriales

archivo: vector.tex

2 clases

Definición Una máquina vectorial es aquella que tiene instrucciones especiales para trabajar sobre vectores, e.g.

C := A + B

implementados de manera de obtener un alto rendimiento.

Propiedades importantes de tener operaciones vectoriales

• Al pedir una instrucción vectorial se garantiza la ausencia de azares por datos (Ojo! no todo lazo sobre

elemento de un vector garantiza esta independencia =⇒ no todo lazo puede ser vectorizado)

• Una única instrucción vectorial cvonlleva mucho trabajo =⇒red. req. de BW respecto a instr. Pueden

encontrarse reduciones de 600 a 1, ej, SAXPY. Esto rompe con la homogeneidad de duración del set

deinst.

• Las instr. vect. tienen un patrón de acceso predecible:

C[1: 7 : 2]

inf :sup:stride6

:= A[2 : 5 : 1] + B[7 : 4 : −1]

Si es predecible, tal vez podamos incorporar mecanismos para suplir suficientes datos al pipe vect. en

el tiempo requerido

• Se eliminan los azares de control (no hay bifurcación)

¿Cuántas ints. vect? Entre 20 y > 100. La IBM 3090 VF tiene 171

4.1

Arquitecturas vectoriales

Si requerimos hacer operaciones como C := A+B logrando (después de start-up time)una operación completada por ciclo, la memoria requiere trabajar a una velocidad de 3 accesos por ciclo −→PROBLEMA CLAVE!

Soluciones:

• Una memoria de alta velocidad (tipo cache) y sacar datos vectoriales de allı́ (pb: tamaño)

• Memorias intercaladas: dos formas de acceso

– Accesadas de manera sı́ncrona, capturadas en latchs para luego transferirlas una por una.

– Accesadas de manera defasada(en pipe)

El número depende de los req. de la unidad de pipe y de la latencia de la memoria.

Ejemplo: Un pipe que requiere tres accesos por ciclo. La mem. tiene una latencia de 2 ciclos

=⇒3 × 2⇒6 módulos de mem (en general, son potencias de 2)

Ejemplo El siguiente ej. muestra una situación ideal para el proc. vectorial. Tenemos un banco de 8

módulos de mem. con dos ciclos de latencia, y un sumador en pipe. de 4 etapas. La operación realizada es

X = A + B.(llevar p. 264 del Stone).

En este caso, se obtiene un BW de un res. por ciclo. Los pbs surgen cuando los elementos no pueden

almacenarse de manera ótima. Ej:

A

C

:= (E + F ) + G

:= A + B

Las instr. anteriores pueden requerir otro patrón de almacenamientos que produzcan conflictos. Conflictos

en acceso matan una máqina vectorial Posible solución: introducir retardos (CDC Star). Ej: todos

los vectores empiezan en M0 . Se accesa primero A[0] y se guarda en un buffer durante dos ciclos (mientras

se accesa B[0]). Se obtiene el mismo BW pero aumenta la latencia (en vez de empezar a obtener res. al 5

ciclo, lo hace al cabo de 11)

Aunque la solución es elegante, su abuso conduce a desempeño muy inferior a lo lograble mediante otras

arq., eg CRAY-1 vs. CDC Star.

Trampa Concentrarse en desempeño pico e ignorar startup time. Este determina el tamaño de los vectores

para el cuál se obtiene un desempeño mejor que escalar. Esta métrica se denomina nv . Para CDC-Star 100

es 100 y para CRAY-1 es 2. Para que Cyber 205 (descendiente de STar) sea mejor que CRAY-1 se necesitan

vectores de al menos 200 para SAXPY.

Hay algoritmos muy usados, como eliminación gaussiana (para triangular matrices) que en cada iteración

se decrementa de uno la longitud del vector. Otras caracterı́sticas de este algoritmo (comunes a otros algo.

numéricos) son:

• Requiere accesos por filas y por columnas de una matriz

• Operaciones son, en su mayorı́a, V × V →V , V × escalar→V

• Excepciones son operaciones de reducción (escalares) como MAX, que devuelve la posición del elemento

mayor. Este será el pivote.

4.2

¿ Cómo guardar matrices en un banco de mem. intercaladas de forma que

el acceso por fila y por columna sea lo más rápido posible?

[fotocopiar Stone 280+282]

En matriz 8x8 con 8 módulos, almacenar por filas será terrible para acceso por columnas, ya que todos

los ele. de una col. estarán en el mismo módulo. Es preferible agregar una columna dummy.: stride para

acceso por fila: 1, para col:9.

Una forma de evitar este problema es seleccionar un paso7 “s” (es decir, una forma de guardar los elemntos

en mem) que sea primo relativo al núemro de módulos. Los pasos sucesivos accesan módulos separados de

M/MCD(M,s). Como M es generalmente potencia de 2, cualqier s impar salva la situación

4.3

¿Qué otros tipos de accesos se utilizan?

Según Kuck, además de por filas y por col., tenemos:

• por diagonales/antidiagonales. No es posible accesar eficientemente por filas, columnas y diagonales si

el # de módulos es potencia de 2.

• Bloques cuadrados.

Dos sugerencias:

• Que el númeor de módulos en 1 banco no sea una potencia de 2 sino un número primo. (Ej: BSP, con

17, o GF11, con 567?)

• Aplicando hashing a las posiciones de los elementos (no implementado). Es un temas importante de

investigación (Ej: Supercomputing 92: Lang, Valero et al., “Acceso en potencias de 2 sin conflicto”).

Hay otros accesos, s=2, etc. En conclusión: el porgramador debe cuidar/estar pendiente de asignación

de elem. de matriz a memoria según sus patrones de refe.

7 stride

4.4

Arquitecturas basadas en reg. vect

• CRAY intercala bancos de registros vetcoriales entre mem. ppal y pipe vect.

• No es raro encontrar bancos de 64 o 128 reg.

• A diferencia de un cache, deben manejarse explicitamente (compilador o programador)

• A veces puede utilizarse otra mem. entre ppal y reg, que permitira reestructurar datos (ej: para accesar

col. en vez de filas, p. 286b Stone). La ventaja sobre otros métodos (hashing, realignement network)

es que sólo se hace cuando se necesita.

• Los vectores de largo variable (VLR) traen inconv. =⇒técnica de strip-mining

• Soporte del compilador, por ejemplo, para lazos internos: dep. entre elem, intercambiar lazos, strip

mining (ver prox. curso)

Strip-mining: Los registros vectoriales tienen un tamaño que determina el número máximo de elementos

que puede procesarse simultáneamente de manera vectorial. Este es el Maximum Vector Length (MVL). El

tamaño de una operación vectorial es un parámetro dinámico, por lo que se usa un registro especial, VLR,

para guardar dicha talla. Strip-mining es la generación de código tal que cada operación vectorial sea hecha

para una talla ≤ MVL.

Si el número de elementos a procesar es N > M V L, la operación debe realizarse en varios bloques. El

primero se hace por el resto de la división entera por MVL, es decir, V LR←N mod M V L, y el resto de

las operaciones se harán tal que V LR←M V L. Esto implica un overhead adicional de load y store de los

bloques, y de carga del nuevo valor de VLR.

Ejemplo: la version strip-mined de SAXPY es (tomado de H y P,p. 364)

low = 1

VL = (N mod MVL) /* bloque incompleto */

do 1 j = 0,(N/MVL) /*lazo externo*/

do 10 i = low,low+VL-1 /* vectorizado por el compilador */

Y(i) = a*X(i) + Y(i)

10:

continue

low = low + VL /* inicio del nuevo vector */

VL = MVL /*resetea MVL */

1: continue

Conduce al siguiente modelo de desempeño

Ttotal

= TstartupT otal a + (

N

+ 1) × (Tlazo b + (Tstartup c ) + N × Telem

MV L

a Cáclulo

de la dirección del vector, inicialización control vectorial, etc

escalar de stripmining

c recarga de pipes por bloque

b código

4.5

Mejoras a máquinas vect.

Encadenamiento (forwarding extendido a unidades vectoriales): Ejemplo: SAXPY

Comparación interesante respecto a capa. de encadenamiento en Cheng “Vector Pipelining, Chaining

and Speed on the IBM 3090 and CRAY X-MP”, Computer, Sept. 1989

• nV depende de operación (asig., SAXPY, etc)

– IBM: 5 – 13

– X-MP: 2

• X-MP es más robusto: tarda idem A*X+Y que (A+X)*Y. IBM es asimétrico

• División: IBM:17.4 ciclos. CRAY: 2 ciclos

• En X-MP: 14 ciclos para cargar un escalar, 17 para u elem. de vector.

Máscara de vectores (vectores enmascarados)

do 100 i=1,64

if A[i] <> 0 then A[i]:=A[i]-B[i]

100 continue

Las desventajas son: no reduce tiempo de eje.; En algunas máquinas, las oper. se ejecutan pero no se guarda

el res. =⇒interrup. por div por 0 puede ocurrir!

Oper. de reducción

s := ai × bi + s −→

si := si−d + ai × bi

Se termina con d sumatorias parciales que hay que sumar, y puede cambiar el orden de las sumas (overflows!).

Otra técnica es el “Recursive doubling”: se suman 2 vectores de 64 reg, luego 2 de 32 y asi ...

Manejo de matrices sparse

• Vector de bits: reducción 1 a 64. Se usa 1 bit para repr. 64 bits de una doble palabra. El problema es

que la esparsidad práctica es mucho mayor, e.g., SIMPAR: entre 0.1 y 0,01%

• Hashing non zero elem.

• Compresión/expansión: expandir esparse en vectores; hacer oper; recomprimir.

• Usar scatter/gather.(scatter: comprimir un vector de acuerdo a un vector máscara; gather: intercalar

dos vectores comprimidos)

Uso de varios pipes : igual que Tomasulo, etc. Bin-packing (método de scheduling)

Problema abierto

4.6

El uso apropiado de cache en sist. vect.

Métricas adicionales para medir desempeño de maqs vect.

Hockney’s

• r∞ : MFLOPS sobre vector infinito, i.e., se ignora el startup time. Generalmente n=1000.

−1

r∞

= lim

n→∞

Tstart + Te × n

⇒r∞ = 1/Te

n

• n1/2 : largo del vector para alcanzar r∞ /2. n1/2 = tstart /te ya que n1/2 se alcanza cuando el tiempo

de procesar esos elementos es igual al tiempo de startup.

Si mejoro el reloj, afecto r∞ mientras que si agrego etapas al pipe, afecto n1/2 .

Derivación de Hockney’s

Puede realizarse a partir de datos del fabricante: r∞ es ciclos por seg, si en cada ciclo puede darse una salida

(notese que depende de oper!).

n1/2 = s + k − 1, donde s es el overhead general (fetch operand, store VLR, etc.),k número de etpas de pipe.

También puede medirse experimentalmente: correr el sgte programa

call second(t1)

call second(t1)

To <- T2-T1

do 20 n=1,NMAX **1000

call second(t1)

do 10 i=1,N

10: A(I)=B(I)xC(I)

call second(t2)

T=(T2-T1)-T0

20: write(T,n)

; le compilador vectoriza esto

Graficar T vs n. La inversa de la pendiente de esta recta es r∞ . Extrapolando, se obtiene el punto de

corte con el eje de n, que es n1/2 .

Una de las grandes ideas de Cray fué tener un nV pequeño. P.e., las máquinas japonesas tienen startup

50-100% mayor que Cray.

4.7

Trampas y falacias

Trampa Incremente el desempeño vectoreial e ignore desempeño escalar. La situación tı́pica es que 50%

del tiempo se dedica a oper. escalares. Ej: si nos concentramos en mejorar por 4 veces el perf. vectorial,

obtenemos

T

4T

S=

=

= 1.6

0.5T + 0.5T /4

2.5T

Falacia Puede obtener desempeño vect. sin anchode banda de mem. Cray-1 mejoró desempeño en LINPACK por factor 2x usando transformaciones sofisticadas que permitieron retener + datos en reg.

5

Sub-sistema de memoria

archivo: memoria.tex

1 clase

5.1

Cache

¿Por qué cache?

• CPU performance

– antes de 1985: 1926% crec. anual en

velocidad

– después de 1985: 50100%

• Memoria principal (DRAM): 7% anual

=⇒un nivel adicional en la jerarquı́a de memoria que siga el paso (CACHE, hecha en SRam, más cara),

cuya eficiencia se basa en la localidad espacial: “ Si un item es referenciadp, pronto items cercanos serán

referenciados también”.

Tendencias

1970 1980 1990

Cache en sist. comerciales

2K

8K

256K

Cache en supercomputadoras

(vectoriales)

16K 64K

1M

“A medida que la capacidad de memoria aumenta de 107 bytes a 108 y 109 , hay una fuerte probabilidad

que el cache no crezca linealmente con la memoria ppal. En efecto, varios constructores, tales como Amdhal

y Hitachi han producido máquinas con 2 niveles de cache” (Stone)

5.2

Organización de un cache

Directorio del cache (bits de control, ver más adelante)

Conjuntos asociativos de lı́neas8 o bloques: Varias alternativas para esto.

• Correspondencia directa (Direct Mapped): el bloque i de memoria ⇒lı́nea mod Número de lı́neas

del cache (un conjunto asociativo). Ej: Sea un cache de 8Kbytes, organizado en 128 lı́neas de 16

palabras de 4 bytes cada una (1 lı́nea = 64 bytes). Para obtener la posición en el cache de una

dirección ADD (en bytes):

Lı́nea =(ADD div 64) mod 128

El cache necesita guardar sólo los bits más significativos de la dirección para saber cuá de los

posibles bloques de memoria se encuentra en el bloque de cache. Ventajas: costo de impl. en

HW es bajo. La polı́tica de reemplazo es trivial. Desventajas: puede haber reemplazo aunque

cache no esté lleno. Mal desempeño si se requieren dos bloques mapeados al mismo bloque.

• Totalmente asociativa (Fully associative): cada bloque de la memoria puede estar mapeado en

cualquier bloque del cache. Esto implica que para obtener una dirección ADD, se debe buscar de

manera asociativa en el campo de la dirección (el cual debe contener todos los bits de dirección

de la lı́nea). Ventajas: Uso eficiente del cache, buena tasa de aciertos. Desventajas: El costo

en HW y tiempo de tener una memoria totalmente asociativa y de bus’queda.

• Asociación por conjuntos (Set associative): El cache se divide en grupos (sets). Cada bloque

de memoria está mapeado a uno de los grupos. Dentro de cada grupo, un bloque puede ocupar

cualquiera de las lı́neas. Es equivalente a dividir el cache en n sub-caches directamentre mapeados.

Un n-way set associative cache define un cache donde cada grupo tiene n bloques. Ejemplo: mismo

cache que antes, pero 2-way ass. Para saber si ADD está en el cache, determinamos en que grupo

está mapeado, y luego hacemos una búsqueda asociativa en los bloques del grupo

Grupo =(ADD div 64) mod (Tamaño del cache (128) / n (2) = 64)

El set-ass. es el más común. La heurı́stica es que la tasa de fallas (miss rate) de un cache directamente

mapeado de tamaño X es aprox. el mismo de un 2-way de talla X/2.

5.3

Polı́ticas a definir para manejo de cache

Polı́tica de colocación:

depende de la organización.

Polı́tica de extracción:

(Cómo y qué inf. entra al cache)

extracción por demanda

extracción anticipada (prefetching): Al fallar ref., traer i e i+1. Al ref. por prim. vez linea i en cache,

traer i+1.

extracción selectiva Datos que no pueden ser traı́dos al cache. (eg: datos compartidos)

Polı́ticas de reemplazo (qué lı́nea sale del cache): LRU, al azar (HyP encuentran que azar y LRU son

ambos buenos a partir de cierta cap. de cache, pero azar es más barato)

5.4

Problemas abiertos

Un cache único o varios (Ej: instr., escalares, vectores). Un sólo cache permite que el sist. busque

mejor, pero puede haber contención. La tendencia en maq. escal./superescal. es a más de un cache.

Tamaño: La curva del beneficio resp. al tamaño (en miss rate) descelera a partir de cierto punto:

empı́ricamente, duplicar tamaño, reduce % fallas en 30%.

Tamaño de lı́nea: depende del modelo de accesos. Si hay una alta localidad espacial, mientras mayor

tamaño mejor (pero el stride puede invalidar esto!). En cambio, si hay varios puntos de localidad, es preferible

más lı́neas más pequeñas. Esta última es la tendencia excepto en máquinas vctoriales.

5.5

Efecto de las fallas

La pérdida se modeliza de la sgte manera:

tef f

= tcache + (1 − h)tmain

h es el hit rate. Si main es 10 veces más lento, decrementar h de 0.99 a 0.98 incrmenta tef f en 10%. Un

incremento de 10% en h duplica tef f tcache depende de la organización.

5.6

Cache en arq. vectoriales

La mejora de cache en arq. vect. es muy discutida. Generalmente, los pbs en algebra lineal usan una

cantidad de datos que sobrepasa de lejos la cap. de los caches. Además, si el stride es mayor que el tamaño

de la lı́nea, estaremos trayendo lı́neas al cache frecnetemente. En conlcusión, en lugra de mejorar puede

empeorar!.

CRAY no tiene cache, sino bloques de reg. usados explicite. por programador. ¿Cómo debe ser un cache

para vectores? Grande para contener todo un vector? ¿Pequeño y contener muchos fragmentos de vectores?

OJO: Accesos seriales a vectores atentan contra el cache con LRU, ya que la carga de un vector puede

vaciar (flush) un cache entero y dejar solo data inútil. Entonces, qué polı́tica usar. Problema abierto.

Stone concluye que “Los registros vectoriales deben ser organizados como registros accesibles por el

programa en vez de cache hasta que se sepa como mejorar desempeño con cache organziado por vectores.

5.7

Polı́ticas de actualización de mem. ppal

Write-through: actualizar directamente la palabra modificada en cache ⇒cache y mem. siempre consistentes. ¿Qué hacer si al tratar de escribir hay falla de cache? Alternativas:

1. write-through-with-write-allocate: escribir en mem. ppal, y traer bloque act. al cache.

2. write-through-with-no-write-allocate: sólo escribir en mem. ppal.

DEJAR QUE PIENSEN

Analizar alternativas resp. dato empı́rico: 5–30% de operaciones son de escribir 70-95% de lectura. (en

relaidad estos datos no son de gran ayuda. Los wites vienen en grupos o no? La localidad de ref. se mantiene

durante las sec. de write?

Write-back: En caso de falla de escritura, traer bloque al cache. Ensuciar(poner bit de “dirty”) solo cache

y act. mem. ppal cuando se reemplace el bloque del cache. Variantes:

• Write-back simple: esc. en mem.ppal el bloque reemplazado. (no usa bit “sucio”).

• Flagged Write-back: escribir sólo si tiene bit de “sucio” en ON.

En reemplazo, dar prioridad a traer nuevo bloque, para solapar overwriting con oper. del procesador. Esto

requiere un bloque de registros de “escrituras en curso”.

5.8

Cache y E/S

¿Dónde colocar el cache?

a)

b)

CPU -------

CACHE ------ MEM. PPAL

|

|

I/O PROCESSOR

CPU -------

CACHE

------ MEM. PPAL

|

|

I/O PROCESSOR

a) tiene demasiada actividad en cache.

b) es preferible resp. desempeño pero ... consistencia lógica entre CAHE y mem. debeser exacto para evitar

que CPU encuentre un valor y I/O Proc. otro. Solución posible: usar write-thru para cosnistencia ree.

escrituras en cache y Mem se entera de cambios en cache. Pero ¿Cómo se entera cache de cambios en Mem?

• I/O Proc. debe invalidar datos en cache, y forzar que se produzca un cache miss simulado, prendiendo

bit “corrupted” en directorio.

• I/O Proc. escribe nuevos datos en cache en vez de invalidar. “Para la mayor parte de los sistemas, la

prob. que un update conlleve a un cache hit es baja y no justifica el tráfico extra hacia el cache”.

Pero, y si quiero (me conviene) usar write-back para disminuir tráfico

CPU -------

CACHE ------ MEM. PPAL

\

/

\

/

I/O PROCESSOR

El I/Oproc. conserva una copia del directorio del cache. Esto es necesario para poder invalidar.

En write-back, el I/O pide datos en CACHE (revisa si está en dir). El dir. se actualiza para ambos solo

si hay un cache miss.

6

CASO MAQUINA VECTORIAL: CRAY

archivo: crays.tex

6.1

CRAY Y-MP C90

Tomado de [Cra92]

6.1.1

Generalidades

La C90 posee 8 o 16 procesadores.

Posee soporte para multitasking en cada procesador, paralelismo (un programa corriendo en varios procesadores) y Autotasking (partición automática de programas en CFT77 en tareas para ejecución en varios

procesadores). Posee dual-mode.

6.1.2

Pipelining and segmentation

Todo el hardware está completamente segmentado. Esto implica que todas las operaciones (exchange sequences, memory ref, inst. fetch sequences, inst. issue sequences y unidades funcionales) entregan un

resultado por CP9

6.1.3

Sección de comunicación inter-procesadores (ICS)

EL ICS contiene registros y semáforos compartidos para pasar datos e información de control entre porocesadores. Además contiene lógica que permite a un CPu interrumpir a otro y hacerlo cambiar a modo monitor

(especial para multitasking).

Los reg. y semáforos comp. están divididos en grupos idénticos (clusters) de 8 32-bit shared address

(SB) reg., 8 64-bit shared scalar (ST) reg, y 32 sem. (SM) de 1 bit. Cada CPU está asignado a un cluster,

a cuyos reg. tiene acceso.

Para transferir datos entre CPUs, un CPU carga los datos en registros compartidos desde sus registros

escalares o de dirección, luego otro CPU asignado al mismo cluster puede leerlos.

Los reg. semáforos permiten a un CPU de suspenderse temporalmente para sincronizarse con otro. Cada

CPU puede prender o apagar un SM reg de su cluster, y luego realizar un Test and Set sobre esos reg. Un

TAS sobre un SM ejecutado por un CPU puede hacer que su operación se suspenda hasta que otro CPU

apague el SM. El HW detecta si todos están haciendo TAS (deadlock).

6.1.4

Sección de cómputo del CPU

Registros

Dirección: 8 reg. A y 64 reg. B, de 32 bits c/u. Los A sirven especialmente para referenciar la memoria

o como ı́ndices, además de control de lazos, oper. de I/O, etc. Los B sirven para almacenamiento

intermedio de los A.