•Las arquitecturas Pipeline (Segmentadas) surgen por la necesidad

Anuncio

!"

•Las arquitecturas Pipeline (Segmentadas) surgen por

la necesidad de aumentar la velocidad de

procesamiento

•La velocidad, en un sistema secuencial síncrono, está

limitada, entre otros factores, por:

•Tecnológicos

•Consumo

•Restricciones algorítmicas

•Arquitecturales

•Etc

•Segmentar una arquitectura es dividirla en segmentos

o etapas

•Cada segmento (etapa) está definido por un registro

que almacena los datos a procesar y otro que almacena

los resultados

Entrada

Salida

Unidad de Procesamiento no

segmentada

CLK

Salida

Entrada

E1

E2

En

CLK

Arq. Segmentada (n segmentos o etapas)

#%$&$(')$"#+*-,%'$/.!0(132

!"

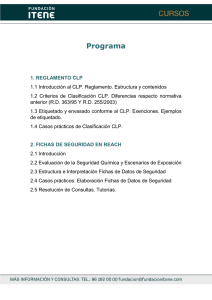

•CLASIFICACIÓN:

1.- LINEAL: Está formado por un conjunto de etapas

conectadas en cascada, sin bucles de realimentación de

datos

2.- NO LINEAL: Pueden existir bucles hacia delante o

hacia atrás ()HHGEDFNIHHGIRUZDUG)

•Atendiendo a la función que realizan se pueden

clasificar en:

1.- ESTÁTICOS: Realizan una función fija sobre un

conjunto de datos de entrada

2.- DINÁMICOS: Realizan diferentes funciones sobre

un conjunto de datos de entrada

#%$&$(')$"#+*-,%'$/.!0(134

!"

•DEFINICIONES BÁSICAS:

•Partiendo de la arquitectura genérica de un pipeline

estático, como el representado en la figura:

Salida

Entrada

E2

E1

Ek

CLK

1.- TABLA DE RESERVA de un pipeline lineal

estático de K etapas

t=0

TIEMPO (CICLOS DE CLK)

T1

E1

E2

E3

...

T2

T3 .......................................... Tk

X

X

X

....................................................................

Ek

X

Indican en qué etapa hay datos procesándose, en un

determinado ciclo de reloj

#%$&$(')$"#+*-,%'$/.!0(135

!"

2.- Tal y como se vió, al estudiar el Skew, se ha de

cumplir que:

δ+T≥trmáx+2.ti+τcmáx+tsmáx

Tmin= trmáx +2.ti+τcmáx+tsmáx- δ

•La frecuencia máxima será:

I

máx

=

1

7

PLQ

3.- Se define el THROUGHPUT como el nº de datos

procesados por unidad de tiempo:

TH=f⇒Siempre que se mantenga

un flujo cte de datos de entrada

4.- SPEEDUP(SK):

•En un pipeline lineal estático de K etapas y n datos a

procesar, el nº de ciclos de reloj necesario es:

K+(n-1)

#%$&$(')$"#+*-,%'$/.!0(637

!"

•En una arquitectura no pipeline será:

n.K

•Luego el Speedup (SK), es:

6 :

Q

=

.

..

+ ( Q − 1)

•Si el número de datos, n, es muy grande:

n→∞

SK=SKmáx=K

5.- EFICIENCIA (EK):

(<

=

6<

.

=

Q

.

; →∞

+ (Q −1)

→1

6.- THROUGHPUT (TH):

7>

Q

Q I

= →∞

.

=

=

→ I

[. + (Q −1)].7 . + (Q −1)

#%$&$(')$"#+*-,%'$/.!0(698

!"

•Control de arquitecturas segmentadas

•Se trata de saber cuándo y cómo introducir un dato

nuevo en el pipeline:

•Para obtener un rendimiento máximo

•Y que no existan colisiones, es decir, que no se

introduzca un nuevo dato en una etapa antes de

haber procesado el anterior

•Máximo rendimiento≡Throughput máximo

7L

máx

=

1

º GDWRV ?A@CBDEGFIHJBKF

WLHPSR

•EJEMPLOS:

1.- Pipeline estático lineal que realiza la función A

(con 3 etapas)

t0

E1

E2

E3

t1

t2

t3

t4

A1 A2 A3 A4 A5

A1 A2 A3 A4

A1 A2 A3

..........

tn

...

...

... An-1

t0=t1=t2=.................=tn=T(periodo de reloj)

A1=dato1;A2=dato2......;An-1=daton-1

“llenado” del pipeline=LATENCIA INICIAL

#%$&$(')$"#+*-,%'$/.!0(631

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

•El control de este tipo de pipelines es trivial:

•Se introduce un dato en cada ciclo de reloj (sin

colisiones)

•Para procesar A1 (a la salida de E3) transcurren

3 ciclos de reloj: Latencia Inicial

•A partir de ese instante se obtiene un resultado

por cada ciclo de reloj

•Para procesar n datos:

[

.

+ (Q −1)].7 = [3+ Q −1].7 = (Q + 2).7

•SPEEDUP(S3):

6

Q

3

.3.7

=

( Q + 2).7

d → ∞

→ 3 ⇒ 1 º (WDSDV

•Eficiencia (E3):

(

3

=

6

3

3

=

Q

Q

+ 2

e →∞

→ 1

[%\]\(^)\"[+_-`%^\/a!b(c3c

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

•THROUGHPUT (TH):

7h

=

Q

Q

.I

+ 2

g →∞

→

I

1

=

7

•Se define la Latencia Media como:

•Nº de unidades de tiempo (T) transcurridas

entre 2 entradas consecutivas

/DWHQFLD

_

0HGLD

=

1

7i

•Se define la utilización media de una etapa o

segmento (en %) como:

7LHPSR

_ GH _ XVR _ GH _ XQD _ HWDSD

7LHPSR _ WRWDO _ GH _ SURFHVDGR ( Q _ GDWRV )

[%\]\(^)\"[+_-`%^\/a!b(cfa

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

2.- Pipeline estático no lineal que realiza la función B

con 3 etapas

t0

E0

t1

B

t2

t3

t4

t5

t6

B

B

B

E1

t7

B

B

B

E2

B

TABLA DE RESERVA

•Estrategias de Control:

1ª.- “Introducir un nuevo dato en cuanto se pueda”

t0

E1

E2

E3

t1

B1 B1

t2 t3

t4

t5

t6

t7

t8 t9 t10 t11 t12 t13 t14 t15

B2 B2

B1 B1

B2 B2 B3 B3

B1

B1 B2

B2

B3

B3

B1

B1 B2

B2

B3

•Ciclo estable=11.T ciclos de reloj

•Secuencia de latencias <3T,8T,3T,8T,...>

•Ciclo estable (3T,8T)=11.T

[%\]\(^)\"[+_-`%^\/a!b(c3j

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

•Latencia media=5’5 (11ciclos de reloj/2 datos

procesados)

•Utilización de etapas:

E1⇒8/11≈73%

E2 ⇒4/11≈36%

E3 ⇒4/11≈36%

•Speedup (S3):

2datosx8ciclosxT

S3=16.T/11.T ≈1’45

•Eficiencia (E3):

E3=S3/3 ≈0’48 ⇒50% máximo

•Throughput (TH):

TH=11 ciclos/2 datos

[%\]\(^)\"[+_-`%^\/a!b(c3k

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

2ª.- “Prueba y Error: Esperamos 4 ciclos de reloj y

analizamos el pipeline”

t0

E1

E2

E3

t1

B1 B1

t2

t3 t4

t5 t6

t7

t8

t9 t10 t11 t12 t13 t14 t15

B2 B2 B1 B1 B3 B3 B2 B2 B4 B4 B3 B3

B1

B1

B2

B2

B3

B3

B4

B1

B1

B2

B2

B3

B3

B4

Ciclo estable ≡ 8.T

•Ritmo de entrada=2 datos/8.T

•Secuencia de latencias <4,4,....>

•Ciclo estable (4T,4T) = 8.T

•Latencia Media = 8 ciclos/2 datos = 4

•Utilización de etapas (en el ciclo estable):

E1⇒100% ⇒¡Es óptimo, no se puede mejorar!

E2 ⇒50%

E3 ⇒50%

•Speedup (S3):

S3=16.T/8.T= 2

•Eficiencia (E3):

E3=S3/3≈0’66.... ⇒ 66’6%

[%\]\(^)\"[+_-`%^\/a!b(c3l

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

•Throughput (TH):

TH=1/latencia media=0’25

•Hay que formalizar el método, no vale con “prueba y

error”

•Hay que demostrar que el control es óptimo

•Se puede demostrar que: “LA MÍNIMA LATENCIA

ALCANZABLE (M.A.L.) ES MAYOR O IGUAL

QUE EL MÁXIMO DEL Nº DE VECES QUE SE

UTILIZA UNA ETAPA PARA PROCESAR UN

DATO”

•En el ejemplo anterior, para la función B, de la tabla de

reserva original se ve que:

•E1 se utiliza 4 veces, E2 se utiliza 2 veces y E3 2

veces.

•La M.A.L es 4

•FORMALIZACIÓN DEL MÉTODO

•Se define el vector de colisiones, Vc, como:

Vc(i)=ARRAY (0..H-1) OF BOOLEAN

H⇒Nº de ciclos de reloj para procesar un dato en

la tabla de reserva

1 ⇒Colisión si entra un nuevo dato en i ciclos de reloj

Vc(i) 0 ⇒No habrá colisión

[%\]\(^)\"[+_-`%^\/a!b(c3m

MNOPQ

RSOMQTUQVTNSWQO

MXVTY Z!VZ"O

•Se define el conjunto de latencias prohibidas por

cada segmento o etapa:

CLP(n)n≡Nº de etapas⇒Indica cuando se produce

colisión

•Se define el CLP de todo el pipeline, como:

CLP=UnCLP(n)

•Se obtendrá el vector de colisiones Vc, a partir del

CLP del pipeline:

1⇒Si i está en el CLP

Vc(i)

0 ⇒Si i no está en el CLP

•EJEMPLO:

E0

E1

E2

t0

t1

B

B

t2

t3

B

t4

t5

B

B

t6

t7

B

B

CLP(1)={0,1,2,5,6,7}

CLP(2)={0,2}

B

CLP(3)={0,2}

CLP=U3CLP(i)={0,1,2,5,6,7}

Vc(i)=<1,1,1,0,0,0,1,1,1>

[%\]\(^)\"[+_-`%^\/a!b(c3n

opqrs

tuqosvwsxvpuysq

ozxv{ |!x|"q

•Diagrama de estados de Vc(i)

Vector inicial

11100111

La

ten

cia

≥

8

≥8

c ia

ten

La

=3

a

i

nc

e

t

La

Latencia≥8

La

te n

cia

=

4

11110111

11111111

Latencia=4

*Se obtiene haciendo

*Se obtiene haciendo

el OR lógico:

el OR lógico:

00111000

11100111

11111111

Vc DESPLAZADO

Vc ORIGINAL

01110000

11100111

11110111

•CICLO (3,8) → CICLO “ANSIOSO”

•CICLO (8,8) → CICLO “TONTO”

•CICLO (4,4) → CICLO “ÓPTIMO”

LATENCIA MEDIA = M.A.L.=4

}%~~()~"}+-%~/!K

opqrs

tuqosvwsxvpuysq

ozxv{ |!x|"q

•En ocasiones no es posible alcanzar MAL, o

Throughput máximo

•Una posible solución (a veces no se consigue) es

insertar ciclos de espera.

•EJEMPLO: Pipeline con 3 etapas, Función A.

t0

E1

E2

E3

t1

A

A

A

t2

A

A

CLP(1)={0,2}

CLP(2)={0,1}

CLP(3)={0}

CLP=U3CLP(n)={0,1,2}

Vc(i)=<1,1,1>

•Diagrama de estados de Vc(i):

111

Latencia≥3

•Se sabe que MAL=2, pues es el máximo Nº de veces

que se utiliza E1 y E2 para procesar un dato

}%~~()~"}+-%~/!

opqrs

tuqosvwsxvpuysq

ozxv{ |!x|"q

•Si se introduce un estado de espera D, se obtiene:

t0

t1

t2

A

E1

t3

CLP(1)={0,2}

A

A

A

E2

E3

A

X

CLP(2)={0,2}

CLP(3)={0}

A

D

CLP(4)={0}

•CLP=U4CLP(i)={0,2}

•Vc=<1,0,1,0>

•Diagrama de estados de Vc:

L

cia≥3

n

e

t

a

L

1010

=1

a

i

nc

e

t

a

Lat

enc

ia≥

3

1110

•Latencia media=1+3/2(datos)=2=M.A.L.

t0

E1

E2

E3

D

t1

t2

t3

t4

t5

A1 A2 A1 A2 A3 A4

A1 A2 A1 A2 A3

A3

A1 A2

A1 A2

t6

t7

t8

A3 A4 A5

A4 A3 A4

A4

A3 A4

Ciclo estable (2 datos procesados)

}%~~()~"}+-%~/!K

opqrs

tuqosvwsxvpuysq

ozxv{ |!x|"q

•CONCLUSIONES:

1.- En una arquitectura pipeline, los datos QRVH

SURFHVDQPiVGHSULVD; incluso más despacio (más Hw,

estados de espera, etc)

2.- Se procesan mayor nº de datos por unidad de tiempo

(Throughput)

3.- Una vez alcanzado el ciclo estable (pipelines

estáticos no lineales) el throughput es máximo

4.- En los lineales, una vez “llenado” el pipeline

(latencia inicial), se obtiene un resultado por ciclo de

reloj

5.- Para que 3 y 4 sean ciertos, el flujo de datos de

entrada debe ser continuo y grande

6.- El control de los pipelines lineales es muy simple; el

de los no lineales requiere de autómatas que “decidan”

cuándo y cómo introducir nuevos datos y su ruta por la

arquitectura

}%~~()~"}+-%~/!K