Tema 7: Gestión de memoria

Anuncio

Sistemas operativos

Tema 7: Gestión de memoria

La memoria principal

►

La memoria es el componente central en la arquitectura de un

computador.

A menudo, el único dispositivo de almacenamiento al que la CPU puede

acceder directamente.

Un vector de palabras, cada una con su propia dirección física.

La CPU lee instrucciones y lee o modifica datos de la memoria durante

cada ciclo de instrucción.

► Las operaciones de E/S con DMA (acceso directo a memoria)

escriben/leen datos en memoria.

►

CPU

Caché

MP

DMA

Gestión de memoria

►

Asignar y liberar espacio en memoria según se necesite.

La política empleada repercute en la utilización de la CPU y los

tiempos de respuesta del sistema.

Reubicación: vinculación del espacio de direcciones lógicas de cada

proceso con direcciones físicas concretas.

►

Seguir la pista de qué partes de la memoria están siendo

usadas y por qué procesos.

Protección: impedir accesos (accidentales o malintencionados) a la

memoria propia de otros procesos o del SO.

Compartición: permitir el acceso de varios procesos a zonas de

memoria comunes.

► Comunicación

entre procesos, mismo código para varias instancias de

un mismo programa, etc.

Sobre la reubicación

►

Reubicación estática en tiempo de compilación.

►

Reubicación estática durante la carga.

►

Reubicación dinámica.

Dirección lógica = dirección física.

El compilador genera código máquina con direcciones absolutas.

Dirección lógica = dirección física.

El código máquina contiene direcciones relativas al comienzo del

programa (código reubicable), que se vinculan a direcciones físicas

al comenzar su ejecución.

Dirección lógica ≠ dirección física.

Código reubicable.

Las direcciones físicas se calculan en tiempo de ejecución, por

medio de un soporte hardware especializado (unidad de gestión de

memoria, MMU).

Sobre la protección

► En

general, la ubicación de un proceso en

memoria no se conoce de antemano, y no es

posible anticipar todas sus referencias a memoria.

Muchas las referencias se calculan dinámicamente (e.g.

a raíz de instrucciones malloc).

► La

protección requiere mecanismos que actúen en

tiempo de ejecución.

La solución prácticamente universal es proveerla por

hardware, en la propia MMU.

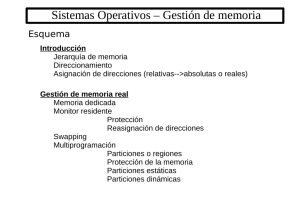

Técnicas de gestión de memoria

► Monitor

residente.

► Asignación contigua con particiones

múltiples.

Particiones estáticas.

Particiones dinámicas.

► Asignación

no contigua.

Paginación.

Segmentación.

Segmentación paginada.

Monitor residente

Monitor residente

► Se

divide la memoria en dos zonas: monitor

residente (SO) y espacio de usuario.

► Con reubicación estática:

Registro barrera

CPU

Dir. física

≥

NO

TRAP

SO

SÍ

Espacio de

usuario

Monitor residente

► Con

reubicación dinámica:

Registro barrera

CPU

Dir. lógica

+

SO

Dir. física

Espacio de

usuario

Intercambio (swapping)

► Forma

de conseguir multiprogramación, utilizando

almacenamiento secundario de apoyo.

SO

1

P1

Espacio de

usuario

P2

2

Intercambio

► Tiempos

de cambio de contexto muy elevados.

Mejoran solapando la carga o descarga de un proceso

con la ejecución de otro.

► Buffers

► Cuidado

del SO, e intercambio dentro de la memoria principal.

con las operaciones de E/S por DMA.

Podrían iniciarse sobre la memoria de un proceso y

terminar sobre la de otro.

Soluciones:

► No

descargar procesos con E/S pendiente.

► Realizar la E/S sobre buffers del SO.

Asignación contigua

con particiones múltiples

Sistemas de particiones múltiples

► Objetivo:

soporte más eficiente a la

multiprogramación.

► Se divide el espacio de usuario en un conjunto de

regiones o particiones.

Cada región alberga un proceso.

► Dos

variantes:

Multiprogramación con número fijo de tareas (MFT):

particiones estáticas.

Multiprogramación con número variable de tareas

(MVT): particiones dinámicas.

Con reubicación estática

Lím. inferior

Dir. física

CPU

P2

Lím. superior

SO

P1

≥

NO

TRAP

SÍ

≤

NO

SÍ

P2

TRAP

P3

►

Los límites se actualizan en los cambios de contexto, con la

información del bloque de control del proceso en cuestión.

Con reubicación dinámica

Tamaño

Dir. lógica

CPU

P2

≤

NO

SÍ

Dir. base

+

SO

P1

Dir. física

P2

TRAP

P3

►

El tamaño y la dirección base se actualizan en los cambios

de contexto.

MFT

► Las

particiones de la memoria son fijas, definidas

a priori.

► Asignación de procesos a particiones:

Una cola de procesos por partición.

► Estrategia

best-fit: cada proceso se asigna a la partición más

pequeña que puede albergarlo.

► Posibilidad de particiones vacías aún habiendo procesos

preparados que cabrían en ellas.

Una única cola.

best-fit-only.

► Estrategia best-fit-available: los procesos entran en la partición

► Estrategia

más pequeña en que caben de entre las disponibles.

Ejemplo

SO

2KB

7KB 3KB 2KB 5KB

6KB

12KB

2KB

►

►

►

El proceso de 5KB entra

en la partición de 6KB.

El proceso de 2KB entra

en una partición de 2KB.

Best-fit-only:

►

El proceso de 3KB espera.

Con exploración de la cola,

el proceso de 7KB entra en

la partición de 12KB.

Best-fit-available:

El proceso de 3KB entra

en la partición de 12KB.

Más sobre MFT

► Utilizando

intercambio, se puede aumentar el

grado de multiprogramación más allá del número

de particiones.

Los procesos pueden residir en particiones distintas

durante su ejecución sólo con reubicación dinámica.

► ¿Qué

hacer si un proceso solicita más memoria,

excediendo el tamaño de la partición asignada?

No conceder más memoria y abortar la ejecución.

Encolar el proceso en espera de una partición

suficientemente grande.

► Exige

reubicación dinámica.

Fragmentación

Aprovechamiento subóptimo de la memoria.

► Fragmentación interna: memoria asignada que no se utiliza.

► Fragmentación externa: memoria desocupada que no puede

aprovecharse para dar cabida a nuevos procesos.

►

SO

6KB 6KB

►

10KB 7KB

FI 3KB

4KB 3KB

4KB

4KB

FI 1KB

FE 8KB

En MFT no habría fragmentación si las particiones coincidieran con el

tamaño de los procesos.

MVT

►

El tamaño y número de las particiones de la memoria varía

dinámicamente.

Mayor flexibilidad que MFT.

Elimina la fragmentación interna: a cada proceso se le asigna

únicamente la memoria que va a utilizar.

SO

SO

SO

SO

SO

SO

P1

P1

P1

P1

P1

P2

P2

P3

P4

P3

P3

Hardware y software para MVT

►

Mismo hardware que en MFT.

Predominantemente, reubicación dinámica.

►

El SO mantiene una lista de huecos, y asigna memoria

según una determinada estrategia:

First-fit: selecciona el primer hueco suficientemente grande.

Best-fit: selecciona el hueco más pequeño de tamaño suficiente.

► Hay

que explorar toda la lista, salvo que esté ordenada por tamaño.

► Tiende a generar huecos pequeños, cuyo rastreo es comparativamente

costoso.

Worst-fit: selecciona el hueco más grande.

► Hay

que explorar toda la lista, salvo que esté ordenada por tamaño.

► Pretende crear huecos grandes.

Compactación

►

La fragmentación externa en MVT puede ser grande, y en

general aumenta con el tiempo.

Caso extremo: un hueco desperdiciado entre cada dos procesos.

►

El problema se alivia con compactación, desplazando

procesos en un sentido y huecos en otro.

El desplazamiento obliga a detener la computación.

Se necesita reubicación dinámica.

¿Cuándo compactar?

► Cuando

un proceso no pueda alojarse en memoria.

► De modo preventivo, cuando se exceda un determinado nivel de

fragmentación.

► Cuando se realice algún intercambio.

Paginación

Paginación

►

►

►

El espacio lógico de los

procesos se divide en

páginas de tamaño fijo.

La memoria se divide en

marcos, del mismo tamaño

que las páginas.

Las páginas se asignan a

marcos, posiblemente de

manera no contigua.

P1

Pág. 1

Pág. 3

Pág. 2

Pág. 1

Pág. 2

P2

Pág. 2

Pág. 1

Pág. 2

Pág. 3

Pág. 1

Hardware de paginación

Las direcciones lógicas se descomponen en número de página (p) y

desplazamiento dentro de la misma (d).

► La MMU vincula números de página a marcos concretos de la memoria

física.

►

CPU

Dir. lógica

p

d

Dir. física

m

d

MP

SÍ

PTBR

V

m

Tabla de páginas

V=1

NO

TRAP

Observaciones

► El

tamaño de páginas y marcos es potencia de 2.

► Igual número de bits para p y para m: los

procesos no pueden direccionar más memoria que

la que hay.

► Hay una tabla de páginas para cada proceso.

► Cuando hay pocas páginas, las tablas pueden

alojarse en registros de la CPU. Lo habitual, sin

embargo, es almacenarlas en la propia memoria.

En memoria, cada entrada de la tabla ha de ocupar un

número entero de palabras.

Puntos fuertes

►

No hay fragmentación externa, y la asignación de memoria

es trivial.

Cualquier marco libre es igualmente bueno.

►

La fragmentación interna se reduce a la última página de

cada proceso.

Mejor aprovechamiento de la memoria cuanto más pequeñas sean

las páginas.

► Caso

peor: (1 página - 1 palabra) × número de procesos.

► En media: (½ página) × número de procesos.

►

Se facilita la compartición: varios procesos pueden acceder

a un mismo marco.

El código compartido debe ser reentrante (i.e. no debe

automodificarse).

Puntos débiles

►

Si las tablas de páginas se alojan en memoria, se duplica el

tiempo de acceso efectivo a la misma.

Solución: una caché especial para entradas de las tablas de páginas

(Translation Lookaside Buffer, TLB).

►

Las tablas de páginas pueden ocupar un espacio

considerable.

Ejemplo: memoria de 4GB, páginas de 4KB y 4 bytes por entrada

Æ tablas de 4MB por proceso.

Parece recomendable un tamaño de páginas grande, para que las

tablas tengan pocas entradas.

► Compromiso

Soluciones:

► Paginación

con la fragmentación interna.

multinivel.

► Tabla de páginas invertida.

Paginación en 2 niveles

Dir. lógica

CPU

p1

Dir. física

p2

d

m2

d

MP

PTBR

V

V

m2

m1

TP Interna

TP Externa

►

A menudo, los procesos no utilizan todas las páginas del espacio lógico.

Las páginas no utilizadas se pueden condensar en entradas de la TPE con V=0.

Ejemplo (continúa):

►

►

►

►

Memoria de 4GB y páginas de 4KB

4 bytes por entrada en TPE y TPI

10 bits para p1 y 10 para p2

Procesos de 12 MB

16KB en tablas por proceso

Observaciones

► El

número de bits de p2 se ajusta para aprovechar

al máximo el marco de cada TPI.

► Si las tablas de páginas se alojan en memoria, se

triplica el tiempo de acceso efectivo a la misma.

► Se pueden compartir TPIs.

► La idea es generalizable a más de 2 niveles.

Tabla de páginas invertida

►

Una única tabla, en memoria, con tantas entradas como marcos.

Cada entrada indica qué página de qué proceso se aloja en el marco

correspondiente.

Dir. lógica

CPU

P

p

Dir. física

d

i

d

P

buscar

Si no se encuentra

nada, TRAP

i

P

MP

p

Tantos accesos a memoria como entradas se recorren en la búsqueda.

Una tabla hash limita la búsqueda a un número reducido de entradas.

► Se dificulta la compartición.

►

Segmentación

Segmentación

► El

espacio lógico de un proceso se concibe como

un conjunto de segmentos de tamaño variable.

Funciones, variables, pila, etc.

► Similar

a la MVT, sólo que los distintos segmentos

de un proceso no tienen por qué estar contiguos

en memoria.

Hardware de segmentación

►

Las direcciones lógicas se descomponen en número de

segmento (s) y desplazamiento dentro del mismo (d).

Tabla de segmentos

long

CPU

s

Dir. lógica

STBR

base

d

MP

≤

NO

TRAP

SÍ

+

Observaciones

► Los

campos long y d tienen igual número de bits.

► El campo base tiene tantos bits como las

direcciones de memoria física.

► No se necesita bit de validez.

La protección la proporciona el campo long.

► Hay

una tabla de segmentos para cada proceso.

► Nuevamente, las tablas suelen almacenarse en

memoria, con cada entrada ocupando un número

entero de palabras.

Puntos fuertes

► Se

divide el espacio lógico en partes

semánticamente definidas.

Optimiza la protección y la compartición.

► No

hay fragmentación interna.

Puntos débiles

► Se

duplica el tiempo de acceso efectivo a la

memoria.

Solución: una caché especial para entradas de las tablas

de segmentos.

► Las

tablas de segmentos pueden ocupar un

espacio considerable.

► Hay fragmentación externa.

Política de asignación first-fit, best-fit o worst-fit.

Compactación.

Reducir el tamaño medio de los segmentos aumentaría

el espacio consumido en tablas.

Segmentación paginada

Segmentación paginada

► Combinación

de segmentación y paginación.

Los segmentos se dividen en páginas y se

meten en marcos.

► Se

mantiene la visión natural del espacio

lógico de los procesos.

► Se trivializa la asignación (cualquier marco

es igualmente bueno), y se elimina la

fragmentación externa.

Hardware de segmentación paginada

►

El desplazamiento dentro del segmento se descompone en un número

de página (p) y un desplazamiento dentro de ésta (d’).

Tabla de segmentos

long

STBR

base

m

CPU

s

Dir. lógica

d

MP

≤

NO

TRAP

SÍ

p

d’

m

d’

Observaciones

► Una

tabla de segmentos por proceso, y una tabla

de páginas por segmento.

► Se introduce fragmentación interna, en la última

página de cada segmento.

► Con todas las tablas en memoria, se triplica el

tiempo efectivo de acceso a la misma.

► En comparación con la segmentación, aumenta el

espacio consumido en tablas.

► La

paginación segmentada (paginación

segmentando la tabla de páginas) tiene poco

sentido práctico, y apenas se usa.

Memoria virtual

Memoria virtual

Conjunto de técnicas que permiten ejecutar procesos que no se

encuentran completamente cargados en memoria.

► Principio de cercanías: las referencias a memoria tienden a agruparse.

►

Ejecución de instrucciones en secuencia, acceso a tablas, bucles, etc.

Direcciones accedidas

localidad(t1)

►

t1

t

Muchos programas contienen código para opciones poco utilizadas,

que no hay por qué tener siempre en memoria.

Memoria virtual

►

Las partes de un proceso que no se estén utilizando en un

momento dado pueden guardarse en almacenamiento

secundario (típicamente, en un disco duro).

Se cargan y descargan partes según sea necesario.

►

Cada proceso ocupa menos memoria Æ se puede

incrementar el grado de multiprogramación y el

aprovechamiento de la CPU.

En teoría, para ejecutar un proceso llega con tener en memoria la

siguiente instrucción y los datos que ésta vaya a utilizar.

En la práctica, se intenta aproximar la localidad del proceso.

Conjunto residente: parte del espacio lógico de un proceso que se

encuentra en la memoria principal.

Memoria virtual

► Los

procesos no están limitados por el tamaño de

la memoria principal.

Antes, para ejecutar procesos muy grandes se recurría a

la programación de superposiciones (overlays).

► Esta

técnica ha quedado relegada a sistemas empotrados y/o

de tiempo real.

► Al

no tener que cargar o intercambiar procesos

enteros, se reduce la carga de E/S.

Inconvenientes

► Complejidad

elevada:

¿Cómo repartir la memoria entre los procesos?

¿Cuántos procesos pueden residir en memoria

simultáneamente?

¿Qué partes de los procesos cargar o

descargar?

► Rendimiento:

Los accesos a disco son un cuello de botella.

Esquemas de memoria virtual

► Se

puede implementar memoria virtual con

cualquier esquema de reubicación dinámica

y asignación no contigua.

Más fácil con esquemas que paginan la

memoria.

Los algoritmos se complican con segmentos de

tamaño variable.

► El

esquema más frecuente es la

paginación bajo demanda.

Paginación bajo

demanda

Paginación bajo demanda

► Paginación

+ paginador perezoso.

No se carga una página en memoria hasta que una

instrucción necesita acceder a ella.

Proceso

MP

Disco

A

B

A

C

D

A

C

E

D

Memoria

virtual paginada

E

B

C

Soporte hardware

► La

traducción de direcciones lógicas sigue el

mismo esquema que la paginación…

… sólo que puede haber más bits en el campo p

de la dirección lógica.

► Las

páginas en memoria y las que están en

disco se distinguen con el bit de validez:

1 Æ página válida y cargada en memoria.

0 Æ página inválida o válida pero no cargada.

Soporte hardware

Proceso

A

B

C

D

E

Tabla de páginas

MP

Disco

1 1

0 1 3

A

0 0 0 0 -

A

C

D

B

C

E

0 -

Al encontrar V=0, el SO comprueba si se trata de un acceso inválido o

un fallo de página en la rutina de atención a la TRAP.

► A menudo, las entradas con V=0 contienen la dirección de disco donde

se almacena la página correspondiente.

►

Tamaño de la tabla de páginas

►

Con memoria virtual, la tabla de páginas puede volverse

extremadamente grande.

Ejemplo: memoria virtual de 64GB, páginas de 4KB y 4 bytes por

entrada Æ tablas de 64MB (en memoria real) por proceso.

►

Posibles soluciones:

Paginación multinivel:

► Sólo

tiene que estar siempre en memoria la tabla de páginas externa.

► Las tablas de páginas internas pueden alojarse en disco mientras no se

utilizan.

Segmentación paginada:

► Sólo

tiene que estar siempre en memoria la tabla de segmentos.

► Las tablas de páginas de cada segmento pueden alojarse en disco

mientras no se utilizan.

Tabla de páginas invertida:

► El

SO debe mantener tablas con información sobre las páginas que no

están en memoria.

El fallo de página

►

Ante un fallo de página, hay que localizar la página

solicitada en el disco, cargarla en memoria y reiniciar la

instrucción.

Es un proceso de duración potencialmente muy larga y variable,

principalmente por las operaciones de E/S.

►

El repertorio de instrucciones puede plantear ciertos

desafíos, por la dificultad de deshacer los efectos de una

instrucción parcialmente ejecutada.

MOV (R1)+,DIR: copiar en DIR el contenido de la posición de

memoria apuntada por R1, e incrementar R1.

► Si

ocurre un fallo de página al intentar acceder a DIR, hay que

devolver R1 a su valor anterior.

Rendimiento

► tac:

►

►

►

tiempo de acceso sin memoria virtual (en paginación,

doble del tiempo de acceso a una palabra de la memoria).

p: probabilidad de fallo de página.

tfp: tiempo medio de atención a un fallo de página.

Tiempo de acceso efectivo medio:

tef=(1-p)×tac+p×(tfp+tac)

►

Para tac=1μs y tfp=10ms, una degradación

inferior al 10% requiere p<10-5.

Un fallo de página cada 100000 referencias.

Soporte software

► En

la rutina de atención al fallo de página

interviene una cantidad de software considerable:

Reemplazo: si no hay marcos libres cuando se produce

un fallo de página, hay que desalojar alguna de las que

residen en memoria principal.

Gestión del conjunto residente: decidir cuántos marcos

se asignan a cada proceso.

Control de carga: decidir cuántos procesos se pueden

mantener en memoria simultáneamente.

Reemplazo

Reemplazo

► Se

trata de seleccionar una página víctima para

descargar de la memoria, de entre un conjunto de

candidatas.

Pueden ser páginas del mismo proceso (reemplazo

local) o de cualquiera (reemplazo global).

► Los

distintos algoritmos se evalúan sobre cadenas

de referencias, fijando el número de marcos

disponibles.

Intuitivamente, a mayor número de marcos, menor

número de fallos de página.

Algoritmo FIFO

►

FIFO (First In, First Out): se reemplaza la página que lleva

más tiempo en memoria.

Ejemplo: con 3 marcos disponibles, la cadena de referencias

(5,0,1,2,0,3,0,4,2,3,0,3,2,1,2,0,1,5,0,1) produce 15 fallos de

página.

5 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 5 0 1

M0

5 5 5 2 2 2 2 4 4 4 0 0 0 0 0 0 0 5 5 5

M1

- 0 0 0 0 3 3 3 2 2 2 2 2 1 1 1 1 1 0 0

M2

- - 1 1 1 1 0 0 0 3 3 3 3 3 2 2 2 2 2 1

Algoritmo FIFO

► Ventaja:

muy fácil de implementar.

► Inconvenientes:

El instante de carga no es una medida de uso:

la página sacrificada podría volver a necesitarse

pronto.

Anomalía de Belady: existen cadenas de

referencias tales que con m marcos se producen

menos fallos de página que con m+1.

La anomalía de Belady

►

►

►

Con 3 marcos, la cadena

(1,2,3,4,1,2,5,1,2,3,4,5)

produce 9 fallos de página.

Con 4 marcos, en cambio,

produce 10.

Los algoritmos que no

exhiben este

comportamiento se

denominan algoritmos de

pila.

1 2 3 4 1 2 5 1 2 3 4 5

M0

1 1 1 4 4 4 5 5 5 5 5 5

M1

- 2 2 2 1 1 1 1 1 3 3 3

M2

- - 3 1 1 2 2 2 2 2 4 4

1 2 3 4 1 2 5 1 2 3 4 5

M0

1 1 1 1 1 1 5 5 5 5 4 4

M1

- 2 2 2 2 2 2 1 1 1 1 5

M2

- - 3 3 3 3 3 3 2 2 2 2

M3

- - - 4 4 4 4 4 4 3 3 3

Algoritmo óptimo

►

Idealmente, se debería reemplazar la página que tardará

más tiempo en referenciarse.

El objetivo es retardar el fallo de página todo cuanto sea posible.

En el mismo ejemplo de antes se producen 9 fallos de página.

5 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 5 0 1

M0

5 5 5 2 2 2 2 2 2 2 2 2 2 2 2 2 2 5 5 5

M1

- 0 0 0 0 0 0 4 4 4 0 0 0 0 0 0 0 0 0 0

M2

- - 1 1 1 3 3 3 3 3 3 3 3 1 1 1 1 1 1 1

Algoritmo óptimo

► El

algoritmo óptimo garantiza la tasa de fallos de

página más baja posible para un número de

marcos dado.

► Sin embargo, es difícilmente implementable,

porque requiere conocer cadenas de referencias

futuras.

► Se utiliza como patrón para la evaluación de otros

algoritmos.

Algoritmo LRU

►

LRU (Least Recently Used): se reemplaza la página que

lleva más tiempo sin referenciarse.

Por el principio de cercanías, se toma el pasado reciente como una

aproximación del futuro inmediato.

En el ejemplo se producen 12 fallos de página.

5 0 1 2 0 3 0 4 2 3 0 3 2 1 2 0 1 5 0 1

M0

5 5 5 2 2 2 2 4 4 4 0 0 0 1 1 1 1 1 1 1

M1

- 0 0 0 0 0 0 0 0 3 3 3 3 3 3 0 0 0 0 0

M2

- - 1 1 1 3 3 3 2 2 2 2 2 2 2 2 2 5 5 5

Algoritmo LRU

► LRU

es un algoritmo de pila, que suele dar una

buena aproximación del algoritmo óptimo.

► Inconveniente: implementaciones costosas.

Contador de referencias a página:

► En

cada referencia, el valor del contador se copia en la entrada

correspondiente de la tabla de páginas.

► Se reemplaza siempre la página cuya entrada en la tabla tiene

el valor más pequeño.

► El desbordamiento provoca transitorios de rendimiento muy

pobre Æ aumentar el número de bits del contador.

Pila de referencias:

► En

cada referencia se extrae la página correspondiente de la

pila y se pone en la cima.

► Se reemplaza siempre la página que está en la base de la pila.

Algoritmo de la 2ª oportunidad

► Aproximación

de LRU por medio de 1 solo bit.

Cada vez que se referencia una página, se pone R=1 en

la entrada correspondiente de la tabla de páginas.

► 2ª

oportunidad = FIFO + bit R.

Al recorrer la cola, se examina el bit R:

► Si

R=0, se reemplaza la página.

► Si R=1, se pone R=0 y se pasa la página al final de la cola.

► Si

R=1 en todas las páginas, el algoritmo de la 2ª

oportunidad degenera en FIFO.

Aún así, el rendimiento suele ser considerablemente

mejor.

Dirty bit

►

Se puede añadir un bit M (dirty bit), que se activa cuando

se modifica el contenido de la página correspondiente.

►

Para valores iguales del bit R, es mejor sacrificar una página con

M=0 porque no hay que escribirla en disco.

Algoritmo de la 2ª oportunidad mejorado:

1. Con FIFO como base, se selecciona para reemplazo la primera

página que tenga R=0 y M=0.

2. Si no existe tal página, se busca la primera página con R=0 y

M=1.

•

Durante la búsqueda, se pone R=0 en todas las entradas que se

recorren y se envían al final de la cola.

3. Si aún no se ha encontrado víctima, se repiten los pasos 1 y 2.

Gestión del conjunto

residente y control de carga

Gestión del conjunto residente y

control de carga

► ¿Cuántos

marcos asignar a un proceso?

El mínimo lo determina el repertorio de instrucciones.

► E.g.

ADD /DIR1,/DIR2,/DIR3 puede necesitar 4 marcos:

1 para la propia instrucción, 1 para cada sumando y 1 para el

resultado.

El máximo lo fija el tamaño de la memoria principal.

Políticas de asignación:

► Fija:

la asignación se decide en el momento de la carga.

Requiere reemplazo local.

► Variable:

la asignación se decide dinámicamente.

Reemplazo local o global.

► ¿Cuántos

procesos mantener simultáneamente en

memoria?

Hiperpaginación (thrashing)

Si un proceso no dispone de marcos suficientes para su localidad, pasa

más tiempo en fallo de página que ejecutándose Æ hiperpaginación.

► Con asignación fija, la hiperpaginación afecta a procesos aislados.

► Con asignación variable y reemplazo global, se produce a nivel de

sistema cuando la suma de las localidades de todos los procesos no

cabe en la memoria.

►

Utilización de la CPU

En ese caso, la utilización de la CPU cae drásticamente.

hiperpaginación

Grado de multiprogramación

Hay que suspender procesos, descargando su conjunto residente.

Modelo del conjunto de trabajo

define el conjunto de trabajo (working set, WS)

de un proceso como el conjunto de páginas en sus

últimas Δ referencias a memoria.

► Se

2 0 1 3 4 3 2 3 5 1 6 6 1 1 1 5 5 6 6 5 5

Δ

WS={0,1,2,3,4}

Δ

WS={5,6}

WS una aproximación de la localidad del proceso.

Se puede aproximar con interrupciones periódicas, a

partir de los bits R de la tabla de páginas.

Modelo del conjunto de trabajo

► Gestión

del conjunto residente:

Supervisar el conjunto de trabajo de cada proceso y

asignar un número suficiente de marcos.

Descargar las páginas que dejen de pertenecer al

conjunto de trabajo.

► Control

de carga:

Si la demanda total de marcos (Σ WSi) supera el

número de marcos de la memoria, se suspenden

procesos.

En caso contrario, se pueden cargar procesos nuevos.

Frecuencia de fallos de página

► Solución

más directa a la hiperpaginación.

► En vez de supervisar el conjunto de trabajo, se

observa la frecuencia de fallos de página (FFP)

de cada proceso.

► Gestión del conjunto residente:

Si la FFP excede un umbral superior, se asignan más

marcos al proceso.

Si la FFP se reduce por debajo de un umbral inferior, se

le quitan marcos al proceso.

► Control

global.

de carga: ídem, sólo que a partir de la FFP

Fin