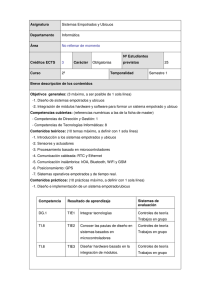

sistemas empotrados - sis-embebidos

Anuncio

SISTEMAS EMPOTRADOS

Optativa de 2º ciclo

Ingeniería Informática

Ingeniería de Telecomunicación

José Luis Villarroel Salcedo

Departamento de Informática e Ingeniería de Sistemas

Centro Politécnico Superior

Universidad de Zaragoza

ÍNDICE

•

•

•

•

•

•

•

•

•

•

•

Introducción

El 68HC08

El TMS320F2812

Herramientas de desarrollo

Gestión del tiempo

Sistemas discretos secuenciales

Sistemas muestreados

Procesos concurrentes

Ejecutivos cíclicos

Prioridades e interrupciones

Núcleos multitarea

1

40

100

157

202

237

298

353

368

410

437

1

SISTEMAS EMPOTRADOS

SISTEMAS EMPOTRADOS

INTRODUCCIÓN

2

SISTEMAS EMPOTRADOS

DEFINICIÓN

Sistema de Tiempo Real: Es un sistema informático en el que es

significativo el tiempo en el que se producen sus acciones.

No basta que las acciones de un sistema sean correctas, sino que,

además, deben ocurrir dentro de un intervalo de tiempo determinado.

Los sistemas tiempo real suelen estar integrados en un sistema de

ingeniería más general, en el que realizan funciones de control,

procesamiento y/o monitorización:

SISTEMAS EMPOTRADOS

(embedded systems)

Ejemplos: Vídeo, lavadora, ABS, …, computadora de vuelo

3

SISTEMAS EMPOTRADOS

EJEMPLO

Computador

de un coche

Km

Km/h

Cont. Velocidad

Tª

Hora

Computador

Control

Empotrado

Calefacción

Aire

Acondicionado

Pedales

Ruedas

Sistema Inyección

4

SISTEMAS EMPOTRADOS

EJEMPLO

Varias tareas:

Control automático de velocidad

Ordenes del conductor:

Control climatización

» comienzo cont. velocidad

Visualización:

» establecimiento temperatura

interior

» velocidad

» rpm

» consumo

» niveles

» alarmas

» ...

» puesta en hora

» ...

5

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Concurrencia

Los componentes del sistema controlado o monitorizado funcionan

simultáneamente

El sistema de control debe atenderlo y generar las acciones de control

o visualización de forma simultánea

Un computador ejecuta sus acciones de forma secuencial

RAPIDEZ

se puede hacer que el computador ejecute sus acciones de forma

aparentemente simultánea

Computadores multiprocesador o sistemas con varios computadores

6

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Fiabilidad y seguridad

Un fallo en un sistema de control puede hacer que el sistema

controlado se comporte de forma peligrosa o antieconómica

Es importante asegurar que si el sistema de control falla lo haga de

forma que el sistema controlado quede en un estado seguro => hay

que tener en cuenta los posibles fallos o excepciones en el diseño

Eficiencia

Gran parte de los sistemas de control deben responder con gran

rapidez a los cambios en el sistema controlado

7

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Interacción con dispositivos físicos

Los sistemas empotrados interaccionan con su entorno mediante

diversos tipos de dispositivos que normalmente no son convencionales

(teclados, impresoras, ...): convertidores A/D y D/A, pwm, entradas y

salidas digitales paralelo y serie, ... (interfases con sensores,

actuadores, periféricos especiales, ...)

Los componentes del software que controlan el funcionamiento de

estos dispositivos (manejadores, "drivers") son, en general,

dependientes del sistema concreto

8

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Robustez

Embarcados en sistemas con movimiento o que pueden ser

transportados, sujetos a vibraciones e incluso impactos (coches,

robots, instrumentación portátil, ...)

No siempre trabajan en condiciones óptimas de temperatura, humedad,

limpieza.

Factor de protección IP: IP65

» Primer dígito: protección ante entrada de sólidos (polvo)

» Segundo dígito: protección ante la entrada de líquidos

9

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Bajo consumo

Muchos de estos sistemas están alimentados con baterías o pilas.

Menor consumo => mayor autonomía

En muchos casos necesidades de bajo voltaje (3V)

Bajo peso

Característica de agradecer en sistemas portátiles

No depende únicamente del computador embarcado y su periferia sino

también de la alimentación (baterías) o de los sensores y actuadores

10

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS

Bajo precio

Aplicable a electrónica de consumo y otros dispositivos con mercados

muy competitivos (p.e. telefonía móvil)

Pequeñas dimensiones

Las dimensiones de un sistema empotrado no dependen sólo de sí

mismo sino también del espacio disponible en el sistema que controla

y/o monitoriza.

Característica a tener muy en cuenta por los problemas que acarrea

11

SISTEMAS EMPOTRADOS

EJEMPLOS

Ejemplos de sistemas empotrados

Electrónica de consumo

» Videos, HIFI, televisión, ...

» Lavadoras, frigoríficos, lavaplatos,

...

Automóviles

» Control velocidad, climatización,

visualización

» ABS, ASR

» Inyección

Telecomunicaciones

» Radios, teléfonos móviles

» GPS

Aviónica, espacial

» Computadores de vuelo, de

misión

» Path-finder

Defensa

» Bombas y misiles inteligentes

» Vehículos, dirección de tiro, ...

Instrumentación

12

SISTEMAS EMPOTRADOS

CLASIFICACIÓN COMPUTADORES

EMPOTRADOS

NO

EMPOTRADOS

PROPÓSITO GENERAL

Supercomputadores

Servidores

Estaciones de trabajo

PC's

Calculadoras

Cálculo científico

Gestión (bancos, empresas)

Bases de datos

TIEMPO REAL

Tarjetas microprocesadores

+ tarjetas E/S + bus

Autómatas Programables

Reguladores digitales

Control industrial

Simuladores de vuelo

Robótica

Tarjetas microprocesadores

+ tarjetas E/S + bus

Microcontroladores, DSPs

Electrodomésticos

Aeronáutica

Teléfonos móviles

13

SISTEMAS EMPOTRADOS

LOS MICROS

Microprocesadores

Propósito general

Potente CPU

Caches y manejo eficiente de memoria

SI

CPU especializada:

•Instrucción MAC

•Manejo buffers, ...

Memoria interna (RAM/ROM)

Periféricos:

•Timers

•Líneas serie alta velocidad

Memoria interna (RAM/ROM)

Periféricos:

•E/S digitales

•Conversores A/D

•PWM

•Timers

•Líneas serie (SCI, SPI)

SI

Memoria externa

Caches

NO

Caches

NO

Microcontroladores

DSPs

Control digital

La CPU no necesita potencia

Todo en un CHIP

Procesado Digital de Señal

Potente CPU especializada

Comunicación con conversores A/D externos

14

SISTEMAS EMPOTRADOS

EL MERCADO

10000

9000

8000

7000

6000

5000

4000

3000

8-bit

2000

4-bit

1000

0

16-bit

91

90

92

93

94

µC

DSP

95

96

97

98

99

SISTEMAS EMPOTRADOS

15

CARACTERÍSTICAS DE LOS µC y DSP

Técnica de fabricación

CMOS: Complementary Metal Oxide Semiconductor

» La inmensa mayoría de los procesadores para sistemas empotrados se

fabrican en esta tecnología

» Menor consumo (alimentación a baterías)

» Mayor inmunidad al ruido

» Son chips casi o totalmente estáticos (no necesidad de refresco) => el reloj

puede ser ralentizado o detenido: seelp mode

SISTEMAS EMPOTRADOS

16

CARACTERÍSTICAS DE LOS µC y DSP

Arquitecturas

Von-Neuman (µC)

» Programa y datos son almacenados en la misma memoria principal. Un

único bus de datos.

» Primero se busca la instrucción y entonces el dato involucrado => Dos

búsquedas en secuencia.

Harvard (µC y DSP)

» Bus de datos y bus de instrucciones separados.

» Arquitectura segmentada => búsquedas en paralelo

» Pre-búsqueda de siguiente instrucción en paralelo con acceso a los datos

de la instrucción en ejecución

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS DE LOS µC y DSP

CISC: Complex Instruction Set Computer

» Muchas instrucciones diferentes. Potentes y especializadas.

» Facilita la programación.

» Código muy compacto

» P.e.: Motorola

RISC: Reduced Instruction Set Computer

» Pocas instrucciones muy sencillas.

» La sencillez de las instrucciones permite liberar área de silicio para

implementar características que mejoren las prestaciones.

» Chips más baratos, de menor consumo, de menos pines.

» P.e.: PIC

17

18

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS DE LOS µC y DSP

Memorias

PROGRAMA

PARÁMETROS

DATOS NO VOLÁTILES

VARIABLES

PILA

ROM

OTP

EPROM

EEPROM

FLASH

EEPROM

FLASH

RAM con batería

RAM

SISTEMAS EMPOTRADOS

19

CARACTERÍSTICAS DE LOS µC y DSP

Máscara

» Memoria ROM

» Programada en fábrica

OTP: One Time Programmable

» Es un dispositivo PROM. En realidad una EPROM sin ventana de borrado.

» Una vez que el programa ha sido grabado no puede ser borrado ni

modificado

» Alternativa a la máscara ROM para series pequeñas

Reprogramación

» El uso de EPROM, EEPROM, EPROM y FLASH para la memoria de

programa facilita el desarrollo y puesta a punto de dispositivos

» El uso de EEPROM, EPROM y FLASH permite la reprogramación del

procesador sin extraerlo del sistema que controla

–

Nuevas versiones, eliminación de errores

SISTEMAS EMPOTRADOS

20

CARACTERÍSTICAS DE LOS µC y DSP

Alimentación

Bajo voltaje

» Alimentación a 5V (µC)

» Alimentación a 3V (µC y DSP)

IDLE/HALT

» Modos de bajo consumo, manteniendo valores de registros, memoria y

salidas

» IDLE: se para la CPU

–

El micro se despierta con una interrupción externa o interna (timers) o

con el RESET

–

Actividad periódica del micro -> timer dedicado a despertar

» HALT: se para todo (CPU, timers, periféricos), el micro se despierta sólo

con una interrupción externa o RESET

SISTEMAS EMPOTRADOS

CARACTERÍSTICAS DE LOS µC y DSP

Entradas / salidas

UART: Universal Asynchronous Receiver Transmitter

» SCI: Serial Comunication Interface.

Synchronous Serial Port

» SPI: Serial Periferal Interface

» McBSP: Multi Channel Buffered Serial Port

I2C: Inter-Integrated Circuit bus

» Bus serie de dos hilos

» Multi-master, multi-slave, detección de colisiones. 128 dispositivos, 10

metros

CAN: Controller Area Network

» Bus con prioridades

21

SISTEMAS EMPOTRADOS

22

CARACTERÍSTICAS DE LOS µC y DSP

Conversión Analógico-Digital (sólo µC, algún DSP)

» Dada la dificultad de integrar circuitos analógicos con digitales no suelen

tener gran precisión

» Normalmente 8 ó 10 bits

Conversión Digital-Analógica (sólo µC , algún DSP)

» No suele estar implementada

» PWM: Pulse Width Modulator. Se usa como técnica de conversión D/A

Contadores de pulsos (sólo µC)

» Cada pulso/evento incrementa un registro acumulador -> número de veces

que ha sucedido el evento

SISTEMAS EMPOTRADOS

23

CARACTERÍSTICAS DE LOS µC y DSP

Interrupciones

Desde los periféricos: timers, UARTS, A/D, E/S paralelo, componentes

externos.

Interrupciones enmascarables -> se pueden activar y desactivar

Interrupciones vectorizadas: una dirección de salto para cada

interrupción

Prioridades

SISTEMAS EMPOTRADOS

24

CARACTERÍSTICAS DE LOS µC y DSP

Características especiales

Watchdog timer

» Si el programa no reinicializa el watchdog antes de un cierto tiempo, éste

procede a hacer el RESET del sistema

Monitor del reloj

» Circuito que detecta si el reloj funciona demasiado despacio => RESET

Monitor

» Programa residente que facilita el desarrollo y la puesta a punto (carga,

break points, ...)

Floating point vs fixed point (DSPs)

25

SISTEMAS EMPOTRADOS

µC POPULARES

8051 (Intel)

Arquitectura Harvard (direccionamiento separado para datos e

instrucciones)

Bus de 8 bits de datos

Puede direccionar 64K de programa (los 4K ó 8K bajos pueden residir

en chip) y 64K de memoria de datos externa. 128 bytes de RAM interna

+ registros especiales. E/S direccionadas en espacio propio.

» Bus de direcciones de 16 bits

Gran potencia en instrucciones de bit

Timers y puertos serie (no A/D ni PWM)

8048 serie baja

80c196 de 16 bits

80186: microcontrolador con un 8086 como núcleo (PC XT)

26

SISTEMAS EMPOTRADOS

µC POPULARES

68HC11 (Motorola)

Arquitectura Von Neuman (datos, programa, E/S, timers comparten el

mismo espacio de memoria)

Bus de 8 bits de datos, 16 bits de direcciones

Pueden tener: EEPROM/OTPROM, RAM, E/S digitales, timers, A/D,

PWM, acumuladores de pulsos, comunicación serie síncrona y

asíncrona

Serie baja 68HC05

683xx: microcontrolador con un 68xxx como núcleo

27

SISTEMAS EMPOTRADOS

µC POPULARES

68HC08 (Motorola)

Arquitectura Von Neuman (datos, programa, E/S, timers comparten el

mismo espacio de memoria)

Bus de 8 bits de datos, 16 bits de direcciones

Pueden tener: ROM/FLASH, RAM, E/S digitales, timers, A/D, PWM,

acumuladores de pulsos, comunicación serie síncrona y asíncrona

Existen elementos de la familia con USB, IIC, CAN

Hasta 60K de Flash, hasta 2K de RAM

28

SISTEMAS EMPOTRADOS

µC POPULARES

PIC (MicroChip)

Arquitectura Harvard (direccionamiento separado para datos e

instrucciones)

» solapamiento de instrucciones

Primer microcontrolador RISC

16Cxx principal línea de la casa

» 35 instrucciones

» 8 bits de datos

» 14 bits de instrucción (hasta 8K instrucciones)

» Pueden tener: EEPROM/OTPROM, RAM, E/S digitales, timers, A/D, PWM,

acumuladores de pulsos, comunicación serie síncrona y asíncrona

29

SISTEMAS EMPOTRADOS

DSPs POPULARES

Las familias de Texas Instruments

C2000

C5000

C6000

Lowest Cost

Efficiency

Performance &

Best Ease-of-Use

Control Systems

Motor Control

Storage

Digital Ctrl Systems

Best MIPS per

Watt / Dollar / Size

Wireless phones

Internet audio players

Digital still cameras

Modems

Telephony

VoIP

Multi Channel and

Multi Function App's

Comm Infrastructure

Wireless Base-stations

DSL

Imaging

Multi-media Servers

Video

30

SISTEMAS EMPOTRADOS

DSPs POPULARES

Familia 6000

(Texas Intruments)

Program

RAM

Data Ram

Addr (32)

Internal Buses

DMA

D (32)

EMIF

.M1 .M2

.L1 .L2

.S1 .S2

Control Regs

CPU

Regs (B0-B15)

Regs (A0-A15)

Ext’l

Memory

.D1 .D2

Serial Port

Host Port

Boot Load

Timers

Pwr Down

31

SISTEMAS EMPOTRADOS

DSPs POPULARES

Familia 6000 (Texas Instruments)

Device

MHz

Kbytes

pins

mm

W

6201B

1600 200

128

352

27

6202

2000 250

384

352

6211

1200 150

72

MHz

6701

6711

TMS320

MIPS

$

Periphs

1.9

80-110

D2H

27

1.9

120-150

D3X

256

27

1.5

20-40

E2H

Kbytes

pins

mm

W

$

Periphs

1000 167

128

352

35

1.9

170-200

D2H

600 100

72

256

27

0.9

20-40

E2H

MFLOPS

Peripherals Legend:

D,E: DMA,EDMA

2,3: # of McBSPs

H,X: HPI, XBUS

32

SISTEMAS EMPOTRADOS

DSPs POPULARES

Familia 2000 (Texas Instruments)

C24x

» 16-bit data Fixed-Point

» SCI, SPI, CAN, A/D, event manager, watchdog timers, on-chip Flash

memory, 20-40 MIPS

C28x

» 32-bit data Fixed-Point

» SCI, SPI, CAN, 12-bit A/D, McBSP, watchdog timers, on-chip Flash

memory, up to 400 MIPS

33

SISTEMAS EMPOTRADOS

DSPs POPULARES

Otros fabricantes importantes:

Analog Devices (www.analog.com/dsp)

» ADSP-21xx 16 bit, fixed point

» ADSP-21xxx 32 bit, floating and fixed point

Lucent Technologies (www.lucent.com)

» DSP16xxx 16 bit fixed point

» DSP32xx 32 bit floating point

Motorola (www.mot.com)

» DSP561xx 16 bit fixed point

» DSP560xx 24 bit, fixed point

» DSP96002 32 bit, floating point

SISTEMAS EMPOTRADOS

LENGUAJES DE PROGRAMACIÓN

Ensamblador

Permiten el uso eficiente de los recursos

Programación costosa y casi imposible la modificación

» El código debe ser documentado, empleo de símbolos

» Programación estructurada

Lenguajes de alto nivel

Desarrollo más rápido, mantenimiento menos costoso

↓ eficiencia

↑ ocupación en memoria

Ada --> grandes sistemas empotrados

C --> ¡La estrella!

» Permite el acceso a los recursos hardware

34

35

SISTEMAS EMPOTRADOS

LENGUAJES DE PROGRAMACIÓN

Uso de C y Ensamblador

Programación en C

» Puesta a punto de la lógica del

programa

Reescritura de algunas partes

críticas en ensamblador

» Disminución de la ocupación de

memoria

Fuente

Ensamblador

Fuente C

Compilador

Cruzado

Ensamblador

Cruzado

Objeto

Relocalizable

Objeto

Relocalizable

Librerías

» Aumento de las prestaciones

Fichero

Configuración

Montador de

Enlaces

Ejecutable

No Relocalizable

Cargador

Máscara

Microcontrolador

DSP

SISTEMAS EMPOTRADOS

36

HERRAMIENTAS DE DESARROLLO

Simuladores

Un simulador ejecuta un programa de un microcontrolador o DSP en un

computador de propósito general (p.e. un PC)

Los contenidos de la memoria y registros pueden ser observados y

alterados

No soporta interrupciones reales ni (generalmente) hardware adicional

La velocidad de ejecución es menor que en el procesador real

SISTEMAS EMPOTRADOS

37

HERRAMIENTAS DE DESARROLLO

Tarjetas de evaluación con monitor residente

Elementos básicos:

» Procesador + Hardware periférico básico

» Línea de comunicación

» Conector para enlazar hardware propio

» Programa monitor en ROM

El monitor permite:

» La carga y ejecución de programas

» Visualización y actualización de memoria, breakpoints, ...

Desventajas del monitor residente:

» El monitor se ejecuta en el mismo procesador que el programa del usuario.

» Utiliza recursos del procesador (un puerto de comunicación, una

interrupción y memoria) y ralentiza la ejecución (acceso a memoria y

registros y comunicación)

SISTEMAS EMPOTRADOS

HERRAMIENTAS DE DESARROLLO

Puerto específico en el mismo procesador

Ejemplos

» IEEE Std 1149.1 (IEEE Standard Test Access Port and Boundary-Scan

Architecture)

» Modo monitor en el 68HC08 (MON08)

Puerto específico que permite:

» Test del sistema en línea

» Programación del procesador en línea

» Puesta a punto

Es un recurso específico del procesador para estas tareas

» Puerto al exterior

» Circuitería

» Software de carga, comunicación, ...

38

SISTEMAS EMPOTRADOS

39

HERRAMIENTAS DE DESARROLLO

Emuladores

Hardware que “emula” al procesador y además permite obtener

información y actuar sobre la aplicación sin gastar recursos ni alterar la

evolución temporal

Se comunica por una parte con un computador o terminal (vía RS232 o

similar) y por otra con el sistema que se está desarrollando (mediante

el POD)

40

SISTEMAS EMPOTRADOS

SISTEMAS EMPOTRADOS

El 68HC08

41

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Características básicas

Arquitectura Von Neuman

8MHz frecuencia bus a 5Volt

Bus datos y aritmética 8 bits

Comunicación serie asíncrona

SCI, y síncrona SPI

Modulo de generación de reloj

con PLL

Bus direcciones 16 bits

TBI, interrupción de tiempo real

multiplicación 8x8 rápida

2 módulos temporizadores 16

bits,PWM

división 16/8 rápida

512 RAM, 32K FLASH

Interrupciones vectorizadas, con

prioridades

In-system programming

Conversor A/D de 8 canales y 8

bits, tiempo conversión 17µS

E/S en espacio de memoria

33 pines I/O

» 10 mA todas I/0, 15 mA 5 E/S

» “pull up” programable

Watchdog COP, detección de

bajo voltaje

Alimentación a 3 V ó 5 V

Dos estados de bajo consumo:

WAIT y STOP

42

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Diagrama

bloques

HC08

43

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Mapa de memoria

44

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Low Power Modes

Existen dos modos de ahorro de energía: WAIT y STOP

WAIT

» CPU apagada

» Periféricos continúan funcionando

» Salida del modo: RESET o Interrupción (externa o de los periféricos)

STOP

» CPU apagada

» Periféricos apagados salvo el KBI

» TBM puede quedar activo

» Salida del modo: RESET, IRQ, interrupción del TBM o del KBI

45

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Encapsulados

44 QFP

42 SDIP

40 PDIP

46

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Familia HC08

RAM

128 bytes .. 4096 bytes

Dos tecnologías

» Flash (68HC908)

4K .. 60K

» Máscara ROM (68HC08)

EEPROM

0 bytes .. 1024 bytes

Comunicación serie

Canales en los timers

CAD

406 bytes .. 32 K

SPI, SCI, CAN, USB, I2C

1 .. 8

8 ó 10 bits, 8 a 14 canales

47

SISTEMAS EMPOTRADOS

CPU08

Características básicas

Hasta 8MHz frecuencia

Bus datos y aritmética 8 bits

Bus direcciones 16 bits

» 64K de programa y datos

Multiplicación 8x8 rápida

División 16/8 rápida

16 modos de direccionamiento

Modos de bajo consumo: WAIT y STOP

Puede ejecutar código para el HC05

48

SISTEMAS EMPOTRADOS

CPU08

Conjunto de registros que pueden ser manipulados por el conjunto de

instrucciones:

Acumulador A

Registro índice H:X

Puntero de pila SP, también

registro índice

Contador de programa PC

Registro de códigos

de condición

49

SISTEMAS EMPOTRADOS

CPU08

Modos de direccionamiento:

Inmediato, el valor del operando

» LDA #01

Extendido, la dirección dato

(direcciones > $FF)

» LDA $8001

Directo, la dirección del dato

(direcciones < $FF)

» LDA $01

Relativo, instrucciones de salto

» rango -127..127

» BRA ETIQUETA (salto dentro del

rango)

» código reubicable

» menor tamaño de las instrucciones

Inherente

» TSX H:X ←(SP)+1

indexado la dirección del

operando se calcula sumando un

desplazamiento (offset) a un

registro índice

» indexado sin desplazamiento

LDA ,X ; A ← (X)

» Indexado, desplazamiento 8bits

LDA $2,X; A ← (X+ $2)

» Indexado, desplazamiento 16bits

LDA $8000,X; A ← (X+$8000)

» indexado SP, desplazamiento 8

bits

LDA $1,SP

» indexado SP, desplazamiento 16

bits

LDA $8000,SP

50

SISTEMAS EMPOTRADOS

CPU08

Conjunto de instrucciones

Carga de Registros

LDA Load Accumulator from Memory

LDHX Load Index Register from Memory

LDX Load X (Index Register Low) from Memory

PULA Pull Accumulator from Stack

PULH Pull H (Index Register High) from Stack

PULX Pull X (Index Register Low) from Stack

Salvado de registros

STA Store Accumulator in Memory

STHX Store Index Register

STX Store X (Index Register Low) in Memory

PSHA Push Accumulator onto Stack

PSHH Push H (Index Register High) onto Stack

PSHX Push X (Index Register Low) onto Stack

Transferencia entre registros

TAP Transfer Accumulator to Processor Status Byte

TAX Transfer Accumulator to X (Index Register Low)

TPA Transfer Processor Status Byte to Accumulator

TSX Transfer Stack Pointer to Index Register

TXA Transfer X (Index Register Low) to Accumulator

TXS Transfer Index Register to Stack Pointer

Transferencia memoria - memoria

MOV Move

Incremento/Decremento

INCA Increment Accumulator

INCX Increment X (Index Register Low)

INC Increment

DECA Decrement Accumulator

DECX Decrement X (Index Register Low)

DEC Decrement

Activado/desactivado de bits

BCLR n Clear Bit n in Memory

BSET n Set Bit n in Memory

CLRA Clear Accumulator

CLRX Clear X Index Register Low

CLRH Clear H Index Register High

CLR Clear

CLC Clear Carry Bit

SEC Set Carry Bit

RSP Reset Stack Pointer

51

SISTEMAS EMPOTRADOS

CPU08

Conjunto de instrucciones

Operaciones aritméticas

ADD Add without Carry

AIS Add Immediate Value (Signed) to Stack Pointer

AIX Add Immediate Value (Signed) to Index Register

ASL Arithmetic Shift Left

ASR Arithmetic Shift Right

DAA Decimal Adjust Accumulator

DIV Divide

LSL Logical Shift Left

LSR Logical Shift Right

MUL Unsigned Multiply

NEGA Negate Accumulator(Two?s Complement)

NEGX Negate X Index Register Low (Two?s Complement)

NEG Negate (Two?s Complement)

SBC Subtract with Carry

SUB Subtract

NSA Nibble Swap Accumulator

Operaciones lógicas

AND Logical AND

EOR Exclusive-OR Memory with Accumulator

ORA Inclusive-OR Accumulator and Memory

COMA Accumulator Complement (One's Complement)

COMX X Index Register Low Complement (One's Complement)

COM Complement (One's Complement)

Rotaciones/Desplazamientos

ROLA Rotate Accumulator Left through Carry

ROLX Rotate X Index Register Low Left through Carry

ROL Rotate Left through Carry

RORA Rotate Accumulator Right through Carry

RORX Rotate X Index Register Low Right through Carry

ROR Rotate Right through Carry

Test datos

CMP Compare Accumulator with memory

CPHX Compare H:X with M

CPX Compare X with M

BIT Bit Test

TSTA Test Accumulator for Negative or Zero

TSTX Test X Index Register Low for Negative or Zero

TST Test for Negative or Zero

52

SISTEMAS EMPOTRADOS

CPU08

Conjunto de instrucciones

Salto condicional

BCC Branch if Carry Bit Clear

BCS Branch if Carry Bit Set

BEQ Branch if Equal

BGE Branch if Greater Than or Equal To

BGT Branch if Greater Than

BHCC Branch if Half Carry Bit Clear

BHCS Branch if Half Carry Bit Set

BHI Branch if Higher

BHS Branch if Higher or Same

BIH Branch if IRQ Pin High

BIL Branch if IRQ Pin Low

BLE Branch if Less Than or Equal To

BLO Branch if Lower

BLS Branch if Lower or Same

BLT Branch if Less Than

BMC Branch if Interrupt Mask Clear

BMI Branch if Minus

BMS Branch if Interrupt Mask Set

BNE Branch if Not Equal

BPL Branch if Plus

BRSET n Branch if Bit n in Memory Set

BRCLR n Branch if Bit n in Memory Clear

DBNZ Decrement and Branch if Not Zero

CBEQ Compare and Branch if Equal

Salto incondicional

JMP Jump

JSR Jump to Subroutine

BSR Branch to Subroutine

RTS Return from Subroutine

BRA Branch Always

BRN Branch Never

Varios

NOP No Operation

Interrupciones

RTI Return from Interrupt

SWI Software Interrupt

WAIT Enable Interrupts; Stop Processor

STOP Enable IRQ Pin, Stop Oscillator

CLI Clear Interrupt Mask Bit

SEI Set Interrupt Mask Bit

53

SISTEMAS EMPOTRADOS

Clock Generator Module CGM

Fuente de reloj para el µC:

reloj externo a la frecuencia de trabajo

reloj externo a baja frecuencia + PLL interno multiplicador frecuencia

CGMXCLK

PLL

CGMVCLK

selector

fuente reloj

CGMOUT

÷2

÷2

BUS CLOCK

54

SISTEMAS EMPOTRADOS

Clock Generator Module CGM

Posibilidades del reloj externo

Sin PLL: dc .. 32.8 MHz

Con PLL: 30 KHz .. 1.5 MHz

Frecuencia de BUS

Alimentación de 5V: máximo 8.4 MHz

Alimentación de 3V: máximo 4.1 MHz

Ejemplo de uso de PLL

55

SISTEMAS EMPOTRADOS

Clock Generator Module CGM

Circuito externo para el CGM

Circuito de reloj

Filtro para el PLL

56

SISTEMAS EMPOTRADOS

Interrupciones

Características básicas

16 posibles fuentes de interrupción

SWI

interrupción software

Reset

Vectorizadas

» 18 vectores diferentes

» Tabla de interrupciones en dirección fija: al final del espacio de

direccionamiento: $FFDC..$FFFF

Enmascarables salvo SWI y RESET

Se pueden habilitar de forma individual

57

SISTEMAS EMPOTRADOS

Interrupciones

RESET

Fuentes

» Encendido (Power-ON Reset, POR)

» Pin RESET externo: RST

» Watchdog COP

» Low Voltaje

» IIegal opcode

» Ilegal address

Acciones

» Detiene la ejecución de la instrucción en curso

» Inicializa el valor de ciertos registros

» Carga en el PC el contenido del vector de RESET ($FFFE-$FFFF)

» Selecciona el reloj externo ÷4 como reloj de BUS

58

SISTEMAS EMPOTRADOS

Interrupciones

Fuentes de Interrupciones

Línea IRQ externa

Internas de los periféricos

» Timer, TBM, CGM

» E/S: SCI, SPI, Keyboard, ADC

Interrupción por programa SWI

Habilitación de interrupciones

El bit I del CCR indica si la CPU atiende interrupciones

» I = 1, no se atienden. SEI, pone el bit a 1

» I = 0, se atienden. CLI, pone el bit a 0

» enmascaradas en reset para poder fijar el puntero pila

Cada interrupción dispone de una bandera individual que permite

enmascararla

59

SISTEMAS EMPOTRADOS

Interrupciones

Cada interrupción tiene una bandera que indica si hay petición

IF1-IF16 de los registros INT1, INT2, INT3

IFx=1 indica interrupción pendiente

IFx=0 indica interrupción no pendiente

Sólo lectura

INT1

INT2

INT3

60

SISTEMAS EMPOTRADOS

Interrupciones

Secuencia en una interrupción

espera fin instrucción curso (peor caso DIV, 7 ciclos)

Apilar registros de la CPU: PC, A, X, CCR

» NO se apila H (parte alta del registro de índice)

Enmascarar interrupciones (I = 1)

» Por defecto las interrupciones no se anidan

Cargar en el PC el vector de la interrupción pendiente más prioritaria

Ejecución del código de la rutina de interrupción

En el RTI se desapilan los registros de la CPU

» Se retoma el I (se vuelven a habilitar las interrupciones)

» Se retoma el PC (se reanuda el programa interrumpido en la siguiente

instrucción)

61

SISTEMAS EMPOTRADOS

Interrupciones

Orden de apilamiento de los registros de la CPU

62

SISTEMAS EMPOTRADOS

Interrupciones

Prioridades

Las prioridades de las interrupciones son fijas

Al acabar la instrucción actual se comprueba cuales son las

interrupciones pendientes y se ejecuta la más prioritaria

Anidamiento de interrupciones

» Debe hacerse con cuidado

» El salto a interrupción enmascara interrupciones. Normalmente no se

anidan.

» Si se permite el anidamiento de interrupciones TODAS las interrupciones

habilitadas interrumpen, independientemente de su nivel de prioridad

respecto de la interrumpida

63

SISTEMAS EMPOTRADOS

Interrupciones

Tabla resumen propiedades de interrupciones

Source

Reset

SW Iinstruction

IRQ pin

CGM(PLL)

TIM1 channel 0

TIM1 channel 1

TIM1 overflow

TIM2 channel 0

TIM2 channel 1

TIM2 overflow

SPI receiver full

SPI overflow

SPI modefault

SP transmitter empty

SCI receiver overrun

SCI noise fag

SCI raming error

SCI parity error

SCI receiver full

SCI input idle

SCI transmitter empty

SCI transmission complete

Keyboard pin

ADC conversion complete

Timebase

Flag

None

None

IRQF

PLLF

CH0F

CH1F

TOF

CH0F

CH1F

TOF

SPRF

OVRF

MODF

SPTE

OR

NF

FE

PE

SCRF

IDLE

SCTE

TC

KEYF

COCO

TBIF

Mask

None

None

IMASK

PLLIE

CH0IE

CH1IE

TOIE

CH0IE

CH1IE

TOIE

SPRIE

ERRIE

ERRIE

SPTIE

ORIE

NEIE

FEIE

PEIE

SCRIE

ILIE

SCTIE

TCIE

IMASKK

AIEN

TBIE

INT Register

Flag

Priority VectorAddress

None

0

$FFFE–$FFFF

None

0

$FFFC–$FFFD

IF1

1

$FFFA–$FFFB

IF2

2

$FFF8–$FFF9

IF3

3

$FFF6–$FFF7

IF4

4

$FFF4–$FFF5

IF5

5

$FFF2–$FFF3

IF6

6

$FFF0–$FFF1

IF7

7

$FFEE–$FFEF

IF8

8

$FFEC–$FFED

IF9

9

$FFEA–$FFEB

Code Warrior

Int Num

1

2

3

4

5

6

7

8

9

10

IF10

IF11

10

11

$FFE8–$FFE9

$FFE6–$FFE7

11

12

IF12

12

$FFE4–$FFE5

13

IF13

13

$FFE2–$FFE3

14

IF14

IF15

IF16

14

15

16

$FFE0–$FFE1

$FFDE–$FFDF

$FFDC–$FFDD

15

16

17

64

SISTEMAS EMPOTRADOS

Interrupciones

Interrupción externa IRQ

Pin IRQ

Registro de control y estado

» Dos modos seleccionables

MODE

–

MODE = 1 interrupción en flanco de bajada y en nivel bajo

–

MODE = 0 interrupción en flanco de bajada

» Bits de ACK, IRQF y IMASK (máscara)

Pullup interno siempre conectado

65

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas

33 pines I/O todos bidireccionales

Organizados en 5 puertos

A,B,C,D,E

pines alta intensidad

» Todos los pines a “1” pueden

suministrar 10mA

» Hay límite en la intensidad total

suministrada por todos los pines

de un puerto y por todos los

puertos

» Los pines PTC0-PTC4 pueden

absorber 15mA

compartidos con otros periféricos

puertos A,C,D con pull-up

programable

» Ejemplo PTA

66

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas

puerto pines

E/S

reg

E/S

reg

reg

dirección pull up

función

alternativa

A

0-7

PTA

DDRA

PTAPUE

KBI

keyboard interrupt

module

B

0-7

PTB

DDRB

-

ADC

conversor

analógico-digital

C

0-6

PTC

DDRC

PTCPUE

-

D

0-7

PTD

DDRD

PTDPUE

TIM

temporización

SPI

Serial Periferial

Interface

E

0-1

PTE

DDRE

-

SCI

Línea Serie Asíncrona

67

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas

Puerto A (similarmente B, C, D, E)

8 pines bidireccionales

Registro de datos PTA

Registro de dirección de los pines

(entrada o salida) DDRA

» DDRAx = 1 pin x configurado

como salida

» DDRAx = 0

pin x configurado

como entrada

Registro de habilitación de los

pullup PTAPUE

» PTAPUEx = 1

pullup habilitado

» PTAPUEx = 0

deshabilitado

68

SISTEMAS EMPOTRADOS

KBI, módulo de interrupción de teclado

Asociado al puerto A

Diseñado para detectar pulsadores en los pines PTA0-PTA7

Sensible al nivel bajo

“ceros”

Puede generar interrupciones

» el banderín KEYF indica pulsación pendiente

» si IMASKK = 0, KEYF provoca interrupción

Puede seleccionarse qué pines son sensibles con el registro INTKBIER

» KBIEx = 1

pin PTAx configurado como entrada y con pullup

Detección del valor de pines

» configuración pin de entrada con DDRA

» lectura de PTA

SISTEMAS EMPOTRADOS

KBI, módulo de interrupción de teclado

69

70

SISTEMAS EMPOTRADOS

KBI, módulo de interrupción de teclado

Modo sensible únicamente a flancos de bajada

» MODEK=0

» Detecta cualquier flanco de bajada si el resto de los pines está a 1

» Un flanco de bajada cuando un pin ya está a 0 no genera un nuevo KEYF

» Borrado KEYF

–

salto a interrupción

–

escribir “1” en ACKK

Modo sensible a flancos de bajada y nivel bajo

» MODEK =1

» KEYF a 1 mientras un pin esté a 0

» Borrado KEYF

–

salto a interrupción

–

escribir “1” en ACKK

y todos los pines del PTA a “1”

71

SISTEMAS EMPOTRADOS

Convertidor A/D

Características

Un solo convertidor, 8 canales multiplexados

Precisión 8 bits, aproximaciones sucesivas

Tiempo de conversión: 17 ciclos ≈1MHz clock, 17µS

Modos

» Conversión contínua

» Conversión única

Flag indica fin de conversión. Puede generar interrupciones

VREFL ≤ V ≤ VREFH

» Conversión lineal

$00 ≤ CONVERSION ≤ $FF

72

SISTEMAS EMPOTRADOS

Convertidor A/D

Registro de control y estado ADSCR

AIEN

Habilitación de las interrupciones

» AIEN = 1 habilitadas

» AIEN = 0 deshabilitadas

ADCO

Conversión continua

» ADCO = 1 conversión continua

» ADCO = 0 una única conversión

COCO

Conversión completa

» AIEN =1, interrupciones habilitadas

COCO debe ser forzado a “0” para

permitir el servicio de las interrupciones

» AIEN =0, interrupciones deshabilitadas

COCO bit de sólo lectura

–

Se pone a 1 al final de una conversión

–

Se borra escribiendo en ADSCR o leyendo ADC

73

SISTEMAS EMPOTRADOS

Convertidor A/D

Registro de control y estado ADSCR

ADCH4–ADCH0

entrada

ADCH4-ADCH0

Selección

canal de conversión

00000

PTB0/AD0

00001

PTB1/AD1

Comienzo de conversión

00010

PTB2/AD2

00011

PTB3/AD3

00100

PTB4/AD4

00101

PTB5/AD5

00110

PTB6/AD6

00111

PTB7/AD7

11101

Vrefh

11110

Vrefl

11111

ADC off

» Escritura del ADSCR

Registro de datos ADC

74

SISTEMAS EMPOTRADOS

Convertidor A/D

El ADC necesita una entrada de reloj en el intervalo [0.5,2.1] MHz.

(Aconsejado 1 MHz)

Registro de control del reloj del ADC

ADCLK

ADIV2-ADIV0 definen el divisor de la frecuencia fuente de reloj

ADICKL- Selecciona la fuente de frecuencia de reloj

» ADICKL = 0

Bus clock

» ADICKL = 1

CGMXCLK (reloj externo)

75

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Características generales

Dispone de 2 “timer” independientes TIM1 y TIM2

Cada TIM dispone a su vez de 2 canales

Para cada timer

» Basado en un contador de 16 bits

» Preescalado programable del reloj de entrada

» 2 canales, para cada canal

–

input capture

–

output compare

flanco subida, flanco bajada o cualquier cambio

activar, desactivar o cambiar una patilla

» generar interrupciones canal1, canal2 o desbordamiento contador

Comparte el patillaje con el PTD

76

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Diagrama de bloques

de un TIM

77

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Contador

T1CNTH, T1TCNTL parte alta y baja del TIM1, sólo lectura

» Lectura de T1CNTH congela el valor de T1CNTL hasta que es leído

Admite reset (TRST en T1SC) y parada (TSTOP en T1SC)

El contador TCNT es modular y cuenta hacia arriba

» Empieza en $0000

» Cuando TCNT = TMOD

TCNT = $0000

78

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Preescalado programable con PS2-PS0

para bus clock 2.4575MHz

divisor

resolución µs

desbordamineto ms

PS2-PS0

1

0,407

26,7

000

2

0,814

53,3

001

4

1,628

106,7

010

8

3,255

213,3

011

16

32

64

6,510 13,021 26,042

426,7 853,3 1706,7

100

101

110

79

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Registro de módulo

T1MODH, T1MODTL parte alta y baja del valor de overflow

80

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Registro de estado y control TSC

TOF indica que se ha producido overflow.

» Borrado, leer TSC cuando TOF=1 y después escribir “0” en TOF

TOIE

habilitación de interrupciones

» TOIE=1 interrupciones habilitadas

» TOIE=0 interrupciones deshabilitadas

TSTOP

TRST

parada del contador del TIM

reset del TIM (contador y preescalado)

81

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Cada canal del TIM channel0 y channel1 puede ser configurado como input

capture y output compare

x puede indicar canal 0 ó 1

input capture

El cambio de

nivel de tensión de un pin

» congela el valor del T1CNT en 2

registros T1CHxH: T1CHxL

output compare

cuando

T1CNTH:T1CNTL coincide con el

valor almacenado en T1CHxH:

T1CHxL :

» activa un banderin CHxF

» se activa un banderín CHxF

» podría provocar una interrupción

» podría provocarse una

interrupción

aplicaciones

» medida precisa instante evento

» medida de intervalos

» medida de frecuencia

» interrupción externa adicional

» puede cambiarse la tensión de

salida de un pin

aplicaciones

» generación de ondas periódicas

» generación de pulsos

» Generación de interrupciones

dependientes del tiempo

82

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Función INPUT CAPTURE

CHxIE, habilitación de

interrupciones

CHxF, Chanel x Flag

» CHxF = 1

activo

ha ocurrido un flanco

» Borrado: lectura de TSCx con

CHxF activo y después escritura

de un 0

MSxB:MSxA

00

00

00

ELSxB:ELSxA

01

10

11

» CHxIE = 1

habilitadas

» CHxIE = 0

deshabilitadas

Configuración como input capture

y selección del tipo de flanco

Configuración CHx

Input capture sólo flanco subida

Input capture sólo flanco bajada

Input capture cualquier flanco

83

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Función OUTPUT COMPARE

CHxIE, habilitación de

interrupciones

CHxF, Chanel x Flag

» CHxF = 1 se ha producido la

igualdad TCNT = TCHx

» borrado: lectura de TSCx con

CHxF activo y después escritura

de un 0

MSxB:MSxA

01

01

01

01

ELSxB:ELSxA

00

01

10

11

» CHxIE = 1 habilitadas

» CHxIE = 0 deshabilitadas

Configuración como ouput

compare y selección del tipo de

flanco

Configuración CHx

OC sin actuar sobre pin

Conmutar salida cuando expira

Salida a "0" cuando expira

Salida a "1" cuando expira

84

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Generación de ondas PWM

La conversión D/A se realiza mediante PWM

Se implementa con un OUTPUT COMPARE y el contaje modular del

TCNT actuando sobre las patillas T1CHx

» Tpwm se programa con el overflow de contador, haciendo conmutar T1CHx

» Ton se programa mediante output compare forzando el cero en T1CHx al

expirar la cuenta del output compare

Ton

Toff

Vmáx

V = Vmin + (Vmáx − Vmin )

Vmin

Tpwm

clear on output compare

toggle on overflow

Ton

T

85

SISTEMAS EMPOTRADOS

Módulo TIMER, TIM

Generación de ondas PWM

TOVx (registro TSCx) habilitan el cambio del estado lógico de las

patillas TCHx ante un overflow del TCNT

» Cuando el canal está inicializado como OUTPUT COMPARE

fuerza el cambio del valor del pin asociado en un overflow

TOVx = 1

» En otro caso no tiene efecto

CHxMAX (registro TSCx)

» CHxMAX = 1

el tiempo de ON del PWM es el 100% del periodo

86

SISTEMAS EMPOTRADOS

Línea serie síncrona, SPI

SPI = Synchronous Serial Peripheral Interface

Comparte patillas con el puerto D

Síncrona => envío del reloj

Señales

» MOSI: Master Output Slave Input

» MISO: Master Input Slave Output

» SPSCK: Reloj del SPI

» SS = 0 (slave)

» SS = 1 (master)

87

SISTEMAS EMPOTRADOS

Línea serie síncrona, SPI

Control

SPCR: registro de control

» SPE = 1 (SPI activada)

» SPMSTR = 0 (slave) / = 1 (master)

» CPOL, CPHA: configuración del reloj

» SPRIE

habilitación interrupción de recepción

» SPTIE

habilitación de la interrupción de transmisión completa

88

SISTEMAS EMPOTRADOS

Línea serie síncrona, SPI

Estado y control

SPSCR: registro de estado y control

» SPR0, SPR1: velocidad de transferencia (bits/s)

–

Baud rate = CGMOUT / (2 x BD)

» SPRF

–

Si SPRIE = 1

» SPTE

–

bit que indica que el receptor está lleno

interrupción

bit que indica que el transmisor está vacío

Si SPTIE = 1

interrupción

» OVRF, ERRIE, MODF, MODFEN

estado y control de errores

89

SISTEMAS EMPOTRADOS

Línea serie síncrona, SPI

Registro de datos

SPDR: Dos registros ocupan la misma posición de memoria ($0012)

» Lectura: buffer con el último byte recibido

» Escritura: buffer

registro de desplazamiento

90

SISTEMAS EMPOTRADOS

Línea serie asíncrona, SCI

SCI = Asynchronous Serial Communications Interface

Comparte patillas con el PTE

Full duplex, Baud rate programable

Control de errores

SCDR: registro de datos

» Dos registros separados en la misma posición de memoria ($0018)

» Escritura => transmisión, Lectura => recepción

» Registro con buffer

Transmisión - SCDR

Recepción - SCDR

68HC08

TXD

PTE0

PTE1

RXD

PERIFERICO

91

SISTEMAS EMPOTRADOS

Línea serie asíncrona, SCI

Selección del “Baud Rate”

Registro SCBR

» SCP0, SCP1

» SCR0..2

bits de selección del preescalado

bit de selección del divisor

92

SISTEMAS EMPOTRADOS

Línea serie asíncrona, SCI

Inicialización

SCC1: registro de control

» ENSCI = 1

SCI habilitada

SCC2: registro de control

» TE = 1

habilitación de la transmisión

» RE = 1

habilitación de la recepción

93

SISTEMAS EMPOTRADOS

Línea serie asíncrona, SCI

Interrupciones

Reg. De control SCC2

Reg. De estado SCS1

Interrupción

Flag

Habilit. Borrado flag

Transmisor vacío SCTE

SCTIE

Leer SCS1 (con SCTE=1), escribir en SCDR

Transmisión

completa

TC

TCIE

Automáticamente cuando hay un nuevo dato a

enviar

Receptor lleno

SCRF

SCRIE Leer SCS1 (con SCRF=1), leer SCDR

Receptor vacío

IDLE

ILIE

Leer SCS1 (con IDLE=1), leer SCDR

94

SISTEMAS EMPOTRADOS

Línea serie asíncrona, SCI

Formato de transmisión

Reg. SCC1

» M long. de carácter

–

M=0

8 bits

–

M=1

9 bits

» PEN

habilitación de

paridad

» PTY

tipo de paridad

Reg. SCC3

» R8

bit adicional en

recepción

» T8

bit adicional en

transmisión

95

SISTEMAS EMPOTRADOS

Módulo base de tiempo, TBM

TBM

Time Base Module

Generación de interrupciones periódicas

Frecuencia configurable

96

SISTEMAS EMPOTRADOS

Módulo base de tiempo, TBM

Activación y control

TBIF

Time base interrupt flag

» TBIF = 1

TACK

registro TBCR

interrupción pendiente

Time base ACKnowledge

» Escritura de un “1”

TBIE

TBON

borrado del flag

Habilitación de la interrupción

Habilitación del módulo

97

SISTEMAS EMPOTRADOS

Módulo base de tiempo, TBM

Selección de la frecuencia

registro TBCR

Bits TBR0..TBR2

Ejemplo de selección con un reloj externo de 32 kHz

98

SISTEMAS EMPOTRADOS

Otros módulos

Computer Operating Properly (COP)

Monitor ROM (MON)

Si no se reinicializa antes de un

cierto tiempo provoca un RESET

Permite la puesta a punto de un

programa en el “tarjet”

Mecanismo de seguridad

Programa residente en ROM

Low-Voltage Inhibit (LVI)

Provoca un RESET si la

alimentación desciende por

debajo de un cierto umbral

System Integration Module (SIM)

Controla todas las actividades del

µC

Módulo de integración

Comunicaciones mediante línea

serie (PTA0)

Break Module (BRK)

Permite el uso de un breakpoint

hardware (puesta a punto)

Genera una SWI

Registro de configuración

Habilitación de: COP, LVI,

instrucción de STOP

Configuración de: frecuencia del

COP, LVI, fuente del reloj para la

SCI

99

SISTEMAS EMPOTRADOS

Resumen Interrupciones

Flags y su borrado

Source

Flag

Mask

Enable

Acknowledge bit

IRQ pin

IRQF

IMASK

TIM1 channel 0

CH0F

CH0IE

Read T1SC0 & CH0F=0

TIM1 channel 1

CH1F

CH1IE

Read T1SC1 & CH1F=0

TIM1 overflow

TOF

TOIE

TIM2 channel 0

CH0F

CH0IE

Read T2SC0 & CH0F=0

TIM2 channel 1

CH1F

CH1IE

Read T2SC1 & CH1F=0

TIM2 overflow

TOF

TOIE

SPI receiver full

SPRF

SPRIE

Read SPSCR & read SPDR

SPI transmitter empty

SPTE

SPTIE

Write SPDR

SCI receiver full

SCRF

SCRIE

Read SCS1 & read SCDR

SCI input idle

IDLE

ILIE

Read SCS1 & read SCDR

SCI transmitter empty

SCTE

SCTIE

Read SCS1 & write SCDR

SCI transmission complete

TC

TCIE

Keyboard pin

KEYF

ADC conversion complete

COCO

AIEN

Timebase

TBIF

TBIE

ACK

IMASKK

Borrado flag

Vector fetch/ACK=1

Read T1SC & TOF=0

Read T2SC & TOF=0

Write SCDR

ACKK

Vector fetch/ACKK=1

TACK

TACK = 1

100

SISTEMAS EMPOTRADOS

SISTEMAS EMPOTRADOS

El TMS320F2812

101

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Características básicas:

Frecuencia de bus

MHz

máx. 150

Alimentación 3.3 V

» CPU

1.8 V

Comunicación serie: SPI, SCI,

CAN y McBSP

Conversor AD con 16 canales y

12 bits

Dos event managers

Memoria interna: 128K flash, 1K

OTP ROM, 16K RAM

» Generación PWM

Arquitectura harvard

» Input capture, output compare

» 3 buses (1 programa + 2 datos)

» Bus datos 32 bits

» Bus direcciones:

» Lectura encoders

Tres estados de bajo consumo:

IDLE, STANBY y HALT

Instrucción MAC

–

32 bits (datos)

CPU segmentada

–

22 bits (programa)

Tres Timers de 32 bits

Módulo de generación de reloj

con PLL

Interrupciones vectorizadas con

prioridades

56 pines de entrada/salida digital

SISTEMAS EMPOTRADOS

DESCRIPCIÓN

GENERAL

Diagrama

de bloques

102

SISTEMAS EMPOTRADOS

DESCRIPCIÓN

GENERAL

Mapa de memoria

103

104

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Low Power Modes (modos de bajo consumo)

IDLE

» CPU queda en bajo consumo

» Se puede seleccionar los periféricos que continúan funcionando

» Salida del modo: RESET o interrupción (externa o periférico)

STANDBY

» CPU y periféricos apagados (sin reloj)

» El oscilador, el wachdog y el PLL siguen funcionando

» Salida del modo: RESET, wachdog, señales externas seleccionables e

interrupción externa no enmascarable

HALT

» CPU y periféricos apagados (sin reloj)

» Oscilador y PLL apagados

» Salida del modo: RESET e interrupción externa no enmascarable

» Modo de menor consumo

todo el DSP inactivo

105

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Encapsulados

179-Ball GHH (12x12 mm)

176-Pin PGF LQFP (24x24 mm)

106

SISTEMAS EMPOTRADOS

DESCRIPCIÓN GENERAL

Familia 2000

Parametric

C28x Fixed-Point DSPs

C24x Fixed-Point DSPs

MHz

150

20 - 40

MIPS

150

20 - 40

Special

Instructions/Capabilities

C/C++ Efficient, Code

Compatible with C24x

Devices

Code Compatible with

C28x Devices

Pricing (10kU)

$17.98 to $22.99

$2 to $14.64

Peripherals /Coprocessors

128K or 64K Flash, 12-bit

ADC, Multichanneled

Buffered Serial Port

(McBSP), 2 UARTs, 2

Event Managers,

Enchanced Controller

Area Network (eCAN)

Communication

Controller, SPI, 56 GPIO,

Watch Dog Timer

32K, 16K or 8K Flash, 10bit ADC, SPI, UART, 2

Event Managers,

Controller Area Network

(CAN), Communication

Controller

107

SISTEMAS EMPOTRADOS

C28x CPU

Características básicas

Hasta 150 MHz de frecuencia

ALU de 32 bits, coma fija

MAC y multiplicación de 32x32 bits

resultado de 64 bits

Pipeline de 8 etapas

Buses (harvard)

» Buses de dirección

–

PAB Program address bus (22-bit).

–

DRAB Data-read address bus (32-bit).

–

DWAB Data-write address bus (32-bit).

» Buses de datos

–

PRDB Program-read data bus (32-bit).

–

DRDB Data-read data bus (32-bit).

–

DWDB Data-/Program-write data bus (32-bit).

108

SISTEMAS EMPOTRADOS

C28x CPU

Diagrama de la CPU

Registros

Acumulador ACC (32 b)

8 reg auxiliares XAR0..7 (32 b)

Contador de progr. PC (22 b)

Registro de vuelta RPC (22 b)

Puntero de pila SP (16 b)

Control de interrupciones IFR,

IER, DBGIER (16 b)

Reg. de estado ST0..1 (16 b)

Reg. de producto P, XT (32 b)

Puntero de página DP (16 b)

109

SISTEMAS EMPOTRADOS

C28x CPU

Pipeline

Fetch: F1 (PC

bus direcciones), F2 (lectura instrucción)

Decode: D1, D2

Read: R1 (dirección dato

bus), R2 (lectura dato)

Execute: E

Write: W (escritura del resultado)

110

SISTEMAS EMPOTRADOS

C28x CPU

Modos de direccionamiento

Directo: DP (data page) + desplazamiento de 6 ó 7 bits

Sobre el puntero de pila

» SP + desplazamiento de 6 bits

» Pre-decremento o post-incremento de SP

Indirecto sobre un registro auxiliar

» XARx dirección de un dato

» XARx + desplazamiento de 3 bits

» XARx + desplazamiento XARi

» Post-incremento o pre/post-decremento de XARx

Registro

» Un registro es el origen o destino del dato

111

SISTEMAS EMPOTRADOS

C28x CPU

Conjunto de instrucciones

Para el procesado digital de señal

» Multiplicación

–

16 bits x 16 bits

resultado 32 bits

–

32 bits x 32 bits

resultado

» 32 bits de la parte alta

» 32 bits de la parte baja

» Multiplica y acumula

–

16 bits x 16 bits MAC

resultado 32 bits

–

32 bits x 32 bits MAC

resultado

» 32 bits de la parte alta

» 32 bits de la parte baja

112

SISTEMAS EMPOTRADOS

Reloj y PLL

Fuente de reloj para el DSP

Reloj externo a la frecuencia de trabajo

Reloj externo + PLL multiplicador de la frecuencia

113

SISTEMAS EMPOTRADOS

Reloj y PLL

Posibilidades de reloj externo

20 MHz .. 35 MHz

Posibles conexiones

PLL programado por el registro PLLCR

114

SISTEMAS EMPOTRADOS

Reloj

Se puede

habilitar el

reloj de cada

periférico

independientemente

115

SISTEMAS EMPOTRADOS

Reloj

Habilitación reloj periférico

Peripheral Clock Control (PCLKCR) Register

116

SISTEMAS EMPOTRADOS

Reloj

Preescalado del reloj de los periféricos

Low-Speed Peripheral Clock

Prescaler (LOSPCP) Register

High-Speed Peripheral Clock

Prescaler (HISPCP) Register

117

SISTEMAS EMPOTRADOS

Interrupciones

Características básicas

La CPU soporta

» NMI

interrupción no

enmascarable

» INT1..INT14, RTOSINT,

DLOGINT

16 interrupciones

enmascarables

» Interrupciones software no

enmascarables

Tabla de 128 vectores diferentes

de interrupción

» Sólo 76 efectivas

Reset

Interrupciones software

» 12 de usuario USER0..USER11

(traps)

ILLEGAL

ilegal

código de instrucción

Interrupciones externas a la CPU

» 96 posibles fuentes multiplexadas

en 12 grupos de 8 interrupciones

–

Cada grupo activa una

interrupción de la CPU

(INT1..INT12)

–

41 de los periféricos

–

1 Watchdog

–

2 interrupciones externas

XINT1 y XINT2

–

1 timer 0

–

Resto no conectadas

» Interrupción externa XINT13

NMI o INT13

» Timer 2

INT14 (uso por RTOS)

» Timer 1

INT13 (uso por RTOS)

118

SISTEMAS EMPOTRADOS

Interrupciones

RESET

Fuentes

» Encendido

» Pin de RESET

RS

Acciones

» Detiene todas las operaciones en curso y vacía la pipeline

» Inicializa el valor de ciertos registros

» Carga en el PC el contenido del vector de RESET

–

0x3F FFC0

situado en ROM

–

Salto a InitBoot. Según el estado de algunos pines:

» Salto a la Flash

0x3F 7FF6 (debe contener un salto al

comienzo del programa)

» Salto a H0 SRAM

0x3F 8000

» Salto a la memoria OTP

0x3D 7800

» Ejecución de una rutina de carga

119

SISTEMAS EMPOTRADOS

Interrupciones

Esquema de las

fuentes de interrupción

120

SISTEMAS EMPOTRADOS

Interrupciones

PIE (Periferal Interrupt Expansion)

Multiplexa 96 interrupciones en únicamente 12 (INT1..INT12) que son

entregadas a la CPU

Permite un vector de interrupción individual para cada una

Flag y habilitación individual

121

SISTEMAS EMPOTRADOS

Interrupciones

PIE

122

SISTEMAS EMPOTRADOS

Interrupciones

Habilitación y flags de interrupciones

Máscara general de las interrupciones enmascarables

(registro de estado ST1)

INTM

» INTM = 0 interrupciones globalmente no enmascaradas

–

asm(" clrc INTM

; Enable global interrupts");

» INTM = 1 interrupciones globalmente enmascaradas

–

asm(" setc INTM

; Mask global interrupts");

Dos niveles de habilitación y flags

» Nivel CPU

» Nivel PIE

interrupciones INT1..INT14

96 interrupciones agrupadas en 12 grupos de 8

123

SISTEMAS EMPOTRADOS

Interrupciones

Nivel de CPU

Habilitación

» Registro IER (Interrupt Enable Register)

» INTx = 1

habilitada

Flag

» Registro IFR (Interrupt Flag Register)

» INTx = 1

interrupción pendiente

Ambos registros (16 bits) tienen la misma estructura

124

SISTEMAS EMPOTRADOS

Interrupciones

Nivel PIE

Habilitación global del PIE

ENPIE = 1 en el registro PIECTRL

Agradecimiento de una interrupción de un bloque de 8

» Registro PIEACK

» PIEACKx = 1

interrupción pendiente en el bloque x, no se pasan nuevas

interrupciones a la CPU

» Borrado

escritura por la aplicación de un 1 en el correspondiente bit

125

SISTEMAS EMPOTRADOS

Interrupciones

Nivel PIE

Un registro de habilitación para cada bloque de 8

» PIEIERx (x = 1..12)

» PIEIERx.y = 1

interrupción habilitada

Un registro de flag para cada bloque de 8

» PIEIFRx (x = 1..12)

» PIEIFRx.y = 1

interrupción pendiente

Ambas clases de registros (16 bits) tienen la misma estructura

126

SISTEMAS EMPOTRADOS

Interrupciones

Interrupciones externas

XINT1 y XINT2

» Cada una tiene un registro de habilitación y configuración XINTxCR

» Enable = 1

interrupción habilitada

» Polarity = 0

flanco de bajada

» Polarity = 1

de subida

flanco

NMI

» Registro de configuración XNMICR

» Enable y Polarity idem.

» Select = 0

origen Timer 1

» Select = 1

origen XNMI

127

SISTEMAS EMPOTRADOS

Interrupciones

Respuesta a una interrupción del

PIE

Por defecto no se permiten

interrupciones encajadas

Los flags de la CPU y del PIE

son borrados de forma

automática

El borrado del PIEACKx debe

hacerlo la rutina de

interrupción

La pipeline es vaciada

» Se completan las

instrucciones decodificadas

» El resto se eliminan

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas, GPIO

56 pines I/O todos bidireccionales

Organizados en 5 puertos

A,B,D,E,F,G

Pullup o pulldown interno

Compartidos con otros periféricos

Acciones sobre cada línea

» Set

» Clear

» Toggle

» Read

» Write

Filtrado de ruido

» Qualification

128

129

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas, GPIO

Port

pins

MUX

direc.

qualif.

set

clear

toggle

data

Peripheral

A

16

GPAMUX

GPADIR

GPAQUAL

GPASET

GPACLEAR

GPATOGGLE

GPADAT

EV-A

B

16

GPBMUX

GPBDIR

GPBQUAL

GPBSET

GPBCLEAR

GPBTOGGLE

GPBDAT

EV-B

D

4

GPDMUX

GPDDIR

GPDQUAL

GPDSET

GPDCLEAR

GPDTOGGLE

GPDDAT

EV-A

EV-B

E

3

GPEMUX

GPEDIR

GPEQUAL

GPESET

GPECLEAR

GPETOGGLE

GPEDAT

Ext. Int.

F

15

GPFMUX

GPFDIR

-

GPFSET

GPFCLEAR

GPFTOGGLE

GPFDAT

SPI, SCI,

CAN, McBSP

G

2

GPGMUX

GPGDIR

-

GPGSET

GPGCLEAR

GPGTOGGLE

GPGDAT

SCI

130

SISTEMAS EMPOTRADOS

Entradas/salidas paralelas, GPIO

Puerto A (similarmente B, D, E, F, G)

GPAMUX

» GPAMUXx = 0

GPIOAx (GPIO pin)

» GPAMUXx = 1

Periférico

GPADIR

» GPADIRx = 0

Entrada

» GPADIRx = 1

Salida

GPASET, GPACLEAR, GPATOGGLE

» Escritura BITx = 1

Acción

» Escritura BITx = 0

sin efecto

GPADAT

» Pin de entrada

» Pin de salida

la lectura devuelve el estado lógico del pin

la escritura fuerza el estado lógico del pin

131

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Características generales

Dos módulos independientes e iguales EV-A y EV-B

Funciones de cada módulo

» Input Capture

» Output Compare

» Generación de señales PWM (hasta 8 por módulo)

» Lectura de encoders (Quadrature-Encoder Pulses)

» Generación de periodos de muestreo para el ADC

» Interrupciones diversas

Elementos de cada módulo

» 2 timers (up/down) de 16 bits

–

frecuencia CLOCK_CPU..CLOCK_CPU/128

» Varios registros de comparación

» 2 registros de periodo

» Lógica QEP, unidad de captura

PWM, OC

132

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Interfase

SISTEMAS EMPOTRADOS

Event Manager,

EV-A y EV-B

Estructura

interna

133

134

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Habilitación y configuración de los timers de propósito general

4 timers Tx (x = 1..4)

» T1 y T2 en EV-A

TPS2TPS0

Frec.

Tick

x = 150 MHz

» T3 y T4 en EV-B

000

x/1

6.66 ns

001

x/2

13.3 ns

010

x/4

26.6 ns

011

x/8

53.3 ns

100

x/16

106.6 ns

101

x/32

213.3 ns

110

x/64

426.6 ns

111

x/128

853.3 ns

Cada Tx

» 1 registro contador TxCNT (16 bits)

» 1 registro de periodo TxPR (16 bits)

» 1 registro de control TxCON

–

Preescalado

TPS2-TPS0

–

Modo de operación

–

Habilitación

TMODE1-TMODE0

TENABLE = 1

x = Frecuencia de reloj de la CPU

135

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Modos de operación de los timers de propósito general

TMODE1TMODE0

Modo

Descripción

00

Stop/Hold

Contador parado

01

Continous-Up/-Down

Cuenta hacia arriba hasta el periodo

cuenta hacia abajo hasta 0

sigue

contando hacia arriba

10

Continous-Up

Cuenta hacia arriba hasta el periodo

TxCNT = 0

sigue contando

11

Directional-Up/-Down

Cuenta hacia arriba o hacia abajo

según el valor de del pin TDIRA/B

136

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Interrupciones de los timers de propósito general

Overflow

» Flag

TxCNT = 0xFFFF

T1OFINT (bit 10) del registro EVAIFRA (overflow del T1)

» Habilitación

TxCNT = 0x0000

Underflow

» Flag

T1UFINT (bit 9) del registro EVAIFRA (underflow del T1)

» Habilitación

Period match

» Flag

T1OFINT (bit 10) del registro EVAIMRA (overflow del T1)

T1UFINT (bit 9) del registro EVAIMRA (underflow del T1)

TxCNT = TxPR

T1PINT (bit 7) del registro EVAIFRA (period match del T1)

» Habilitación

T1PINT (bit 7) del registro EVAMFRA (period match del T1)

Borrado de los flags

escribiendo un 1

137

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Función de comparación

Registro

Evento

TxCMPR (16 bits)

TxCNT = TxCMPR

Esta función está asociada a una salida del DSP

» TxPWM_TxCMP

» Cada vez que se produce la igualdad

cambio del valor de la salida

» Cuando el TxCNT alcanza el periodo

cambio del valor de la salida

» Así puede generar un PWM

–

Compare

–

Period

Ton

Periodo del PWM

138

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Función de comparación

Habilitación

» Registro de control del EV-A/-B

–

TCMPOE = 1

–

TxCMPOE = 1

GPTCONA

salidas del módulo A/B sensibles a las comparaciones

salida de comparación del Tx habilitada

» Registro de control TxCON

–

TECMPR = 1

Habilitación de la comparación

Interrupción cuando se produce la comparación

» Flag

T1CINT en EVAIFRA y T2CINT en EVAIFRB (idem para T3 y T4)

» Habilitación

y T4)

T1CINT en EVAIMRA y T2CINT en EVAIMRB (idem para T3

139

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Generación de un periodo de muestreo para el conversor AD

Habilitación y configuración en los registros GPTCONA y GPTCONB

» Pareja de bits TxTOADC

TxTOADC Descripción

00

Activación ADC deshabilitada

01

Toma muestra en underflow de Tx

10

Toma muestra al alcanzar el periodo el Tx

11

Toma muestra en el compare del Tx

140

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

PWM

Además del PWM que puede generar cada GPT

cada módulo posee

tres registros de comparación espacializados en PMW

Cada uno gestiona dos salidas

de la otra)

PWMi y PWMi+1 (una es la inversa

Registros

» Activación

» Comparación

bits CENABLE, FCMPOE, FCNP(1,2,3)OE en COMCON-A/-B

CMPRx

Características adicionales

deadband, generación automática de las

tres fases para motores de alterna

141

SISTEMAS EMPOTRADOS

Event Manager, EV-A y EV-B

Función Input Capture

Tres registros de captura por cada módulo (A y B)

Cada una captura una entrada CAPx (x = 1..3)

del TxCNT

CAP(1,2,3)FIFO

se almacena el valor

Sensible a flancos de subida o de bajada o a ambos

» Configuración

CAPCONA / B

Posibilidad de generación de interrupciones

» Habilitación

» Flags

EV(A,B)IMRC

EV(A,B)IFRC

Función lectura de encoder

Quadrature Encoder Pulse (QEP) Circuit

Multiplexado con la unidad de captura

Control de posición y velocidad de motores

142

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Características generales

12 bits de conversión

1 convertidor

16 canales

Entrada analógica

0..3 V

Tiempo de conversión

» Maximo

200 ns

16 registros de resultado de 16 bits

Autosecuenciamiento de canales

Diversas fuentes de comienzo de conversión

Valor _ Digital = 4095 ×

Voltaje _ entrada − ADCLO

3

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Diagrama de bloques

143

144

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Secuenciadores

Dos grupos de 8 canales independientes

» Cada uno con su sample-and-hold

» Cada uno con su secuenciador

Los dos secuenciadores pueden funcionar independientes (SEQ1 y

SEQ2) o encadenados (SEQ)

Los secuenciadores indican qué canales y en qué orden se convierten

cada vez que se inicia una conversión

Para cada SEQx

» Número de canales a convertir cada vez que se inicia una conversión

MAXCONV

» Orden de los canales

–

CHSELSEQ1

CONV00 – CONV03

–

CHSELSEQ2

CONV04 – CONV07

–

CHSELSEQ3

CONV08 – CONV11

–

CHSELSEQ4

CONV12 – CONV15

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Diagrama

SEQ

145

146

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Dos modos

Conversión continua

se pone los secuenciadores en bucle y las

conversiones no se detienen

Start-stop

A la llegada de un señal de inicio de conversión se

convierten únicamente el número de canales indicado en MAXCONV

Inicio de conversión, SOC

Por software

SEQ1, SEQ2, SEQ

EVA

SEQ1, SEQ

EVB

SEQ2, SEQ

Pin de entrada GPIOE1/XINT2_ADCSOC

Interrupciones

Fin de las conversiones de un secuenciador

SEQ1, SEQ

147

SISTEMAS EMPOTRADOS

Convertidor analógico-digital, ADC

Habilitación y configuración

ADCTRL1

» CONT RUN = 1

modo

conversión continua

» SEQ CASC = 1

en cascada

ADCTRL3

SEQ1 y SEQ2

encendido del ADC

» ADCRFDN = 1, ADCBGDN = 1

5 ms

ADCPWDN = 1

ADC_ST_FLG

» INT SEQx CLEAR

escritura de

un 1

borrado del flag

» INT SEQx

flag

ADCTRL2

» EVB SOC SEQ

habilitación del

SOC del SEQ por EVB

» RST SEQx

RESET del

secuenciador

» SOC SEQx

SOC por software

» INT ENA SEQx = 1

interrupción habilitada

» EXT SOC SEQ1 = 1

SOC por

señal externa habilitada

» EVA SOC SEQ1 = 1

habilitación del SOC de SEQ1 por

EVA

» EVB SOC SEQ2 = 1

habilitación del SOC de SEQ2 por

EVB

148

SISTEMAS EMPOTRADOS

32 bits CPU timers

El DSP posee tres timers adicionales a los de EV-A/-B

TIMER0

utilizable por el usuario

TIMER1 y TIMER2

real

reservados para sistemas operativos de tiempo

Los tres tienen la misma estructura

149

SISTEMAS EMPOTRADOS

32 bits CPU timers

Estructura y funcionamiento

Permiten la generación de interrupciones periódicas

tiempos

base de

150

SISTEMAS EMPOTRADOS

32 bits CPU timers

Configuración

Registro de control

» TIE = 1

» TIF

» TRB

TIMERxTCR

interrupción habilitada

flag de la interrupción

reinicilización del timer al escribir un 1

» TSS = 1

el timer se detiene

151

SISTEMAS EMPOTRADOS

32 bits CPU timers

Programación

Preescalado

TIMERxTPR/TPRH

» Escribir en TDDR y TDDRH el valor del prescalado (número de ticks de

CPU que tiene un tick del timer)

» PSC y PSCH es el contador

Periodo

» Escribir en TIMERxPRD y TIMERxPRDH el valor del periodo (en ticks del

timer)

SISTEMAS EMPOTRADOS

Multichannel Buffered Serial Port, McBSP

Características básicas

Comunicación serie síncrona

Interfase directa con conversores y codecs comerciales

Comunicación full-duplex

128 canales

No DMA

» Colas FIFO de recepción y transmisión de 16 posiciones

Varios tamaños de datos: 8, 12, 16, 20, 24 y 32 bits

Posibilidad de compresión de datos

» A-law

» µ-law

Interrupciones

152

SISTEMAS EMPOTRADOS

Multichannel Buffered Serial Port, McBSP

Diagrama

153

SISTEMAS EMPOTRADOS

Multichannel Buffered Serial Port, McBSP

Comunicación serie síncrona

Tamaño de dato enviado configurable 8, 12, 16, 20, 24 y 32 bits

Los datos de agrupan en tramas de longitud fija

» Frame

» Uno o varios datos

Sincronización en bit (reloj) y en trama

Reloj configurable

154

155

SISTEMAS EMPOTRADOS

Multichannel Buffered Serial Port, McBSP

Comunicación multicanal

Cada trama es dividida en rodajas temporales

» Rodaja

un dato (8, 12, 16, 24, 32 bits)

» Canal = rodaja

La línea serie es multiplexada en el tiempo en diversos canales

Hasta 128 canales

El McBSP puede transmitir o recibir en únicamente los canales activos

156

SISTEMAS EMPOTRADOS

Otros periféricos