Diseño de un amplificador distribuido para Ultra Wide

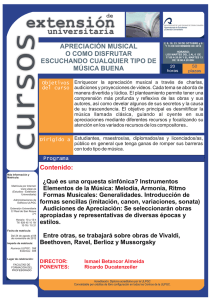

Anuncio