Segmentación

Anuncio

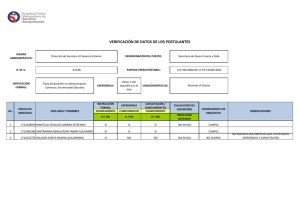

Segmentación: Mejora del rendimiento IEC – UTM Moisés E. Ramírez G. 1 Segmentación La segmentación (pipelining) es una técnica de implementación por la cual se solapa la ejecución de múltiples instrucciones. Es la técnica de implementación clave utilizada para hacer CPU rápidas. 2 1 Ejemplo: lavanderia 1. 2. 3. 4. Colocar la carga de ropa sucia en la lavadora. Sacar la ropa de la lavadora para pasarla a la secadora. Doblar la ropa seca. Acomodar la ropa limpia y seca en su lugar correspondiente. 3 Lavado usando segmentación Cada uno de los pasos en los que se dividió el proceso se conoce como una etapa de la segmentación o un segmento. La segmentación no disminuye el tiempo de ejecución pero si aumenta la productividad, y de esta manera se aumenta el rendimiento. 4 2 Para la ejecución de instrucciones MIPS 1. 2. 3. 4. 5. Atrapar las instrucciones de la memoria. Leer los registro mientras se decodifica la instrucción. Ejecutar la instrucción o calcular una dirección. Accesar un operando en memoriade datos. Escribir el resultado en un registro. 5 Riesgos en la segmentación Riesgos de Estructura: Significa que el hardware no puede soportar la combinación de instrucciones que se quiere ejecutar en el mismo ciclo. Ejemplo: Si contamos con una sola memoria, para datos y código, no será posible escribir o leer un dato, mientras se atrapa una instrucción. Riesgos por dependencias de datos: Una instrucción depende del resultado de una instrucción previa que aún está en la segmentación. Riesgos de Control: Surgen de la necesidad de hacer una decisión basada en los resultados de una instrucción, mientras otras se están ejecutando. Ejemplo: en un brinco condicional, mientras se determina si el brinco se hará o no, otras instrucciones ingresarán al procesador. Si se determina que el brinco no se llevará a cabo, esas instrucciones prosiguen su ejecución. 6 3 Implementación multiciclos vs segmentación Se desean analizar dos implementaciones: multiciclo y segmentado, en la siguiente tabla se muestra el tiempo requerido para cada etapa y tipo de instrucción. La ejecución de 3 instrucciones de carga en la implementación multiciclos, ocupara 800 x 3 = 2,400 ps, la implementación segmentada usa 1,400 ps. 7 Para la segmentación, hay etapas que requieren solo 100 ps, pero todas comparten el mismo ciclo de reloj, entonces cada etapa debe considerar el peor de los casos, que es 200 ps. Para poder calcular el tiempo entre el fin de una y otra instrucción segmentada, (suponiendo condiciones ideales) y compararlo con la versión no segmentada, se tiene que: Tiempo entre instrucciones Tiempo entre instrucciones (segmentadas) (no segmentadas) = Número de etapas de segmentación 8 4 9 Trabajando en condiciones ideales y con un número grande de instrucciones, ¿cuál es el aumento del rendimiento? Supongamos 1,000,000 instrucciones 1e6 * 800ps / 1e6 * 200ps ̴ 4 La segmentación aumenta el throughput (rendimiento) de la implementación, y no necesariamente el tiempo de ejecución de las instrucciones. 10 5 Camino de datos segmentado Previamente se analizaron las implementaciones de un solo ciclo y multiciclos. Las etapas requeridas por cada instrucción son: 1. 2. 3. 4. 5. IF: (Instruction fetch) Captura de la instrucción. ID: (Instruction decode) Decodificación de la instrucción y lectura de registros. EX: (Execution) Ejecución o cálculo de una dirección. MEM: (Memory Access) Acceso a memoria. WB: (Write Back) Retro escritura. 11 Camino de datos de un solo ciclo segmentado 12 6 En la etapa WB se realiza la escritura del resultado en el archivo de registros, el cual está ubicado en la segunda etapa del camino de los datos – Riesgo por dependencia de datos La selección del siguiente valor del PC, seleccionado entre el PC incrementado en cuatro y la dirección destino de un brinco toma lugar en la etapa MEM – Riesgo de control El flujo de datos de derecha a izquierda no afecta a la instrucción actual, pero puede tener influencia sobre las instrucciones siguientes, que ya están en alguna etapa de la segmentación. 13 Formato estilizado para mostrar el camino de datos de instrucciones 14 7 Agregando registros Para no tener que replicar las unidades funcionales, es necesario agregar registros que almacenen temporalmente los datos para las siguientes etapas. 15 Captura de la Instrucción Durante esta etapa la instrucción LW utilizará las unidades funcionales resaltadas en la figura siguiente de la memoria de código sólo se resalta la mitad derecha puesto que ésta será accesada solo para lectura. Al mismo tiempo, en esta etapa se calculará el valor de PC + 4 y se escribirá en el PC para introducir a la siguiente instrucción a la segmentación (aún no se considerarán los riesgos). En el registro IF/ID se escribirá la instrucción, y el valor de PC + 4. Cabe aclarar que en esta etapa, el hardware desconoce el tipo de instrucción. 16 8 Instruction fetch 17 Decodificación de la instrucción y lectura del archivo de registro Para esta etapa los datos que se evalúan se toman del registro IF/ID y los resultados al final de la misma se escribirán en el registro ID/EX. Los aspectos de interés particular para la instrucción LW son: la lectura del registro 1 y la extensión del signo de la constante para que utilice32 bits. También se lee el registro 2, pero este no es importante para la instrucción bajo consideración. 18 9 Instruction decode 19 Ejecución o Cálculo de una dirección Los datos se tomarán del registro ID/EX y los resultados se escribirán en el registro EX/MEM. Lo importante para la instrucción LW es el cálculo de la dirección del dato que se leerá en memoria. En esta etapa ya se tiene identificado el tipo de instrucción por lo que el control deberá colocar como segundo operando de la ALU a la constante extendida en signo. El primer operando, por default corresponde al registro base. 20 10 Execution 21 Acceso a memoria En esta etapa se leerá un dato de memoria, la dirección a leer se toma del registro EX/MEM y el dato leído se escribirá en el registro MEM/WB. En la figura siguiente se resalta solo la mitad derecha de la memoria por que solo se está haciendo una lectura. 22 11 Memory 23 Retro escritura El último paso de la instrucción LW consiste en la escritura del dato que está en el registro MEM/WB en el registro correspondiente, el nombre de retroescritura es por que aunque se esta ejecutando el paso 5, el archivo de registros esta ubicado en la etapa 2. Esto no afecta en la ejecución, puesto que el archivo de registros puede leerse y escribirse en el mismo ciclo de reloj; y en el caso de esta implementación segmentada, la lectura y escritura se harán por diferentes instrucciones. 24 12 Write back 25 Corrección al camino de datos para la instrucción LW 26 13 Se analizará la siguiente secuencia de instrucciones: lw $10, 20 ($1) sub $11, $2, $3 27 28 14 29 30 15 31 32 16 33 34 17 35 36 18 37 38 19 39 Proceso de ejecución de SW IF: la instrucción es capturada de memoria y almacenada en IF/ID ID: IF/ID proporciona los números de registros que se leerán y se realiza la extensión de signo de 16 a 32 bits, dichos valores se almacenan en ID/EX EX: Se suma el 1er registro y el la constante extendida a 32 bits, se almacenan en EX/MEM MEM: El segundo registro previamente almacenado en ID/EX y posteriormente en EX/MEM se almacena en la dirección de memoria calculada en la etapa anterior. WB: No se hace nada 40 20 Proceso de ejecución de SW 41 Ejecución de SW 42 21 Ejecución de una secuencia de instrucciones 43 Ejecución de las 5 instrucciones a la vez 44 22 El control segmentado 45 Señales de control en cada etapa 1. Captura de la Instrucción. Las señales de control para 2. Decodificación de la instrucción y lectura del archivo de registro. Sucede una situación similar a la la lectura de memoria de código y escritura del PC están siempre acertadas, por que cambiarán su valor en cada ciclo de reloj, por lo que no hay líneas de control especiales. etapa anterior, no hay líneas de control para un ajuste opcional. 3. Ejecución o Cálculo de una dirección. En esta etapa, dependiendo del tipo de instrucción debe seleccionarse: El segundo operando de la ALU (ALUSrc). La operación que realizará la ALU (ALUOp). El registro destino (RegDst). 46 23 4. Acceso a memoria. Aquí se determina si: 5. Se trata de un brinco (branch). Se escribirá en memoria (MemWrite). Se leerá de memoria (MemRead). Retro escritura. Son dos señales que se deben definir: La que determina si se escribirá el resultado de la ALU o el dato de memoria (MemtoReg). La que habilita la escritura en el archivo de registros (RegWrite). 47 Las señales de control 48 24 Valores para el control Las señales de control deben tener los valores correctos en la etapa correcta, dependiendo del tipo de instrucción a ejecutar. Los valores son los mismos que en la implementación de un solo ciclo, la diferencia es que se requieren en diferentes etapas. 49 En la etapa 1 se atrapa la instrucción y se almacena en IF/ID. En la 2ª etapa se toma del registro IF/ID el opcode que determina el tipo de instrucción que se está ejecutando, mismas que entran al circuito de control. 50 25 51 Ejemplo de Ejecución segmentada. Evaluar la ejecución de las cinco instrucciones siguientes a través de la segmentación: ¾ lw $10, 20 ($1) ¾ sub $11, $2, $3 ¾ and $12, $4, $5 ¾ or $13, $6, $7 ¾ add $14, $8, $9 52 26 53 54 27 55 56 28 57 58 29 59 60 30 61 Ejemplo Ejecución de la secuencia de instrucciones: Lw $10, 9( $1) Sub $11, $2, $3 And $12, $4, $5 Or $13, $6, $7 Add $14, $8, $9 62 31 63 64 32 65 66 33 67 68 34 69 70 35 71 Segmentación en el procesador Alpha 21264 72 36 73 37