capitulo 7 - Arquitectura y Tecnología de Computadores

Anuncio

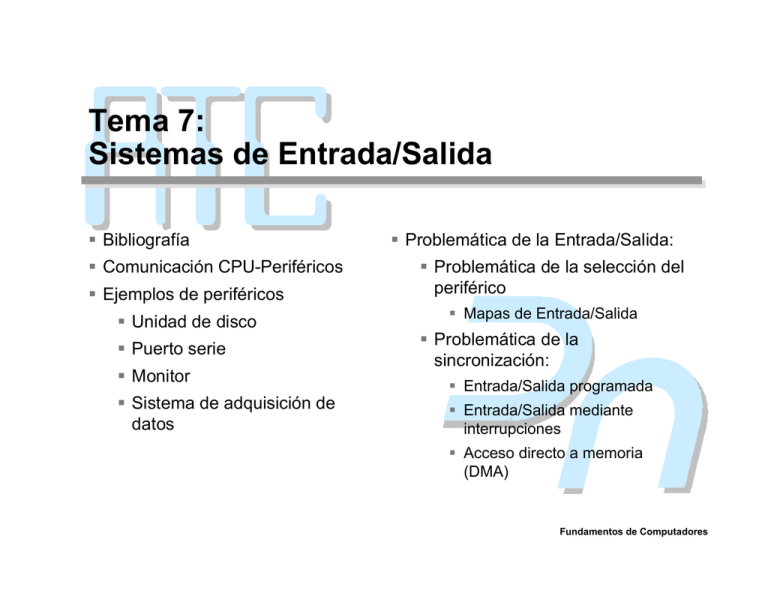

Tema 7: Sistemas de Entrada/Salida Bibliografía Comunicación CPU-Periféricos Ejemplos de periféricos Unidad de disco Puerto serie Monitor Sistema de adquisición de datos Problemática de la Entrada/Salida: Problemática de la selección del periférico Mapas de Entrada/Salida Problemática de la sincronización: Entrada/Salida programada Entrada/Salida mediante interrupciones Acceso directo a memoria (DMA) Fundamentos de Computadores Bibliografía Arquitectura de Computadores (Capítulo 6) José A. de Frutos, Rafael Rico. Ed. Servicio de Publicaciones de la UA Fundamentos de los Computadores (Capítulo 8) Pedro de Miguel Anasagasti. Ed. Paraninfo Arquitectura de computadores. Un enfoque cuantitativo (Capítulo 9) Hennessy, J.L., Patterson, D.A Ed. McGraw-Hill. Estructura y diseño de computadores: Interficie circuitería/programación (Capítulo 8). Patterson, D.A., Hennessy, J.L.. Ed. Reverté. Organización y Arquitectura de Computadores (Capítulo 6) William Stallings. Ed. Prentice Hall 2 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Comunicación CPU-Periféricos (I) El fin de los sistemas de E/S de un computador es comunicar éste con el mundo exterior COMPUTADOR CPU ALU UC MEMORIA CENTRAL SISTEMAS DE E/S MUNDO EXTERIOR Esta comunicación cubre numerosos aspectos: desde la interacción hombremáquina hasta el control de procesos en sistemas automáticos La transferencia de información entre la CPU (computador) y el mundo exterior se realiza a través de dispositivos llamados periféricos Los periféricos realizan la interfaz entre el mundo síncrono y codificado del computador y el mundo analógico exterior 3 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Comunicación CPU-Periféricos (II) Los periféricos pueden ser: Dispositivos de entrada de datos: el teclado, el ratón, el scaner, los sensores de magnitudes mecánicas o electricas, etc Dispositivos de salida de datos: como el monitor, la impresora, etc Dispositivos de entrada y salida de datos: como los discos Un caso especial de periférico son los puertos serie o paralelo que representan simplemente canales de E/S de datos entre CPU y el exterior Un periférico siempre tiene dos partes: El controlador: se encarga de la comunicación con la CPU El dispositivo mecánico, electromecánico o electromagnético con su electrónica de control (o un transductor en el caso de sensores) Misión del controlador: Transferencia de datos (objeto propio de la comunicación) Protocolo de la transferencia ("ponerse de acuerdo" en el cómo y el cúando) Misión del dispositivo: Relación con el exterior 4 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Ejemplos de periféricos (I) PERIFÉRICO Señales de control CONTROLADOR sincronización codificación decodificación Datos física del fenómeno DISPOSITIVO asignación de puerto de E/S Direcciones registro de datos registro de control Ejemplo de un periférico general 5 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Ejemplos de periféricos (II) Unidad de disco UNIDAD DE DISCO Señales de control CONTROLADORA IDE discos DMA transfer. codificación / decodificación Datos motor posición cabezas lógica de control de motores Direcciones registro de datos motor discos registro de control Ejemplo de un disco 6 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Ejemplos de periféricos (III) Puerto serie PUERTO SERIE Señales de control CONTROLADOR INTERFAZ RS-232C reloj 1 5 6 conector DB9 Datos Direcciones 9 registro de datos 2 RxD 6 DSR 3 TxD 7 RTS 4 DTR 8 CTS 5 Gnd registro de control Ejemplo de un puerto serie 7 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Ejemplos de periféricos (IV) Monitor MONITOR Señales de control CONTROLADORA VGA DMA transfer. MEMORIA conector DB15 Datos Codificación-RGB&sincronismo Direcciones registro de datos 1 red 2 green 3 blue 13 horiz. sync. 14 vert. sync. F. A. electrónica alta frecuencia registro de control Ejemplo de un monitor 8 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Ejemplos de periféricos (V) Sistema de adquisición de datos SISTEMA DE ADQUISICIÓN DE DATOS Señales de control TARJETA DE ADQUISICIÓN memoria Datos DMA IRQ termopar tensiones A/D mux. acondicionamiento de señal temporizador fuente de tensión registro de datos Direcciones registro de control Ejemplo de un sistema de adquisición de datos 9 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (I) 1. Selección del periférico Direccionando los registros de datos y de control A cada periférico le corresponden varias direcciones del mapa de E/S, llamadas puertos 2. Sincronización Problemática de salida de datos: La CPU trabaja a una velocidad muy superior a la que transmiten información los periféricos, de manera que pueden ser desbordados Problemática de la entrada de datos: La información no es generada por el periférico en sincronía con la CPU 3. Gestión de las señales de control Solución Ö CPU, controlador del dispositivo y software de E/S 10 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (II) Problemática de selección del periférico Mapas de Entrada/Salida Existen dos soluciones: Mapas de memoria y de E/S disjuntos (separados) Mapas de memoria y de E/S comunes (E/S mapeada en memoria) La forma de direccionar puertos es similar a la de posiciones de memoria; tan solo cambian las señales de control si los mapas de memoria y E/S son disjuntos. 11 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (III) Problemática de la sincronización (I) Sincronización controlador-dispositivo El registro de estado del controlador informa a la CPU sobre el estado de las señales que se encargan de la sincronización con el dispositivo: Petición de servicio Petición de servicio Ocupado/error Ocupado/Error dispositivo Servicio terminado Servicio terminado dispositivo controlador El registro de estado puede indicar también situaciones de error, anomalías en el funcionamiento del periférico, etc. PERIFÉRICO Información CPU CONTROLADOR Datos DISPOSITIVO Petición de servicio Ocupado/Error Direcciones 12 Fundamentos de Computadores Departamento de Automática Servicio terminado Universidad de Alcalá Problemática de la Entrada/Salida (IV) Problemática de la sincronización (II) Debe haber mecanismos que resuelvan los problemas de temporización Hay que tener en cuenta esta temporización en dos aspectos: Inicio de la transferencia Transferencia propiamente dicha Según la intervención de la CPU en estos momentos tenemos: E/S programada: la CPU tiene todo el protagonismo ya que inicia y lleva a cabo la transferencia E/S por interrupción: la CPU ejecuta la transferencia pero el inicio es pedido por el periférico que indica así su disponibilidad Acceso directo a memoria (DMA): la transferencia es realizada por un controlador especializado 13 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (V) Problemática de la sincronización (III) Entrada/Salida programada La CPU inicia y realiza la transferencia La transferencia puede ser: Incondicional: la CPU no comprueba si el periférico está disponible Polling La CPU consulta si los periféricos están disponibles para realizar una transferencia Ð registro de estado del controlador del periférico lectura reg. estado lectura reg. estado Dato disponible? Acepta nuevo dato? Condicional: la CPU comprueba si el periférico está disponible antes de iniciar una transferencia de información. Este método se conoce como sondeo o polling Ventajas: Programación sencilla y el hardware es simple Inconveniente: Se malgasta tiempo de proceso no si 14 si lectura reg. datos escritura reg. datos otras tareas otras tareas no fin? si LECTURA/ENTRADA Fundamentos de Computadores Departamento de Automática no no fin? si ESCRITURA/SALIDA Universidad de Alcalá Problemática de la Entrada/Salida (VI) Problemática de la sincronización (IV) Entrada/Salida mediante interrupciones (I) En la E/S por interrupción: 1º El periférico realiza la petición de servicio mediante una señal de control específica (interrupción hardware) 2º Cuando la interrupción es aceptada por la CPU, ésta abandona momentáneamente el programa principal para ejecutar la rutina de tratamiento de la interrupción y realiza la transferencia PC FLAGS ANTES INT RUTINA INT Siguiente instrucción Vector de interrupción DESPUÉS INT Siguiente instrucción Estado Estado SP PILA SP Siguiente instrucción Estado SP Antes de comenzar la rutina de tratamiento de la interrupción la CPU debe salvar la dirección de retorno y el registro de estado 15 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (VII) Problemática de la sincronización (V) Entrada/Salida mediante interrupciones (II) Aceptación de interrupciones Mecanismos de la E/S por interrupción: Aceptación o no de la petición de interrupción Dirección donde se encuentra la rutina de tratamiento de la interrupción (vector de interrupción) Conexión de varios periféricos con capacidad de interrumpir Gestión de prioridades en caso de peticiones simultáneas Las interrupciones pueden ser: Enmascarables: se pueden dejar de atender por procedimiento software No enmascarables: siempre son atendidas Vector de interrupción Existen dos formas de determinar la posición en la que se encuentra la rutina de tratamiento de la interrupción: Vector de interrupción fijo y determinado por la CPU El periférico suministra el vector de interrupción completo o una codificación del mismo 16 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (VIII) Problemática de la sincronización (VI) Entrada/Salida mediante interrupciones (III) Conexión de varios periféricos y gestión de prioridades Resolver cómo conectarlos con la CPU Establecer prioridades Determinar el vector de interrupción 1. CPU con una línea de interrupción: Todos los periféricos hacen la petición en la misma línea El vector de interrupción es fijo y común a todos los periféricos La rutina de interrupción identifica mediante polling el periférico que interrumpió a la CPU y desactiva la petición La prioridad se determina por el orden en que se realiza el polling 17 Fundamentos de Computadores Departamento de Automática 2. CPU con varias líneas de interrupción: Cada periférico hace la petición por una línea distinta El vector de interrupción es fijo pero diferente para cada línea y por tanto para cada periférico La prioridad la determina internamente la CPU 3. CPU con línea de petición de interrupción y de aceptación (I): La CPU cuenta con una línea de entrada INT para las peticiones de interrupción y con una línea de salida INTA para dar los reconocimientos de interrupción Universidad de Alcalá Problemática de la Entrada/Salida (IX) Problemática de la sincronización (VII) Entrada/Salida mediante interrupciones (IV) 3. CPU con línea de petición de interrupción y de aceptación (II): a) Encadenamiento de periféricos o daisy-chain Todos los periféricos piden servicio por la misma línea (INT) Cuando la CPU acepta la interrupción activa INTA El periférico de mayor prioridad desactiva la petición y activa un biestable de concesión La CPU identifica por polling el periférico que ha interrumpido, observando el biestable de concesión El vector de interrupción es fijo y la resolución de prioridades es por daisychain 18 Fundamentos de Computadores Departamento de Automática b) Interrupciones vectorizadas Todos los periféricos piden servicio por la misma línea (INT) Cuando la CPU reconoce la interrupción (INTA), el periférico se identifica poniendo en el bus de datos el vector de interrupción La resolución de prioridades se puede realizar por daisy-chain Universidad de Alcalá Problemática de la Entrada/Salida (X) Problemática de la sincronización (VIII) Entrada/Salida mediante interrupciones (V) 3. CPU con línea de petición de interrupción y de aceptación (III): c) Gestión centralizada de interrupciones mediante controlador Un PIC (Programmable Interruption Controller) permite la conexión de distintos periféricos a la línea de petición de la CPU expandiendo en varios niveles dicha línea (INT) Permite enmascarar aquellas líneas que se desee mediante un registro de máscara programable Admite controladores esclavos para expandir más niveles de interrupción Resuelve la gestión de prioridades de forma flexible: Prioridad fija (por orden) Línea prioritaria la que lleva más tiempo sin atenderse 19 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (XI) Problemática de la sincronización (IX) Acceso directo a memoria - DMA (I) En el acceso directo a memoria (Direct Memory Access): El controlador del periférico se comunica directamente con la memoria principal del computador La CPU no realiza ninguna tarea, tanto la inicialización como la transferencia son gobernadas por el periférico DATOS DIRECCIONES CPU MEMORIA PRINCIPAL HOLDA HOLD La transferencia de E/S se lleva a cabo por la activación de las señales de control de acceso a memoria Controladora DMA señales de control 20 Fundamentos de Computadores Departamento de Automática Universidad de Alcalá Problemática de la Entrada/Salida (XII) Problemática de la sincronización (X) Acceso directo a memoria - DMA (II) Formas de realizar el DMA: Acceso directo a memoria multipuerto Una memoria multipuerto es aquella que tiene posibilidad de realizar transferencias simultáneas con el exterior por medio de varios puertos A cada puerto se le asigna un registro de datos y otro de direcciones que guardan el dato transferido y la dirección de transferencia MEMORIA Puerto 1 CPU Bus de datos Bus de direcciones Bus de control 21 Puerto 2 Puerto 3 Acceso directo a memoria por robo de ciclo La memoria tiene un solo puerto que es compartido entre el controlador de DMA y la CPU Siempre que el periférico requiera una transferencia DMA debe hacer una petición de robo de ciclo a la CPU (HOLD) La CPU hace la concesión (HOLDA) El controlador de DMA controla los buses de direcciones y datos, y las señales de control de memoria y E/S Terminada la transferencia, el controlador lo comunica a la CPU Bus de datos Controlador periférico Fundamentos de Computadores Departamento de Automática Bus de direcciones Bus de control Universidad de Alcalá