Registros de Corrimiento en la GAL22V10

Anuncio

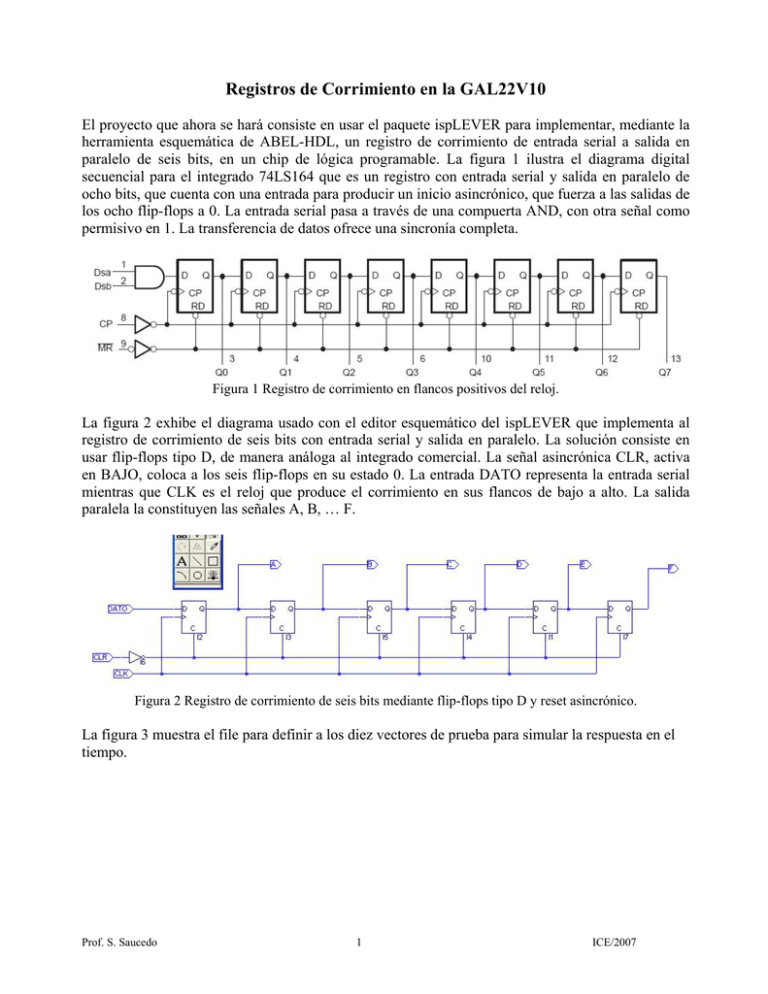

Registros de Corrimiento en la GAL22V10 El proyecto que ahora se hará consiste en usar el paquete ispLEVER para implementar, mediante la herramienta esquemática de ABEL-HDL, un registro de corrimiento de entrada serial a salida en paralelo de seis bits, en un chip de lógica programable. La figura 1 ilustra el diagrama digital secuencial para el integrado 74LS164 que es un registro con entrada serial y salida en paralelo de ocho bits, que cuenta con una entrada para producir un inicio asincrónico, que fuerza a las salidas de los ocho flip-flops a 0. La entrada serial pasa a través de una compuerta AND, con otra señal como permisivo en 1. La transferencia de datos ofrece una sincronía completa. Figura 1 Registro de corrimiento en flancos positivos del reloj. La figura 2 exhibe el diagrama usado con el editor esquemático del ispLEVER que implementa al registro de corrimiento de seis bits con entrada serial y salida en paralelo. La solución consiste en usar flip-flops tipo D, de manera análoga al integrado comercial. La señal asincrónica CLR, activa en BAJO, coloca a los seis flip-flops en su estado 0. La entrada DATO representa la entrada serial mientras que CLK es el reloj que produce el corrimiento en sus flancos de bajo a alto. La salida paralela la constituyen las señales A, B, … F. Figura 2 Registro de corrimiento de seis bits mediante flip-flops tipo D y reset asincrónico. La figura 3 muestra el file para definir a los diez vectores de prueba para simular la respuesta en el tiempo. Prof. S. Saucedo 1 ICE/2007 MODULE corrimientos X,K = .x.,.c.; "entradas CLK,CLR,DATO PIN; "Seis salidas A,B,C,D,E,F PIN ISTYPE 'REG'; TEST_VECTORS ([CLK,CLR,DATO]->[A,B,C,D,E,F]) [0, 0, 0 ]->[0,0,0,0,0,X]; [K, 1, 0 ]->[0,0,0,0,0,X]; [K, 1, 1 ]->[1,0,0,0,0,X]; [K, 1, 0 ]->[X,X,0,0,0,X]; [K, 1, 1 ]->[1,0,X,0,0,X]; [K, 1, 1 ]->[1,1,0,1,0,X]; [K, 1, 0 ]->[0,X,1,0,1,0]; [K, 1, 1 ]->[1,0,X,1,0,1]; [0, [K, 0, 1, 0 1 ]->[0,0,0,X,0,0]; ]->[X,0,X,0,0,0]; END Figura 3 File tipo .ABV para definir los vectores de prueba. La figura 4 muestra la respuesta para los vectores de prueba propuestos. Figura 4 Respuesta en el tiempo de la simulación del mapa de fusibles del file .JED. Prof. S. Saucedo 2 ICE/2007 Tarea Práctica Analizar el siguiente esquema y predecir el funcionamiento. Sugerencia: estudiar al integrado 74LS194. Capturar con el editor esquemático de ABEL-HDL y simularlo. Figura 5 Registro universal bidireccional de corrimiento de cuatro bits. La figura siguiente puede servir para simular los vectores module vectores X,C = .x.,.c.; " entradas CP,MR,S1,S0,DSR,DSL PIN; S = [S1,S0]; " Modo P3..P0 PIN; P = [P3..P0]; " Carga paralela " Salidas Q3..Q0 pin istype 'reg'; Q = [Q3..Q0]; test_vectors ([CP,MR,S,DSR,DSL, P]->Q) [C, 1, 3, 1, 0, 11]->X; [C, 1, 2, 1, 0, 11]->X; [C, 1, 2, 0, 1, 11]->X; [C, 1, 2, 1, 0, 7]->X; [C, 1, 2, 0, 1, 7]->10; [C, 1, 3, 1, 0, 7]->7; [C, 1, 2, 1, 0, 11]->3; [C, 0, 2, 0, 1, 11]->0; [C, 1, 1, 1, 0, 14]->1; [C, 1, 1, 0, 1, 14]->2; [C, 1, 1, 1, 0, 14]->5; [C, 1, 0, 0, 1, 11]->5; [C, 1, 0, 1, 0, 7]->5; END Prof. S. Saucedo 3 ICE/2007