FACULTAD DE INGENIERIA INTRODUCCION A LOS

Anuncio

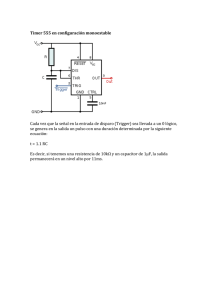

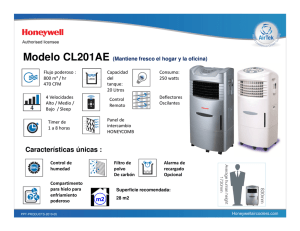

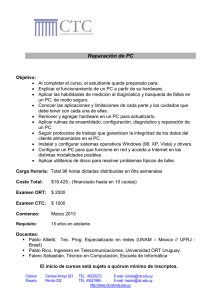

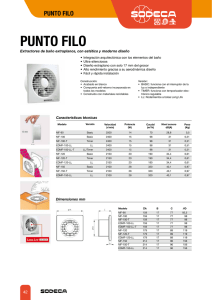

FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 PROBLEMA 1 – Parte a) Caso T80 y bloques lab – – – – Bloque Timer Controlador1 con bloque Timer Controlador0 con BOTON TULT[8], LJUEGO, LTOUT puertos out DFF DO[0] D ODSP_LJUEGO_n PRN Q OUTPUT LJUEGO OUTPUT LTOUT OUTPUT TULT[7..0] CLRN inst36 DFF DO[0] D ODSP_LTOUT_n PRN Q CLRN inst35 DFF DO[7..0] D ODSP_TULT_n PRN Q CLRN inst55 INTtimer_n INTbot_n AND3 De otros controladores A[7] AND2 Hacia T80 inst31 NOT A[6] INT_n OR2 rangoIO_n inst9 inst2 IORQ_n 0xC0-0xFF inst14 deco_1de4 A[2] A1 A0 A[1] A[4] rangoIO_n RD_n Y0 Y1 Y2 Y3 OR3 CS_TIMER_n NOT CS_INTtimer_n CS_TIMER inst25 CS_INTbot_n G inst15 AND2 inst21 DECO WR_n inst78 A[4] deco_1de4 A[1] NOT A[0] inst43 rangoIO_n WR_n Y0 Y1 Y2 Y3 A1 A0 OR3 ODSP_LJUEGO_n ODSP_LTOUT_n ODSP_TULT_n G inst26 inst39 DECO Pag. 1/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 DO[7..0] Desde T80 bloquetimer M1_n M1_n IORQ_n INT_n IORQ_n RD_n RD_n CLK clk RESET zc CS_TIMER datos_o[7..0] inst3 RESET A[0] AND2 c_aux[7..0] A0 CS_TIMER_n CE_n trg datos_i[7..0] INTA_n_timer INTA_n inst4 controlador_de_interrupciones CLK RESET_n CK DO[7..0] RESET_n M1_n IORQ_n INT_n M1_n WR_n MREQ_n IEO_timer IEO IORQ_n RD_n INTtimer_n SRV RD_n IORQ_out_n WR_n M1_out_n MREQ_n OR2 INTA_n_timer inst8 DI_v ector[7..0] VCC DI_opcode[7..0] A[0] CS_INTtimer_n A0 CE_n IEI NOT IRQ inst67 inst6 controlador_de_interrupciones CLK RESET_n CK RESET_n M1_n IORQ_n M1_n IORQ_n RD_n WR_n MREQ_n DO[7..0] INTbot_n INT_n IEO SRV RD_n IORQ_out_n WR_n M1_out_n OR6 MREQ_n DI_v ector[7..0] CS_INTbot_n A0 Hacia T80 CE_n IEO_timer IEI BOTON DI[7..0] DI_opcode[7..0] A[0] INPUT VCC IRQ Desde MEMORIAS inst5 inst7 Pag. 2/9 FACULTAD DE INGENIERIA INTRODUCCION A LOS MICROPROCESADORES UNIVERSIDAD DE LA REPUBLICA FEBRERO 2014 Parte a) Caso buses multiplexados y CTC A[7] AND2 A[6] inst17 IORQ_n NOT OR2 rangoIO_n inst18 0xC0-0xFF inst19 A[4] OR2 CS_CTC rangoIO_n inst20 deco_1de4 A[1] A[4] NOT A[0] inst48 rangoIO_n WR_n ODSP_LJUEGO_n Y0 Y1 Y2 Y3 A1 A0 OR3 ODSP_LTOUT_n ODSP_TULT_n ODSP_TMEJOR_n G inst29 inst42 DECO D[7..0] ctc D0..D7 M1 VCC IEI M1\ CK/TRG0 IORQ\ ZC/TO0 RD\ CK/TRG1 ZC/TO1 CS1 CK/TRG2 CS0 ZC/TO2 CE\ CK/TRG3 IORQ RD A[1] A[0] CS_CTC CK RESET/ CK RESET\ canal 0 en modo Timer canal 1 en cascada BOTON R IEO INT\ canal 2 Counter interrumpe en cada flanco de BOTON OUTPUT INT/ inst16 D[0] DFF D PRN Q LJUEGO Q LTOUT Q TULT[7..0] ODSP_LJUEGO_n CLRN inst28 D[0] DFF D PRN ODSP_LTOUT_n CLRN inst32 DFF D PRN ODSP_TULT_n CLRN inst33 Pag. 3/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 b) ---- isr de boton y timer ---isr_boton: ;si ESTADO=Jugando entonces ; detener Timer ; ESTADO = Inactivo ; LJUEGO = 0 ; tjugada = TOUT - timer ;; timer decreciente desde TOUT hasta 0 ; TULT = tjugada ;else ; Estado = Jugando ; LJUEGO = 1 ; LTOUT = 0 ; TULT = 0 ; Arrancar Timer ;fin_si estado ei push af ld a, (ESTADO) cp EJUGANDO jr nz, else ;; si ESTADO == Jugando ;; detener Timer call stop_timer ;; ESTADO = Inactivo ;; LJUEGO = 0 ld a, EINACTIVO ld (ESTADO), a ld a, 0 out (LJUEGO), a ;; TULT = TOUT – timer ;; decreciente desde TOUT in a, (CUENTA_TIMER) neg add TOUT out (TULT), a jr finsi else: ;; Estado = Jugando ld a, EJUGANDO ld (ESTADO), a ;; LJUEGO = 1 ;; LTOUT = 0 ;; TULT = 0 ld a, 0xFF out (LJUEGO), a ld a, 0 out (LTOUT), a out (TULT), a ;; Arrancar Timer call start_timer finsi: pop af reti isr_timer: ; detener Timer ; LJUEGO = 0 ; LTOUT = 1 ; ESTADO = Inactivo ; ei push af call stop_timer ld a, 0 out (LJUEGO), a ld a, 0xff out (LTOUT), a ld a, EINACTIVO ld (ESTADO), a pop af reti start_timer: ld a, TIMER_ON_CTE out (BASE_TIMER+0), a ret stop_timer: ld a, TIMER_OFF_CTE out (BASE_TIMER+0), a ret c) --- Init ---------------org 0 ;; stack, modo2, tabla int sp, 0 2 hl, BASETABLA a, h i, a ;; ESTADO = Inactivo ;; TULT = 0 ;; LJUEGO = 0 ;; LTOUT = 0 ld a, EINACTIVO ld (ESTADO), a ld a, 0 out (TULT), a out (LJUEGO), a out (LTOUT), a ;; inic timer y ctrl int. call init_perif ;; inic otros dispositivos call init_otros ei jp ppal ld im ld ld ld init_perif: ;; vectores interr ld a, TIMER_VEC out (BASE_CTRL_TIMER+0), a ld a, TOUT_VEC out (BASE_CTRL_BOTON+0), a ;; borro eventuales peticiones pendientes out (BASE_CTRL_TIMER+1), a out (BASE_CTRL_TOUT+1), a ;; cte recarga timer ld a, TOUT out (BASE_TIMER+1), a ret Pag. 4/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 org 100 ;; tabla interrupciones basetabla: DW isr_otro0 DW isr_otro1 DW isr_otro2 DW vacio DW isr_timer ;; vect = 8 DW isr_boton ;; vect = 10 org 0x8000 ;; variables ESTADO: DB LJUEGO LTOUT TULT EQU EQU EQU DELTA TOUT EQU 100 EQU 200 BASE_TIMER BASE_CTRL_TIMER BASE_CTRL_BOTON EQU EQU EQU 0xC0 0xC2 0xC4 TIMER_VEC BOTON_VEC EQU EQU 8 10 0xF0 0xF1 0xF2 ; ei, reset, auto, pre=15 EQU 10101111b TIMER_ON_CTE ; di, resto idem EQU 00101111b ------------------ Cambios en solución con CTC Se utilizan tres canales del CTC: • canal 0: timer, pre=256, cte=128 para llegar a período de 100ms • canal 1: counter, cte=TOUT para interrumpir por timeout • canal 2: counter, cte=1 para generar interrupcion con cada flanco de BOTON BASE_CTC CTC_VEC CTC_CTE0 EQU EQU EQU CTC_CTE1 EQU ; ei, cnt, x, x, x, CTC_CW1 EQU ; idem con di CTC_CW1_OFF EQU TOUT tc, reset 11000111 01000111 CTC_CTE2 EQU 1 ; ei, cnt, x, edge-, x, tc, reset CTC_CW2 EQU 11000111 Las nuevas versiones de las subrutinas son: ;; definicion de ctes EJUGANDO EQU 0xFF EINACTIVO EQU 0x0 TIMER_OFF_CTE ; di, timer, 256, x, auto, tc, reset CTC_CW0 EQU 00100111 0xC0 8 128 init_perif: ;; vector ld a, CTC_VEC out (BASE_CTC+0), a ;; canal 2 para boton ld a, CTC_CW2 out (BASE_CTC+2), a ret start_timer: ;; rearranco canales 0 y 1 ld a, CTC_CW0 out (BASE_CTC+0), a ld a, CTC_CTE0 out (BASE_CTC+0), a ld a, CTC_CW1 out (BASE_CTC+1), a ld a, CTC_CTE1 out (BASE_CTC+1), a ret stop_timer: ;; deshabilito generación de interrupciones ld a, CTC_CW1_OFF out (BASE_CTC+1), a ld a, CTC_CTE1 out (BASE_CTC+1), a ret ;;; con los canales elegidos debo modificar la tabla de interrupciones. basetabla: DW isr_otro0 DW isr_otro1 DW isr_otro2 DW vacio DW vacio ;; vect = 8 ;; canal 0 no interrumpe DW isr_timer DW isr_boton Pag. 5/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 PROBLEMA 2 – Solución a) Hardware Memoria ROM A[14..0] Add[] /CS_ROM D[7..0] Data[] CS OE inst11 RAM Add[] Data[] /CS_RAM CS OE WE /RD /WR inst10 A[15] NOT OR2 inst7 /CS_RAM /MREQ inst20 OR2 /CS_ROM inst21 Interrupción VCC DFF D TIC PRN NOT Q /INT inst12 CLRN inst36 /RESET /M1 AND2 OR2 inst /IORQ inst3 Pag. 6/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 Puertos /IDSP_jugador D[7..0] NOT inst48 J1 D[0] TRI INPUT VCC inst31 DFF D /IDSP_PP NOT PRN LEDS[7..0] OUTPUT Q inst45 VCC PAUSE INPUT VCC DFF D NOT PRN Q CLRN inst9 D[0] TRI inst30 /ODSP_leds inst6 /ODSP_CLRpausa CLRN inst37 Decodificación puertos deco_1de4 A[1] A[0] Y0 Y1 Y2 Y3 A1 A0 /IORQ OR2 /ODSP_leds (0h) /ODSP_CLRpausa (1h) deco_1de4 G /WR inst4 inst18 A[1] DECO A[0] Y0 Y1 Y2 Y3 A1 A0 /IORQ OR2 /IDSP_PP G /RD inst5 inst19 (0h) /IDSP_jugador (1h) DECO Pag. 7/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 d) Inicialización y variables c) Programa principal ;----- variables org 8000h PAUSA db ; FIN db ; SENTIDO db ; POSICION db ; org 1000h PPAL: ld A, FINALIZADO cp (FIN) jp Z, END FFh = pausa FFh = fin 00h der, FFh izq donde esta la pelota ;----- constantes PAUSADO equ FINALIZADO equ DERECHA equ SENTIDO_INI equ POSICION_INI equ P_EN_FRONTON equ P_EN_JUGADOR equ FFh FFh 00 DERECHA 0001 0000b 0000 0001b 1000 0000b ;----- puertos LEDS PAUSE_PLAY CL_PAUSE_PLAY JUGADOR 00h 01h ; en bit 0 00h 01h ; en bit 0 equ equ equ equ in A, (PAUSE_PLAY) bit 0, A jp Z, TOGGLE_PAUSE_PLAY jp PPAL TOGGLE_PAUSE_PLAY: ld A, (PAUSA) cpl A, ld (PAUSA), A out (CL_PAUSE_PLAY), A jp PPAL END: di END_LOOP: jp END_LOOP ;----- inicialización ; modo 1 y stack ; variables: fin, pausa, sentido ; HW: borrar flag PAUSE, leds org 0000h im 1 ld SP, 0000h ld A, FINALIZADO cpl A ld (FIN), A ld A, PAUSADO ld (PAUSA),A ld A, SENTIDO_INI ld (SENTIDO),A ld A, POSICION_INI ld (POSICION),A out (LEDS), A out (CL_PAUSE_PLAY), A EI jp PPAL Pag. 8/9 FACULTAD DE INGENIERIA UNIVERSIDAD DE LA REPUBLICA INTRODUCCION A LOS MICROPROCESADORES FEBRERO 2014 b) Rutina atención interrupción jp Z, perdio ; le pego_antes jp actualizo ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; ; si pausa retorno si pelota yendo a la derecha si pelota en posicion 0 cambio sentido actualizo posicion y retorno sino si pelota en posicion 7 si J1 apretado cambio sentido actualizo posicion y retorno sino fin de juego sino "hacia izq y no en led 7" si J1 apretado fin de juego sino actualizo posicion y retorno fin de juego: indico fin en leds seteo variable FIN retorno actualizo posicion y retorno: si SENTIDO = derecha roto POSICION a la derecha sino roto POSICION a la izquierda actualizo leds retorno cambio_sentido: ld A, (SENTIDO) cpl ld (SENTIDO), A actualizo: ld IX, POSICION ld A, (SENTIDO) cp DERECHA jp nz, hacia_jugador hacia_fronton: rr (IX) jp actualizo_leds hacia_jugador rl (IX) actualizo_leds: ld A, (POSICION) out (LEDS), A jp retorno perdio: ld A, FINALIZADO ld (FIN), A out (LEDS), A retorno: pop IX pop AF ei ret org 38h push AF push IX ld A, (PAUSA) cp PAUSADO jp Z, retorno ld A, (SENTIDO) cp DERECHA jp NZ, hacia_izquierda hacia_derecha: ld A, (POSICION) cp P_EN_FRONTON jp Z, cambio_sentido jp actualizo hacia_izquierda: ld A, (POSICION) cp P_EN_JUGADOR jp nz, pelota_lejos_jugador pelota_en_jugador: in A, (JUGADOR) bit 0, A jp Z, cambio_sentido ; le pego jp perdio pelota_lejos_jugador: in A, (JUGADOR) bit 0, A Pag. 9/9