Comparador de 4 Bit.

Anuncio

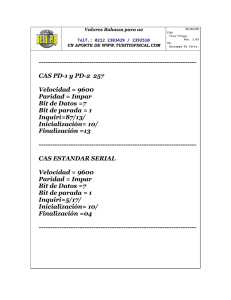

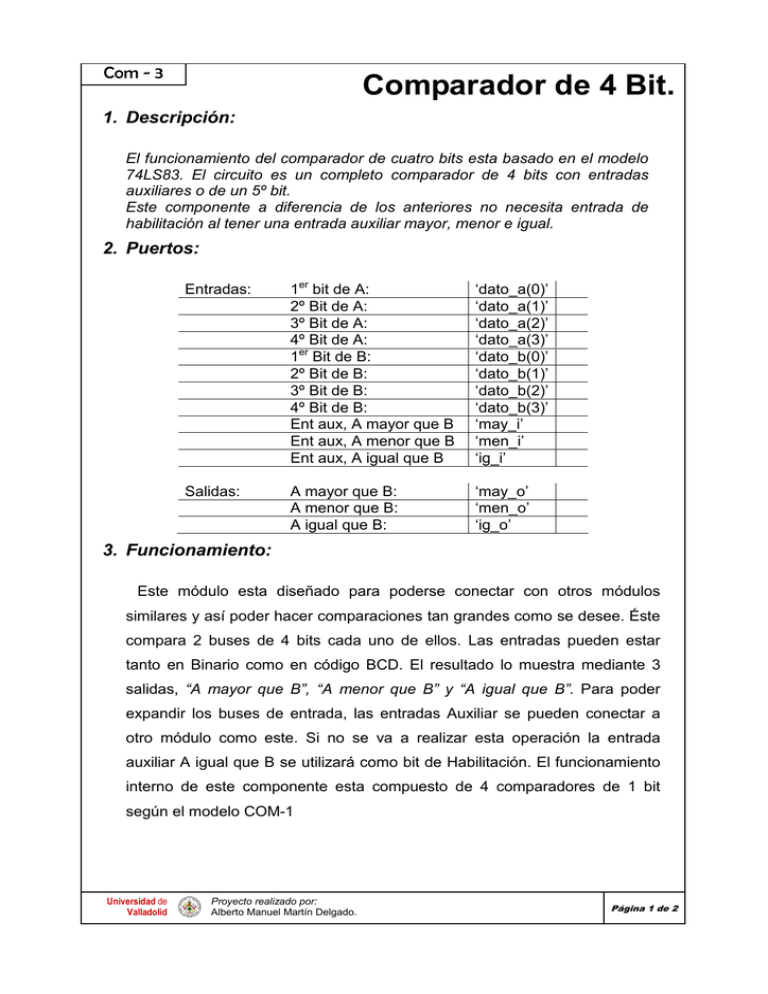

Com - 3 Comparador de 4 Bit. 1. Descripción: El funcionamiento del comparador de cuatro bits esta basado en el modelo 74LS83. El circuito es un completo comparador de 4 bits con entradas auxiliares o de un 5º bit. Este componente a diferencia de los anteriores no necesita entrada de habilitación al tener una entrada auxiliar mayor, menor e igual. 2. Puertos: Entradas: 1er bit de A: 2º Bit de A: 3º Bit de A: 4º Bit de A: 1er Bit de B: 2º Bit de B: 3º Bit de B: 4º Bit de B: Ent aux, A mayor que B Ent aux, A menor que B Ent aux, A igual que B ‘dato_a(0)’ ‘dato_a(1)’ ‘dato_a(2)’ ‘dato_a(3)’ ‘dato_b(0)’ ‘dato_b(1)’ ‘dato_b(2)’ ‘dato_b(3)’ ‘may_i’ ‘men_i’ ‘ig_i’ Salidas: A mayor que B: A menor que B: A igual que B: ‘may_o’ ‘men_o’ ‘ig_o’ 3. Funcionamiento: Este módulo esta diseñado para poderse conectar con otros módulos similares y así poder hacer comparaciones tan grandes como se desee. Éste compara 2 buses de 4 bits cada uno de ellos. Las entradas pueden estar tanto en Binario como en código BCD. El resultado lo muestra mediante 3 salidas, “A mayor que B”, “A menor que B” y “A igual que B”. Para poder expandir los buses de entrada, las entradas Auxiliar se pueden conectar a otro módulo como este. Si no se va a realizar esta operación la entrada auxiliar A igual que B se utilizará como bit de Habilitación. El funcionamiento interno de este componente esta compuesto de 4 comparadores de 1 bit según el modelo COM-1 Universidad de Valladolid Proyecto realizado por: Alberto Manuel Martín Delgado. Página 1 de 2 4. Esquema eléctrico: 5. Ejemplo: Para poder comprender mejor el funcionamiento se han compactado los buses de los datos:’a’ y ‘b’. Se han hecho dos comprobaciones: la primera con valores distintos y la segunda con los mismos datos. Se han valiado las entradas auxiliares, primero es igual y el la sigiente la entrada es menor. 6. Cuestiones: • • ¿Cuál tiene que ser la combinación de entradas para que se active el bit ‘ig_o’? ¿Qué pasa cuando las entradas auxiliares estan desactivadas.? Universidad de Valladolid Proyecto realizado por: Alberto Manuel Martín Delgado. Página 2 de 2