universidad de extremadura

Anuncio

UNIVERSIDAD DE EXTREMADURA

Escuela Politécnica

MÁSTER UNIVERSITARIO EN INICIACIÓN A LA

INVESTIGACIÓN EN TECNOLOGÍA (MUIT)

ESPECIALIDAD EN:

TECNOLOGÍAS INFORMÁTICAS Y

DE LAS COMUNICACIONES (TINC)

Trabajo Fin de Máster MUIT-TINC

Implementación de algoritmos de análisis

hiperespectral en tarjetas gráficas programables

(GPUs)

Sergio Sánchez Martínez

Julio 2010

UNIVERSIDAD DE EXTREMADURA

Escuela Politécnica

MÁSTER UNIVERSITARIO EN INICIACIÓN A LA

INVESTIGACIÓN EN TECNOLOGÍA (MUIT)

ESPECIALIDAD EN:

TECNOLOGÍAS INFORMÁTICAS Y

DE LAS COMUNICACIONES (TINC)

Trabajo Fin de Máster MUIT-TINC

Implementación de algoritmos de análisis

hiperespectral en tarjetas gráficas programables

(GPUs)

Autor: Sergio Sánchez Martínez

Fdo:

Director: Antonio J. Plaza Miguel

Fdo:

Tribunal Calificador

Presidente: Juan Manuel Sánchez Pérez

Fdo:

Secretario: Javier Plaza Miguel

Fdo.:

Vocal: Juan Antonio Gómez Pulido

Fdo.:

CALIFICACIÓN:

FECHA:

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Resumen

El análisis de imágenes hiperespectrales en observación remota de la tierra

constituye una línea de investigación muy activa, con numerosas contribuciones en la

literatura científica reciente. Debido a la resolución espacial disponible en sensores de

observación remota de la tierra, la mayor parte de los píxels registrados por el sensor

constituyen una mezcla de diferentes substancias puras a nivel sub-píxel. Para solucionar

este problema, una de las técnicas más ampliamente utilizadas es el desmezclado espectral,

que comprende dos etapas: 1) extracción de firmas espectrales puras (endmembers), y 2)

estimación de la abundancia de dichos endmembers a nivel sub-píxel. Ambas etapas son

muy costosas desde el punto de vista computacional, lo cual supone un importante

inconveniente en aplicaciones que requieren una respuesta en tiempo casi real, tales como

monitorización y seguimiento de incendios, prevención y seguimiento de desastres

naturales, vertidos químicos y otros tipos de contaminación ambiental, etc. En el presente

trabajo, hemos desarrollado una implementación paralela del algoritmo pixel purity index

(PPI), un conocido método de extracción de endmembers disponible en software comercial

como el paquete Research Systems ENVI de Kodak. La implementación paralela propuesta

en este trabajo ha sido desarrollada en una tarjeta gráfica programable (GPU) de tipo

Nvidia Tesla C1060. Nuestra implementación paralela proporciona resultados muy

prometedores, tanto desde el punto de vista de su precisión a la hora de identificar

endmembers como desde el punto de vista del rendimiento paralelo obtenido,

proporcionando factores de aceleración (speedups) de 200x utilizando una única tarjeta

NVidia Tesla C1060. Estos resultados suponen un incremento muy notable del rendimiento

computacional del algoritmo con respecto a su ejecución serie en un PC de última

generación.

Palabras clave:

Hiperespectral, Endmember, PPI, Pixel Purity Index, GPU, CUDA, ENVI.

Trabajo Fin de Máster

3

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Abstract

Remotely sensed hyperspectral imaging is an active area of research in the

literature. Due to available spatial resolution, most of the pixels collected by hyperspectral

imaging instruments are in fact a mixture of different underlying substances. One of the

most widely used approaches for analyzing hyperspectral images is spectral unmixing,

which comprises two stages: 1) extraction of pure spectral signatures (endmembers), and

2) estimation of endmember fractional abundances at sub-pixel levels. Both stages are

computationally complex, which is a serious drawback in applications which require a

response in near real-time, such as forest fire monitoring and tracking, disaster

management and prevention, oil spill detection, etc. In this work, we develop an efficient

parallel implementation of the pixel purity index (PPI), a well-known algorithm for

endmember extraction available in commercial software such as Kodak's Research

Systems ENVI. The parallel implementation has been conducted in a commodity graphics

processing unit (GPU) of NVidia Tesla C1060 type. Our parallel implementation of the PPI

exhibits very promising results in terms of endmember extraction accuracy and parallel

performance, with speedups approaching 200x using just one NVidia Tesla C1060 card.

This represents a tremendous increase of performance with regards to the serial version of

the same algorithm, implemented in a latest-generation desktop PC.

Keywords

Hyperspectral, Endmember, PPI, Pixel Purity Index, GPU, CUDA, ENVI.

Trabajo Fin de Máster

4

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Índice de contenido

1 Motivaciones y Objetivos.................................................................................................10

1.1Motivaciones..............................................................................................................10

1.2Objetivos.....................................................................................................................11

2 Introducción......................................................................................................................14

2.1Concepto de imagen hiperespectral............................................................................14

2.2Sensores hiperespectrales considerados.....................................................................17

2.3Técnicas de análisis hiperespectral y necesidad de paralelismo.................................19

Técnicas basadas en el modelo lineal de mezcla........................................................20

Necesidad de paralelismo...........................................................................................21

El papel de las GPUs...................................................................................................22

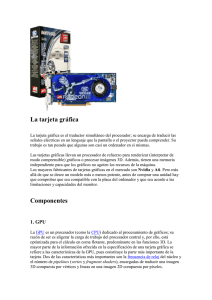

3 Tarjetas gráficas programables GPUs..............................................................................23

3.1Las GPUs como un dispositivo de procesamiento de datos en paralelo....................23

Vortex shaders y píxel shaders....................................................................................24

Pipeline clásico de procesamiento en una GPU..........................................................25

Evolución del uso de GPUs en aplicaciones científicas.............................................27

3.2CUDA: una nueva arquitectura para el calculo en la GPU........................................29

Pipeline unificado.......................................................................................................29

Modelo de programación CUDA................................................................................30

3.3Procesamiento.............................................................................................................32

Un coprocesador multihilo..........................................................................................32

Hilos, Bloques y Grids................................................................................................33

Modelo de memoria....................................................................................................34

3.4Implementación hardware y modelo de ejecución.....................................................35

Nvidia Tesla C1060.....................................................................................................35

Modelo de ejecución...................................................................................................37

Especificaciones generales..........................................................................................39

4 Método..............................................................................................................................43

4.1Pixel Purity Index (PPI)..............................................................................................43

5 Procesamiento paralelo en GPU.......................................................................................47

5.1Generación de los skewers.........................................................................................47

5.2Proyección..................................................................................................................49

5.3Agrupación de resultados...........................................................................................52

5.4CUDA Occupancy Calculator....................................................................................53

5.5CUDA Visual Profiler.................................................................................................57

6 Resultados........................................................................................................................63

7 Conclusiones y líneas futuras...........................................................................................79

8 Apéndice...........................................................................................................................82

8.1Programación con CUDA...........................................................................................82

Compilación................................................................................................................82

Reserva y liberación de memoria de la GPU..............................................................83

Ejecutando código en la GPU.....................................................................................84

Trabajo Fin de Máster

5

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Modificadores de funciones........................................................................................84

Ejecución del kernel....................................................................................................85

Ejemplo de kernel.......................................................................................................85

Herramientas de sincronización..................................................................................88

9 Bibliografía.......................................................................................................................89

10 Publicaciones del Candidato..........................................................................................92

Trabajo Fin de Máster

6

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Índice de figuras

Figura 2.1:Concepto de imagen hiperespectral....................................................................15

Figura 2.2:Adquisición de una imagen hiperespectral por el sensor AVIRIS......................16

Figura 2.3:Tipos de pixeles en imagenes hiperespectrales...................................................17

Figura 2.4:Evolución de la relación SNR del sensor AVIRIS de NASA.............................19

Figura 2.5:Interpretación gráfica del modelo lineal de mezcla............................................20

Figura 3.1: Operaciones en coma flotante por segundo para CPU y GPU..........................23

Figura 3.2:Ancho de banda CPU y GPU..............................................................................24

Figura 3.3:Pipeline clásico de procesamiento en una GPU..................................................26

Figura 3.4:La GPU proporciona más transistores para el procesamiento de datos..............27

Figura 3.5:Pipeline clásico frente a pipeline unificado........................................................30

Figura 3.6:Pila de software de CUDA..................................................................................31

Figura 3.7:Operaciones de memoria gather (reunión) y scatter (dispersión).......................31

Figura 3.8:Shared memory...................................................................................................32

Figura 3.9: Grid, bloques e hilos..........................................................................................34

Figura 3.10:Acceso a diferentes espacios de memoria.........................................................35

Figura 3.11:Arquitectura de la GPU Tesla C1060 de NVidia..............................................36

Figura 3.12:Conjunto de multiprocesadores SIMD con memoria compartida on-chip.......37

Figura 4.1:Funcionamiento del algoritmo PPI.....................................................................46

Figura 5.1:Almacenamiento de los Skewers........................................................................49

Figura 5.2:Almacenamiento de los resultados parciales......................................................50

Figura 5.3:Agrupación de resultados....................................................................................53

Figura 5.4:CUDA Occupancy Calculator.............................................................................54

Figura 5.5:CUDA Occupancy Calculator:Gráfica asociada al número de hilos por bloque55

Figura 5.6:CUDA Occupancy Calculator:Gráfica asociada al número de registros por hilo

..............................................................................................................................................56

Figura 5.7: CUDA Occupancy Calculator:Gráfica asociada a la cantidad de memoria

compartida usada por cada bloque.......................................................................................57

Figura 5.8:CUDA Visual Profiler.........................................................................................59

Figura 5.9:CUDA Visual Profiler: Propiedades de la sesión................................................60

Figura 5.10:CUDA Visual Profiler: resultados parte 1.........................................................60

Figura 5.11:CUDA Visual Profiler: resultados parte 1.........................................................61

Figura 5.12:CUDA Visual Profiler: Gráfica resumen..........................................................61

Figura 5.13:CUDA Visual Profiler: Gráfica de tiempos......................................................62

Figura 6.1:Regiones y asignación de abundancias para la primera imagen sintética...........64

Figura 6.2:Mapas de abundancia empleados en la generación de la primera imagen

sintética. a) Mapa de abundancia para el endmember suelo. b) Mapa de abundancia para el

endmember vegetación.........................................................................................................65

Figura 6.3: Segunda imagen sintética. a) Distribución en la imagen de los cinco píxeles

puros (endmembers), denotados como r1, r2, r3, r4 y r5. b-f) Mapas de abundancia

empleados en la generación de la segunda imagen sintética................................................66

Figura 6.4:Ubicación de la imagen real AVIRIS Cuprite sobre una fotografía aérea de la

región minera Cuprite, Nevada, Estados Unidos.................................................................67

Figura 6.5:Precisión estricta PPI en imagen sintética 1.......................................................68

Trabajo Fin de Máster

7

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 6.6:Precisión estricta PPI en imagen sintética 2.......................................................69

Figura 6.7:Precisión ponderada PPI en imagen sintética 1..................................................70

Figura 6.8:Precisión ponderada PPI en imagen sintética 2..................................................71

Figura 6.9:Resultados gráficos de PPI para la imagen sintética 1........................................73

Figura 6.10:Resultados gráficos de PPI para la imagen sintética 2......................................75

Figura 6.11:Resultados visuales para las versiones C y ENVI en imagen real....................76

Figura 6.12:Resultados visuales para las versiones CUDA y ENVI en imagen real...........77

Figura 6.13:Ejemplo de materiales detectados.....................................................................78

Figura 8.1:Vectores operandos (v_A, v_B) y resultado (v_C) para suma de vectores.........86

Figura 8.2:Partición lógica del problema en bloques...........................................................86

Figura 8.3:Comparación de código de función C y kernel CUDA......................................88

Trabajo Fin de Máster

8

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Índice de tablas

Tabla 3.1: Lecturas y escrituras en los diferentes tipos de memoria....................................34

Tabla 3.2:Especificaciones técnicas de la GPU Tesla C1060 de NVidia.............................36

Tabla 3.3:Recursos y limitaciones según la GPU que utilicemos para programar CUDA. .40

Tabla 3.4:Capacidad de cómputo y número de multiprocesadores de cada GPU de Nvidia

..............................................................................................................................................42

Tabla 5.1:CUDA Occupancy Calculator:Parámetros introducidos......................................54

Tabla 5.2:CUDA Occupancy Calculator: Resultados calculados en función de los

parámetros............................................................................................................................55

Tabla 6.1: Comparación de resultados CPU y GPU para PPI en imagen sintética 1...........72

Tabla 6.2: Comparación de resultados CPU y GPU para PPI en imagen sintética 2...........74

Tabla 6.3:Comparación de resultados para las versiones C (CPU), CUDA (GPU) y ENVI

(CPU) para 15360 iteraciones..............................................................................................75

Trabajo Fin de Máster

9

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

1 Motivaciones y Objetivos

1.1 Motivaciones

El presente trabajo se ha desarrollado dentro de las líneas de investigación actuales

del Grupo Hypercomp de la Universidad de Extremadura, y consiste en la implementación

eficiente de un algoritmo para extracción de referencias espectrales puras o endmembers

en imágenes hiperespectrales haciendo uso de GPUs para acelerar los cómputos relativos a

la extracción de endmembers. En concreto el algoritmo implementado es: Píxel Purity

Index (PPI). Las aplicaciones potenciales de este algoritmo son múltiples, destacando

aplicaciones de detección de minerales, aplicaciones militares tales como detección de

material armamentístico camuflado, anomalías, identificación de agentes contaminantes en

aguas y atmósfera, etc.

Conviene destacar los algoritmos de análisis hiperespectral generalmente necesitan

grandes cantidades de tiempo a la hora de proporcionar resultados, debido a la complejidad

computacional de los mismos (en el caso de PPI, el algoritmo deben ejecutar un gran

número de iteraciones) y también debido al gran tamaño de las imágenes a procesar, lo cual

requiere que la transferencia de datos entre el procesador y el dispositivo hardware

especializado utilizado como coprocesador deba optimizarse. Al requerir tantas iteraciones,

y tener dentro de estas operaciones no triviales, los algoritmos de análisis hiperespectral

generalmente se traducen en un consumo de CPU elevado, por lo que la utilización de

arquitecturas especializadas como coprocesadores puede resultar una alternativa altamente

interesante.

Hasta la fecha, las técnicas tradicionales en la literatura para abordar este problema han

optado por soluciones basadas en el uso de clusters y sistemas multiprocesador. La

computación cluster, a pesar de su adaptabilidad al problema del tratamiento de datos

hiperspectrales (especialmente, cuando dichos datos se encuentran almacenados en un

repositorio de datos en tierra), presenta problemas en cuanto al procesamiento de los datos

en tiempo real dado el alto coste y elevados requerimientos en cuanto a espacio, peso y

consumo (denominado payload en misiones de observación remota de la tierra). Por otra

Trabajo Fin de Máster

10

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

parte, la instalación de un cluster suele llevar asociada la disponibilidad de un número

elevado de ordenadores interconectados entre sí para que compartan el procesamiento de

datos a través de sus procesadores, lo cual hace incrementar la velocidad de ejecución y

procesamiento de las aplicaciones; sin embargo, cada nodo (u ordenador) lleva ligado un

precio y una serie de requerimientos en cuanto a espacio y consumo que alejan esta

aproximación de las características requeridas en cuanto a payload en misiones reales de

observación remota de la tierra.

Para solucionar estos problemas relativos a coste, consumo y peso, y además ofrecer

además mejoras sustanciales en cuanto al tiempo de procesamiento, en el presente TFM

proponemos una alternativa basada en un nuevo modelo de tratamiento de imágenes

hiperespectrales basado en la utilización de GPUs. Conviene destacar que, con una sola

GPU, pueden llegar a obtenerse mejoras notables a la hora de procesar cálculos de tipo

científico, como es el caso de los algoritmos de tratamiento de imágenes hiperespectrales, a

un coste razonable (no más de 400 euros) y además ocupando un espacio mínimo. No

obstante, no todas las tarjetas GPU disponibles en el mercado se ajustan a nuestros

requerimientos. Finalmente, indicar que en este trabajo se ha intentado ir un poco más allá,

y para trabajar de forma totalmente innovadora se ha utilizado la arquitectura CUDA

incorporada en las tarjetas gráficas de NVIDIA de las series 8 (o superiores), Quadro y

Tesla, siendo algunas de las tarjetas de la primera gama las que han sido objeto de estudio

en este TFM.

Para la realización de este trabajo se ha utilizado una maquina con un procesador

Intel Core i7 920 una GPU NVidia Tesla C1060 y el sistema operativo Linux Ubuntu 9.04.

Por otra parte otra de las actividades desarrolladas en el presente trabajo consiste en la

realización de un estudio cuantitativo y comparativo del algoritmo implementado tanto en

C++ para su ejecución en la CPU como en CUDA para su ejecución en la GPU así como

un análisis de la precisión de los resultados obtenidos.

1.2 Objetivos

Este trabajo pretende desarrollar sobre una GPU la implementación de un algoritmo

para la extracción de endmembers en imágenes hiperespectrales y establecer un estudio

cualitativo y comparativo de los resultados obtenidos tras la ejecución. Concretamente el

Trabajo Fin de Máster

11

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

algoritmo es: Píxel Purity Index (PPI) .

La consecución del objetivo general anteriormente mencionado se lleva a cabo en la

presente memoria abordando una serie de objetivos específicos, los cuales se enumeran a

continuación:

• Establecer un estudio sobre la utilidad y el funcionamiento del algoritmo PPI para

extraer el grado de paralelismo inherente que presenta y utilizarlo para su

implementación.

• Realizar un estudio sobre el lenguaje

de programación CUDA para poder

implementar los algoritmos.

• Implementar el algoritmo para su ejecución en la GPU y optimizar el tiempo de

ejecución.

• Implementar una serie de aplicaciones que nos permitan conocer la precisión que se

ha logrado en la ejecución del algoritmo para dos imágenes sintéticas de las cuales

se conocen previamente sus características.

• Realizar un estudio comparativo sobre los resultados obtenidos.

Teniendo presentes los anteriores objetivos concretos, procedemos a describir la

organización del resto de esta memoria, estructurada en una serie de capítulos cuyos

contenidos se describen a continuación:

2)

Introducción. En este capítulo introductorio se describen los conceptos

fundamentales relacionados con análisis hiperespectral y procesamiento de

datos, enfatizando la necesidad de técnicas de procesamiento paralelo en este

campo y proponiendo la utilización de las GPUs como procesador paralelo

para este tipo de técnicas.

3)

GPU. Este capítulo está dedicado a la GPU, hablaremos de cómo han ido

evolucionando las GPUs programables, de los recursos que ofrecen y su

capacidad de computo. Introduciremos una serie de conceptos para lograr

entender cómo se lleva a cabo el procesamiento en una GPU mediante

CUDA. Este capítulo también describe el hardware de la tarjeta Tesla C1060

con la que se ha realizado el trabajo.

4)

Método. Este capítulo describe y muestra la utilidad del algoritmo

Trabajo Fin de Máster

12

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

implementado para el análisis hiperespectral así como su funcionamiento y

filosofía.

5)

Procesamiento paralelo en GPU. En este capítulo se muestra como se lleva

a cabo el procesamiento paralelo en la GPU para el caso que nos ocupa,

centrándonos en cada una de las fases del algoritmo por separado.

6)

Resultados. En este capítulo se describen las imágenes que se han utilizado

para probar el algoritmo, se muestran las diferentes formas de calcular la

precisión, se muestran los resultados conseguidos y finalmente se comparan.

7)

Conclusiones y líneas futuras. Este capítulo está dedicado a resumir las

principales aportaciones realizadas por la presente memoria y a mostrar las

conclusiones derivadas. Además, el capítulo sugiere un conjunto de líneas de

trabajo que pueden ser abordadas en futuros trabajos. La memoria concluye

con una serie de referencias bibliográficas utilizadas en el estudio.

8)

Apéndice. En este capítulo se expone una guía de programación básica de

CUDA y se muestra el código de los algoritmos implementados tanto en C+

+ como en CUDA. También se muestra el código del algoritmo utilizado

para calcular la precisión de los resultados.

Trabajo Fin de Máster

13

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

2 Introducción

El presente capítulo se organiza de la siguiente forma. En primer lugar, describimos

el concepto de imagen hiperespectral, detallando las particularidades y características

propias de este tipo de imágenes de alta dimensionalidad. A continuación, describimos

algunas características genéricas de los sensores de adquisición de este tipo de datos,

haciendo énfasis en los sensores utilizados en el presente trabajo. Seguidamente, se

muestra una visión general de las técnicas de desmezclado disponibles en la actualidad,

con particular énfasis en el modelo lineal de mezcla, utilizado en el presente trabajo para

abordar el problema de la caracterización sub-píxel de una imagen hiperespectral a partir

de la identificación de los píxels espectralmente más puros en la misma. El capítulo

concluye destacando la necesidad de paralelismo en este campo y mostrando el papel de

las GPU para su tratamiento.

2.1 Concepto de imagen hiperespectral

El asentamiento de la tecnología hiperespectral en aplicaciones de observación

remota de la tierra ha dado como resultado el desarrollo de instrumentos de medida de muy

elevada resolución en los dominios espacial y espectral. Los sensores hiperespectrales

adquieren imágenes digitales en una gran cantidad de canales espectrales muy cercanos

entre sí, obteniendo, para cada porción de la escena o píxel, una firma espectral

característica de cada material.

El resultado de la toma de datos por parte de un sensor hiperespectral sobre una

determinada escena puede ser representado en forma de cubo de datos, con dos

dimensiones para representar la ubicación espacial de un píxel, y una tercera dimensión

que representa la singularidad espectral de cada píxel en diferentes longitudes de onda [ 1

]. La Figura 2.1 muestra la estructura de una imagen hiperespectral donde el eje X es el

indicador de las líneas, el eje Y es el indicador de las muestras y el eje Z es el número de

bandas, es decir, la longitud de onda de esa banda (canal).

Trabajo Fin de Máster

14

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 2.1:Concepto de imagen hiperespectral

Como puede apreciarse en la Figura 2.1, el resultado de la toma de datos por parte

de un sensor hiperespectral sobre una determinada escena puede ser representado en forma

de cubo de datos, con dos dimensiones para representar la ubicación espacial de un píxel, y

una tercera dimensión que representa la singularidad espectral de cada píxel en diferentes

longitudes de onda. En concreto, la capacidad de observación de los sensores denominados

hiperespectrales permite la obtención de una firma espectral detallada para cada píxel de la

imagen, dada por los valores de reflectancia adquiridos por el sensor en diferentes

longitudes de onda, lo cual permite una caracterización muy precisa de la superficie de

nuestro planeta. Como ejemplo ilustrativo, la Figura 2.2 muestra el procedimiento de

análisis hiperespectral mediante un sencillo diagrama, en el que se ha considerado como

ejemplo el sensor AVIRIS (Airborne Visible Infra-Red Imaging Spectrometer),

desarrollado por NASA/Jet Propulsión Laboratory, el cual cubre el rango de longitudes de

onda entre 0.4 y 2.5 nm utilizando 224 canales y resolución espectral de aproximadamente

10 nm.

Trabajo Fin de Máster

15

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 2.2:Adquisición de una imagen hiperespectral por el sensor AVIRIS

Como puede apreciarse en la Figura 2.2, la capacidad de observación de este sensor

permite la obtención de una firma espectral detallada para cada píxel de la imagen, dada

por los valores de reflectancia adquiridos por el sensor en diferentes longitudes de onda, lo

cual permite una caracterización muy precisa de la superficie de nuestro planeta. Conviene

destacar que, en este tipo de imágenes, es habitual la existencia de mezclas a nivel de

subpíxel, por lo que a grandes rasgos podemos encontrar dos tipos de píxeles en estas

imágenes: píxel puros y píxel mezcla [ 2 ]. Se puede definir un píxel mezcla como aquel en

el que cohabitan diferentes materiales. Este tipo de píxel son los que constituyen la mayor

parte de la imagen hiperespectral, en parte, debido a que este fenómeno es independiente

de la escala considerada ya que tiene lugar incluso a niveles microscópicos [ 3 ]. La Figura

2.3 muestra un ejemplo del proceso de adquisición de píxeles puros (a nivel macroscópico)

y mezcla en imágenes hiperespectrales.

Trabajo Fin de Máster

16

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 2.3:Tipos de pixeles en imagenes hiperespectrales

El desarrollo tecnológico introducido por la incorporación de sensores

hiperespectrales en plataformas de observación remota de la tierra de última generación ha

sido particularmente notable durante los últimos años. En este sentido, conviene destacar

que dos de las principales plataformas de tipo satélite que se encuentran en funcionamiento

en la actualidad: Earth Observing-1 de NASA (http://eo1.gsfc.nasa.gov) y ENVISAT de la

Agencia Espacial Europea (http://envisat.esa.int), llevan incorporados sensores de este

tipo, permitiendo así la posibilidad de obtener imágenes hiperespectrales de la práctica

totalidad del planeta de manera casi continua. A pesar de la gran evolución en los

instrumentos de observación remota de la tierra, la evolución en las técnicas de análisis de

los datos proporcionados por dichos sensores no ha sido tan notoria. En particular, la

obtención de técnicas de análisis hiperespectral avanzadas, capaces de aprovechar

totalmente la gran cantidad de información espacial y espectral presente en imágenes

hiperespectrales, constituye un objetivo de gran interés para la comunidad científica. A

continuación, describimos en detalle las características del sensor hiperespectral utilizado

en el presente estudio.

2.2 Sensores hiperespectrales considerados

En la actualidad, existe una amplia gama de sensores hiperespectrales de

observación remota de la tierra. Dichos sensores pueden clasificarse según el modo en que

son transportados (plataforma de transporte) en el momento de la toma de datos [ 4 - 6 ].

La mayor parte de los sensores hiperespectrales actuales son aerotransportados (siendo el

Trabajo Fin de Máster

17

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

ejemplo más claro de este tipo de instrumentos el sensor AVIRIS, considerado en el

presente trabajo).

AVIRIS es un sensor hiperespectral aerotransportado con capacidades analíticas en

las zonas visible e infrarroja del espectro [ 8 - 10 ]. Este sensor está en funcionamiento

desde 1987. Fue el primer sistema de adquisición de imágenes capaz de obtener

información en una gran cantidad de bandas espectrales estrechas y casi contiguas. AVIRIS

es un instrumento único en el mundo de la teledetección, pues permite obtener información

espectral en 224 canales espectrales contiguos, cubriendo un rango de longitudes de onda

entre 0.4 y 2.5 m, siendo el ancho entre las bandas muy pequeño, aproximadamente 0.01

m.

En 1989, AVIRIS se convirtió en un instrumento aerotransportado. Desde ese

momento, se realizan varias campañas de vuelo cada año para tomar datos mediante

AVIRIS. El sensor ha realizado tomas de datos en Estados Unidos, Canadá y Europa,

utilizando para ello dos plataformas:

• Un avión ER-2 perteneciente a NASA/Jet Propulsion Laboratory. El ER-2 puede

volar a un máximo de 20 km sobre el nivel del mar, a una velocidad máxima de

aproximadamente 730 km/h.

• Un avión denominado Twin Otter, capaz de volar a un máximo de 4 km sobre el

nivel del mar, a velocidades de 130 km/h.

Algunas de las características más relevantes en cuanto al diseño interno del sensor

AVIRIS son las siguientes:

• El sensor utiliza un explorador de barrido que permite obtener un total de 614

píxeles por cada oscilación.

• La cobertura de la parte visible del espectro es realizada por un espectrómetro

EFOS- A, compuesto por un array de 32 detectores lineales.

• La cobertura en el infrarrojo es realizada por los espectrómetros EFOS-B, EFOS-C

y EFOS-D, compuestos todos ellos por arrays de 64 detectores lineales.

• La señal medida por cada detector se amplifica y se codifica utilizando 12 bits. Esta

señal se almacena en una memoria intermedia donde es sometida a una etapa de pre

Trabajo Fin de Máster

18

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

procesado, siendo registrada a continuación en una cinta de alta densidad de 10.4

GB a velocidad de 20.4 MB/s.

• El sensor dispone de un sistema de calibración a bordo, que utiliza una lámpara

halógena de cuarzo que proporciona la radiación de referencia necesaria para

comprobar el estado de los diferentes espectrómetros.

• A lo largo de los últimos años, el sensor ha ido mejorando sus prestaciones en

cuanto a la relación señal-ruido, como se muestra en la Figura 2.4 que describe la

evolución de la relación SNR del sensor a lo largo de los últimos años.

Figura 2.4:Evolución de la relación SNR del sensor AVIRIS de NASA

2.3 Técnicas de análisis hiperespectral y necesidad de

paralelismo

La mayoría de las técnicas de análisis hiperespectral desarrolladas hasta la fecha

presuponen que la medición obtenida por el sensor en un determinado píxel viene dada por

la contribución de diferentes materiales que residen a nivel sub-píxel. El fenómeno de la

mezcla puede venir ocasionado por una insuficiente resolución espacial del sensor, pero lo

cierto es que este fenómeno ocurre de forma natural en el mundo real, incluso a niveles

microscópicos, por lo que el diseño de técnicas capaces de modelar este fenómeno de

manera adecuada resulta imprescindible. No obstante, las técnicas basadas en este modelo

son altamente costosas desde el punto de vista computacional. A continuación, detallamos

las características genéricas de las técnicas basadas en este modelo y hacemos énfasis en la

Trabajo Fin de Máster

19

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

necesidad de técnicas paralelas para optimizar su rendimiento computacional.

Técnicas basadas en el modelo lineal de mezcla

El modelo lineal de mezcla expresa los píxeles mezcla [ 11 ] como una

combinación lineal de firmas asociadas a componentes espectralmente puros (llamados

endmembers) en la imagen [ 12 ]. Este modelo ofrece resultados satisfactorios cuando los

componentes que residen a nivel sub-píxel aparecen espacialmente separados, situación en

la que los fenómenos de absorción y reflexión de la radiación electromagnética incidente

pueden ser caracterizados siguiendo un patrón estrictamente lineal. En la actualidad, el

modelo lineal de mezcla es el más utilizado en análisis hiperespectral, debido a su sencillez

y generalidad.

Figura 2.5:Interpretación gráfica del modelo lineal de mezcla

El modelo lineal de mezcla puede interpretarse de forma gráfica en un espacio

bidimensional utilizando un diagrama de dispersión entre dos bandas poco correlacionadas

de la imagen, tal y como se muestra en la Figura 2.5. En la misma, puede apreciarse que

todos los puntos de la imagen quedan englobados dentro del triángulo formado por los tres

puntos más extremos (elementos espectralmente más puros). Los vectores asociados a

dichos puntos constituyen un nuevo sistema de coordenadas con origen en el centroide de

la nube de puntos, de forma que cualquier punto de la imagen puede expresarse como

Trabajo Fin de Máster

20

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

combinación lineal de los puntos más extremos, siendo estos puntos los mejores candidatos

para ser seleccionados como endmembers [ 13 ]. El paso clave a la hora de aplicar el

modelo lineal de mezcla consiste en identificar de forma correcta los elementos extremos

de la nube de puntos N-dimensional. En la literatura reciente se han propuesto numerosas

aproximaciones

al

problema

de

identificación

de

endmembers

en

imágenes

hiperespectrales. Por ejemplo, el método Píxel Purity Index (PPI) [ 9 ] se basa en la

generación repetitiva de vectores unitarios con orientación aleatoria en la nube de puntos

de forma que todos los puntos de la imagen hiperespectral se proyectan sobre cada vector

unitario, identificando los puntos extremos en la dirección definida por dicho vector e

incrementando un contador asociado a dichos puntos. Tras la ejecución de un número

amplio de iteraciones, se obtiene como resultado una imagen de pureza, formada por los

índices asociados a cada uno de los píxeles de la imagen, a partir de la cual se extrae un

conjunto final de endmembers utilizando técnicas de análisis y visualización interactiva.

Por su parte, el método N-FINDR utiliza un procedimiento totalmente automático para

extraer endmembers basado en identificar los vértices del simplex de mayor volumen que

puede formarse en la nube de puntos.

Necesidad de paralelismo

Conviene destacar que las técnicas de análisis hiperespectral anteriormente

descritas se basan en la realización de operaciones matriciales que resultan muy costosas

desde el punto de vista computacional [ 14 ]. Sin embargo, el carácter repetitivo de estas

operaciones las hace altamente susceptibles de ser implementadas en diferentes tipos de

arquitecturas paralelas, permitiendo así un incremento significativo de su rendimiento en

términos computacionales y dotando a dichas técnicas de la capacidad de producir una

respuesta rápida. Esta tarea es clave para la explotación de dichas técnicas en aplicaciones

que requieren una respuesta en tiempo casi real.

Las técnicas de computación paralela han sido ampliamente utilizadas para llevar a

cabo tareas de procesamiento de imágenes de gran dimensionalidad, facilitando la

obtención de tiempos de respuesta muy reducidos y pudiendo utilizar diferentes tipos de

arquitecturas [ 15 - 17 ]. En la actualidad, es posible obtener arquitecturas paralelas de bajo

Trabajo Fin de Máster

21

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

coste mediante la utilización de GPUs de última generación que cuentan con múltiples

procesadores.

El papel de las GPUs

La extracción de endmembers es una tarea crucial en la explotación de datos

hiperespectrales. En la última década se han desarrollado muchos algoritmos para la

extracción automática de endmembers desde un conjunto de datos hiperespectrales,

incluidos PPI, N-FINDR, análisis de componentes vértices, o IEA. Estas técnicas tratan los

datos hiperespectrales no como una imagen sino como una lista desordenada de

dimensiones espectrales, donde las coordenadas espaciales se pueden cambiar de forma

aleatoria sin que esto afecte al proceso de búsqueda de endmembers.

A pesar de que el desarrollo espacial y espectral es una promesa para el análisis

científico de imágenes terrestres, introduce un nuevo reto de procesamiento

particularmente para conjunto de datos de alta dimensionalidad. Desde un punto de vista

computacional cada algoritmo muestra un patrón de acceso a los datos regular y que

muestra un paralelismo inherente a muchos niveles: a nivel de vectores de píxeles, a nivel

de información espectral e incluso a nivel de tarea. Como resultado se asocian con sistemas

paralelos compuestos por CPUs (por ejemplo clusters Beowulf). Desafortunadamente estos

sistemas son caros y difíciles de adaptar a bordo de escenarios de procesamiento de

sensación remota.

Un nuevo desarrollo en el campo de la computación surge con los procesadores

gráficos programables (GPUs). Guiadas por la creciente demanda de la industria de los

videojuegos, las GPUs han evolucionado como sistemas programables altamente paralelos.

Sin embargo la arquitectura de las GPUs no encaja necesariamente con todos los tipos de

computación paralela.

En especial, el siempre creciente requerimiento computacional introducido por el

estado actual de los algoritmos de imágenes hiperespectrales pueden beneficiarse de este

hardware y tomar ventaja de su poco peso y bajo coste de sus unidades, lo que lo hace

llamativo para el procesamiento de datos a bordo por un coste mucho más bajo del que

tienen otros dispositivos hardware como las FPGAs.

Trabajo Fin de Máster

22

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

3 Tarjetas gráficas programables GPUs

En este capítulo hablamos de cómo han ido evolucionando las GPUs programables,

de los recursos que ofrecen y su capacidad de computo. Introduciremos una serie de

conceptos para lograr entender cómo se lleva a cabo el procesamiento en una GPU

mediante CUDA. Describiremos el hardware de la tarjeta Tesla C1060 con la que se ha

realizado el trabajo y finalmente trataremos el lenguaje CUDA en si dando unas nociones

básicas para llevar a cabo cualquier proyecto con este lenguaje.

3.1 Las GPUs como un dispositivo de procesamiento de datos

en paralelo

Desde un tiempo a esta parte, las GPUs programables han evolucionado como un

elemento con una gran carga de trabajo, como podemos apreciar en las Figuras 3.1 y 3.2

donde se muestra una comparativa de la evolución de la capacidad de computo y del ancho

de banda de las CPUs y las GPUs. Con múltiples núcleos y con un gran ancho de banda de

memoria, hoy por hoy las GPUs ofrecen prestaciones muy elevadas para procesamiento

gráfico y científico [ 19 - 22 ].

Figura 3.1: Operaciones en coma flotante por segundo para CPU y GPU

Trabajo Fin de Máster

23

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.2:Ancho de banda CPU y GPU

Antes de examinar en detalle la arquitectura de una GPU Tesla C1060 de NVidia

(http://www.nvidia.com), consideramos relevante explicar cómo han funcionado las

operaciones en un pipeline de una GPU clásica a lo largo de los años. No obstante, para

entender este proceso, también debemos introducir los conceptos de vertex shaders y los

píxel shaders.

Vortex shaders y píxel shaders

Los shaders son pequeños programas que se encargan del procesamiento de vértices

(vertex shaders) y de píxeles (píxel shaders). La principal ventaja es que pueden ser

programados por el desarrollador, otorgando una flexibilidad que hasta antes de la

aparición de los shaders era algo impensable. Recursos como las operaciones condicionales

o los saltos se utilizan de forma similar que en los lenguajes más conocidos. Sin los

shaders, muchos de los efectos eran realizados en conjunto con la unidad de procesamiento

central, disminuyendo en gran medida el rendimiento y limitando el avance a nivel gráfico

de los mismos.

Un vertex shader es una función que recibe como parámetro un vértice. Sólo trabaja

con un vértice a la vez, y no puede eliminarlo, sólo transformarlo. Para ello, modifica

propiedades del mismo para que repercutan en la geometría del objeto al que pertenece.

Trabajo Fin de Máster

24

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Con esto se pueden lograr ciertos efectos específicos, como los que tienen que ver con la

deformación en tiempo real de un elemento; por ejemplo, el movimiento de una ola. Donde

toma una gran importancia es en el tratamiento de las superficies curvas.

En cambio, un píxel shader básicamente especifica el color de un píxel. Este

tratamiento individual de los píxeles permite que se realicen cálculos principalmente

relacionados con la iluminación del elemento del cual forman parte en la escena, y en

tiempo real.

La incorporación de los píxel shaders y vertex shaders permite a los programadores

una mayor libertad a la hora de diseñar gráficos en tres dimensiones, ya que puede tratarse

a cada píxel y cada vértice por separado. De esta manera, los efectos especiales y de

iluminación pueden crearse mucho más detalladamente, sucediendo lo mismo con la

geometría de los objetos.

Pipeline clásico de procesamiento en una GPU

Cuando revisamos las arquitecturas hardware, el flujo de datos, y las operaciones

pipeline, a menudo es bueno empezar por el nivel más alto, donde los datos llegan desde la

CPU a la GPU, y el proceso se desarrolla hacia abajo a través de múltiples fases de

procesamiento hasta que un píxel es dibujado definitivamente en la pantalla. Para

situarnos, las GPUs han utilizado diseños pipeline tradicionales, como los que aparecen

ilustrados en la Figura 3.3.

Trabajo Fin de Máster

25

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.3:Pipeline clásico de procesamiento en una GPU

Después de que la GPU recibe los datos vertex (vértices) desde el host (CPU), la

fase vertex se ejecuta en primer lugar. La función de fijado transforma la imagen y el

hardware de luminosidad operado en esta fase se lleva a cabo; entonces los píxeles shaders

programables, y el control de flujo dinámico de los modelos shaders entran en juego. El

siguiente paso en el pipeline clásico es la configuración, donde los vértices son

ensamblados dentro de primitivas como triángulos, líneas o puntos. Las primitivas son

convertidas por la fase de “rasterización” en fragmentos de píxeles (o simplemente

fragmentos), pero no son considerados píxeles completos en esta fase. Los fragmentos

están sometidos a muchas otras operaciones como sombreado, Z-testing, la posible mezcla

en el buffer frame, y el antialiasing. Los fragmentos son finalmente considerados píxeles

cuando han sido escritos en el buffer frame.

A continuación, la siguiente fase es la de píxel shader, que debería ser denominada

técnicamente como fase fragment shader, pero utilizamos la notación estándar en la

literatura [ 19 - 22 ] debido a su aceptación. En el pasado, los fragmentos sólo podían haber

tenido valores de color aplicados de textura simple. Hoy en día, la capacidad de sombreado

de un píxel programado de la GPU permite numerosos efectos de sombreado para ser

aplicados mientras se trabaja de acuerdo con métodos complejos de multitextura.

Específicamente, los fragmentos sombreados (con color y valores Z) desde esta fase píxel

Trabajo Fin de Máster

26

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

son enviados al ROP (Raster Operations). La fase ROP es donde se chequea el buffer Z

para asegurar que sólo los fragmentos visibles son procesados rápidamente, y los

fragmentos visibles, si son parcialmente transparentes, son mezclados con el buffer de

frame existente, junto con los píxeles y aplicándoles antialiased. El píxel procesado final es

enviado a la memoria buffer para ser escaneado y visualizado en el monitor [ 19 ].

Evolución del uso de GPUs en aplicaciones científicas

La principal razón que justifica la gran popularidad de las arquitecturas GPU en

aplicaciones científicas es el hecho de que la GPU está especializada para cómputo

intensivo, computación paralela elevada (exactamente sobre lo que trata el renderizado de

gráficos) y por tanto se designan más transistores dedicados al procesamiento de datos, que

a la recolección de datos y control de flujo como se muestra en la Figura 3.4.

Figura 3.4:La GPU proporciona más transistores para el procesamiento de datos

Más específicamente, la GPU está especialmente pensada para direccionar

problemas que pueden ser expresados como computaciones de datos paralelos (el mismo

programa es ejecutado en muchos elementos de datos en paralelo) con gran intensidad

aritmética (el ratio de operaciones aritméticas respecto a operaciones de memoria). Como

el mismo programa es ejecutado para cada elemento de datos, hay menos requisitos para

un flujo de control sofisticado; y como es ejecutado en muchos elementos de datos y tiene

gran intensidad aritmética, la latencia de acceso a memoria puede ser ocultada con

cálculos, en vez de datos muy grandes de caché [ 20 ].

Trabajo Fin de Máster

27

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

El procesamiento de datos paralelos asocia los datos a elementos de proceso

paralelos. Muchas aplicaciones que procesan grandes conjuntos de datos como arrays

pueden usar un modelo de programación de datos paralelos para acelerar los cálculos. En

renderizado 3D los conjuntos de píxeles y vértices se asignan a hilos paralelos. De la

misma manera, aplicaciones de procesamiento de imágenes y multimedia como

postprocesado de imágenes renderizadas, codificación y decodificación de vídeo, escalado

de imágenes, visión estéreo, y patrones de reconocimiento pueden asociar bloques de la

imagen y píxeles a hilos de procesamiento paralelo. De hecho, muchos algoritmos fuera

del campo del renderizado

como el procesamiento de señales, simulaciones físicas

finanzas o biología, se aceleran con el procesamiento de datos en paralelo.

Hasta la fecha, sin embargo, a pesar de acceder a todo el poder de computación

contenido en al GPU y usarlo eficientemente para aplicaciones científicas, seguía siendo

difícil obtener las siguientes pautas:

•

La GPU solamente podía ser programada a través de la API (Application

Programming Interface) gráfica; esto provocaba que la curva de aprendizaje

para un desarrollador principiante fuese muy elevada, ya que tenía que trabajar

con una API inadecuada, que no estaba adaptada a la aplicación científica.

•

La DRAM de la GPU podía ser leída de manera general (los programas de GPU

pueden obtener elementos de datos de cualquier parte de la DRAM) pero no se

podía escribir de manera general (los programas de GPU no pueden esparcir la

información a cualquier parte de la DRAM), eliminando mucha de la

flexibilidad de programación ya disponible en la CPU.

•

Algunas aplicaciones tenían en problema del “cuello de botella”, debido al

ancho de banda de la memoria DRAM, utilizando escasamente el poder

computacional de la GPU.

En este sentido, una de las principales motivaciones del presente TFM es demostrar

que dichas limitaciones en la actualidad pueden superarse mediante la utilización de la

arquitectura CUDA para procesamiento de datos científicos en la GPU. Dicho aspecto será

abordado en detalle en el siguiente subapartado del presente capítulo de la memoria.

Trabajo Fin de Máster

28

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

3.2 CUDA: una nueva arquitectura para el calculo en la GPU

CUDA viene del inglés Compute Unified Device Architecture y es una nueva

arquitectura hardware y software, diseñada para dar y manejar procesamientos en la GPU

como un elemento de computación de datos paralelos sin la necesidad de mapearlos a una

API de gráficos. Está disponible para las versiones GeForce 8 Series, Quadro FX

5600/4600, Tesla y Fermi. El mecanismo de multitarea del sistema operativo es

responsable de manejar el acceso a la GPU mediante CUDA, y las aplicaciones gráficas

funcionan de forma simultánea. A continuación describimos el pipeline unificado del que

disponen las actuales GPUs de NVIDIA y que puede ser explotado de forma eficiente

mediante CUDA, así como la arquitectura completa de la Tesla C1060. El apartado finaliza

describiendo los diferentes modelos de programación en CUDA.

Pipeline unificado

A partir del modelo de pipeline clásico, con sus flujos de datos empezando en lo

más alto, donde los vértices con varios atributos, índices, comandos, y texturas son pasados

a la GPU desde la CPU. Las fases de procesamiento mayores siguen una manera lineal

segura incluyendo vertex shading, píxel shading, operaciones raster, (que son operaciones a

través de las cuales un área espacial queda dividida en celdas regulares, en las que cada

una de las cuales presentan unos atributos o valor, como pueden ser la altitud, reflectancia,

etc.) y escritura de píxeles en el buffer frame.

Con este pipeline unificado y la arquitectura “shader”, el diseño de la GPU Tesla

C1060 reduce significativamente el número de fases del pipeline y cambia el flujo

secuencial para estar más orientado a bucle. Las entradas son alimentadas en la parte alta

del núcleo shader unificado, y las salidas son escritas en registros y entonces vuelven otra

vez a la parte alta del núcleo shader para la próxima operación. Como resultado, en el

diagrama GPU unificado generalizado que se muestra en la Figura 3.5, los flujos de datos

bajan secuencialmente por el pipeline a través de diferentes tipos “shader”. La figura de la

derecha representa un núcleo “shader” unificado con uno o más procesadores “shader”

unificados estandarizados.

Trabajo Fin de Máster

29

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.5:Pipeline clásico frente a pipeline unificado

Como puede apreciarse en la Figura 3.5, los datos vienen de la parte superior

izquierda del diseño unificado (como vértices), y son llevados al núcleo shader para su

procesamiento, y los resultados son enviados de vuelta a la parte superior del núcleo

shader, donde son llevados otra vez, procesados otra vez, mandados de vuelta a la parte

superior, y así hasta que todas las operaciones shader son ejecutadas y el fragmento de

píxel se pasa al subsistema ROP [ 19 ].

Modelo de programación CUDA

Antes de profundizar en el modelo de programación empleado por CUDA,

destacamos que la pila del software de CUDA se compone de varias capas, tal y como

muestra la Figura 3.6. En concreto, dichas capas son un controlador de hardware, una API

y su runtime, y dos librerías matemáticas de alto nivel para uso común, CUFFT y

CUBLAS. El hardware ha sido diseñado para soportar controladores ligeros y capas

runtime, dando como resultado una ejecución óptima. En este sentido, la API de CUDA es

una extensión del lenguaje de programación C, lo cual hace que tenga una curva de

aprendizaje mínima.

Trabajo Fin de Máster

30

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.6:Pila de software de CUDA

Por otra parte, CUDA ofrece un direccionamiento de carácter general para la

memoria DRAM como ilustra la Figura 3.7. Este modelo de direccionamiento permite

obtener mayor flexibilidad en la programación, en el sentido de que ofrece tanto la

operación de reparto de datos como la de obtención de estos. Desde una perspectiva de

programación, esto se traduce en la habilidad de leer y escribir datos en cualquier lugar de

la DRAM, exactamente igual que en la CPU [ 20 ].

Figura 3.7:Operaciones de memoria gather (reunión) y scatter (dispersión)

CUDA proporciona una memoria compartida on-chip a modo de caché de datos que

permite accesos muy rápidos de lectura y de escritura. Mediante ésta los hilos pueden

compartir datos. Como se muestra en la Figura 3.8, las aplicaciones pueden beneficiarse de

esta memoria minimizando los accesos a memoria DRAM lo que les hace menos

Trabajo Fin de Máster

31

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

dependientes del ancho de banda de la DRAM que es mucho menor que el de la shared

memory.

Figura 3.8:Shared memory

3.3 Procesamiento

En la siguiente sección presenta a la GPU como un coprocesador multihilo para la

CPU, seguidamente se exponen los diferentes mecanismos de los que se hace uso para

llevar a cabo el procesamiento en la GPU, estos son los hilos de ejecución, los bloques en

los que se organizan estos hilos y los llamados grid en los que se estructuran estos bloques.

La sección finaliza con el modelo de memoria utilizado por CUDA.

Un coprocesador multihilo

Cuando se programa con CUDA, la GPU se ve como un dispositivo de cálculo

(device) capaz de ejecutar un gran número de hilos en paralelo. Éste opera como un

coprocesador de la CPU principal, o host. En otras palabras, los datos paralelos, cálculo

intensivo de porciones de aplicaciones ejecutándose en el host son cargados en el device.

De forma más precisa, una parte de una aplicación que se ejecuta muchas veces, pero con

datos diferentes e independientes, puede ser aislada en una función que es ejecutada en el

device como muchos hilos independientes. Como dicha función es compilada, la

instrucción obtenida a partir del device (en nuestro caso, la GPU) y el programa resultante,

Trabajo Fin de Máster

32

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

llamado kernel, se descargan en el device. Tanto el host como el device mantienen su

propia DRAM, referidas como memoria del host y memoria del device respectivamente.

Una puede copiar datos de una memoria a la otra a través de llamadas a una API

optimizada, que usa el Acceso Directo a Memoria (DMA) del device [ 20 ].

Hilos, Bloques y Grids

El tratamiento por lotes de los hilos que ejecuta el kernel está organizado como un

grid de bloques de hilos, ilustrado en la Figura 3.9. Un bloque de hilos es un lote de hilos

que pueden cooperar juntos compartiendo datos eficientemente a través de la memoria

compartida y sincronizar sus ejecuciones para coordinar los accesos a memoria. De forma

precisa, uno puede especificar puntos de sincronización en el kernel, donde los hilos en un

bloque están suspendidos hasta que todos ellos alcancen el punto de sincronización. Cada

hilo es identificado por su identificador de hilo (thread ID), que es el número de hilo dentro

de un bloque [ 20 ].

Hay un número máximo de hilos que un bloque puede contener (512 hilos

concretamente). Sin embargo, los bloques de misma dimensión y tamaño que ejecutan el

mismo kernel pueden ser tratados por lotes de forma conjunta, en un grid de bloques, así

que el número total de hilos puede ser lanzado en una única invocación del kernel es

mucho más grande. Esto se debe al gasto de reducir la cooperación entre hilos, porque los

hilos en diferentes bloques del mismo grid no pueden comunicarse ni sincronizarse con los

de los demás. Este modelo permite a los kernels ejecutarse eficientemente sin

recompilación en varios devices con diferentes capacidades paralelas: un device puede

ejecutar todos los bloques de un grid secuencialmente si tiene poca capacidad, o en

paralelo si tiene mucha, o normalmente una combinación de ambas [ 20 ]. La Figura 3.9

muestra como cada kernel se ejecuta como un grid de bloques de hilos.

Trabajo Fin de Máster

33

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.9: Grid, bloques e hilos

Modelo de memoria

Un hilo que se ejecute en el device tiene solo acceso a la DRAM del device y a la

memoria on-chip a través de los siguientes espacios de memoria (Tabla 3.1) [ 20 ], como se

muestra en la Figura 3.10.

Registro de

hilo

Lectura

Escritura

Memoria

Memoria

compartida de local de hilo

bloque

✓

✓

✓

✓

✓

✓

Memoria

global de grid

Memoria

constante de

grid

Memoria de

texturas de

grid

✓

✓

✓

×

✓

×

Tabla 3.1: Lecturas y escrituras en los diferentes tipos de memoria

Los espacios de memoria global, constante y de textura pueden ser leídos o escritos

por el host y perduran durante las distintas ejecuciones del kernel en la misma aplicación.

Estos espacios se optimizan para diferentes usos de la memoria. Además la memoria de

texturas ofrece diferentes modos de direccionamiento, así como de filtrado de datos, para

diferentes formatos de datos.

Trabajo Fin de Máster

34

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.10:Acceso a diferentes espacios de memoria

3.4 Implementación hardware y modelo de ejecución

En esta sección se presenta la arquitectura hardware de la GPU utilizada en el

trabajo y se explica el modelo de ejecución que sigue CUDA.

Nvidia Tesla C1060

A lo largo de la presente memoria hemos cubierto muchos de los puntos básicos de

la programación de GPUs de NVidia, así que ahora podemos echar un vistazo a los

aspectos específicos de la arquitectura Tesla C1060 [ 19 ], la tarjeta que estamos usando

para realizar este TFM. La Figura 3.11 describe la arquitectura hardware de dicha tarjeta.

El significado de las siglas que aparecen en el esquema es el siguiente: TPC

(Texture/Processor Cluster), SM (Streaming Multiprocessor), SP (Streaming Processor),

Tex (Texture), ROP (Raster Operation Processor).

Trabajo Fin de Máster

35

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Figura 3.11:Arquitectura de la GPU Tesla C1060 de NVidia

A continuación la Tabla 3.2 muestra las características técnicas de la GPU:

Specification

Description

Form Factor

10.5" x 4.376", Dual Slot

# of Streaming Processor Cores

240

Frequency of processor cores

1.3 GHz

Single Precision floating point 933

performance (peak)

Double Precision floating point 78

performance (peak)

Floating Point Precision

IEEE 754 single & double

Total Dedicated Memory

4 GDDR3

Memory Speed

800MHz

Memory Interface

512-bit

Memory Bandwidth

102 GB/sec

Max Power Consumption

187.8 W

System Interface

PCIe x16

Auxiliary Power Connectors

6-pin & 8-pin

Thermal Solution

Active fan sink

Tabla 3.2:Especificaciones técnicas de la GPU Tesla C1060 de NVidia

Trabajo Fin de Máster

36

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Modelo de ejecución

La GPU se implementa como un conjunto de multiprocesadores como se puede ver

en la Figura 3.12. Cada multiprocesador tiene una arquitectura SIMD: en cada ciclo de

reloj, cada procesador del multiprocesador ejecuta la misma instrucción, pero opera en

datos distintos. Los espacios de memoria local y global son implementados como regiones

de la memoria del device. Cada procesador tiene acceso a la memoria compartida del

multiprocesador en el que está integrado. Cada multiprocesador accede a la cache de

textura mediante una unidad de textura que implementa los diferentes modos de

direccionamiento y filtros de datos [ 20 ].

Figura 3.12:Conjunto de multiprocesadores SIMD con memoria compartida on-chip

Un grid de bloques de hilos se ejecuta en el device mediante la programación de los

bloques en cada multiprocesador. Cada multiprocesador procesa los bloques por lotes, un

lote tras otro. Un bloque solo se procesa en un multiprocesador, así el espacio de memoria

compartida reside en la memoria on-chip compartida por lo que se puede beneficiar de la

velocidad que proporciona dicha memoria.

Trabajo Fin de Máster

37

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

El numero de bloques que cada multiprocesador puede procesar en un lote depende

de cuantos registros necesita cada hilo y de cuanta memoria compartida necesita cada

bloque en un kernel ya que estos recursos se deben compartir entre todos los hilos de los

bloques del lote. Si no hay una cantidad suficiente de registros o de memoria compartida

disponible en un multiprocesador para procesar al menos un bloque, el kernel fallará en su

ejecución.

Los bloques que se procesan en un multiprocesador en un lote se llaman activos.

Cada bloque activo se divide en grupos de hilos SIMD llamados warps. Cada uno de estos

warps contiene el mismo número de hilos, este número se llama warp size, y se ejecuta en

un multiprocesador en modo SIMD. Los warps activos (los warps de los bloques activos)

se dividen en el tiempo: un programador de hilos cambia de un warp a otro para maximizar

el uso de recursos computacionales del multiprocesador. Se llama half warp a la primera o

a la segunda mitad de un warp.

La forma en la que un bloque se divide en warps es siempre la misma; cada warp

contiene hilos consecutivos, incrementando sus identificadores de hilo (thread ID). El

primer warp contiene al hilo 0.

El orden de emisión de los warps de un bloque no esta definido y no existe un

mecanismo de sincronización entre bloques para coordinar los accesos a memoria global o

compartida.

El orden de emisión de los bloques en un grid de bloques de hilos tampoco está

definido y no hay un mecanismo de sincronización entre bloques, así que los hilos de dos

bloques diferentes pertenecientes al mismo grid no se pueden comunicar de una forma

segura a través de la memoria global durante la ejecución de un grid.

Si una instrucción no atómica ejecutada por un warp escribe en la misma posición

ya sea de memoria global o compartida por más de un hilo de warp, el número de de

escrituras serializadas que ocurran en esa posición así como el orden de las escrituras es

indefinido, pero se garantiza que al menos una escritura tenga éxito. Si una instrucción

atómica ejecutada por un warp lee, modifica o escribe en una posición de memoria ya sea

global o compartida por más de un hilo del warp, cada lectura, modificación o escritura en

la posición ocurre de forma serializada aunque el orden es indefinido.

Trabajo Fin de Máster

38

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Especificaciones generales

A continuación en la Tabla 3.3 se listan una serie de especificaciones generales que

se deben tener en cuenta a la hora de programar una GPU con CUDA para lograr una

ejecución más eficiente en función de la capacidad de computo (Compute capability) de la

GPU.

Trabajo Fin de Máster

39

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Parámetro

Valor según gener. GPU

CUDA Compute Capabilities

1.0 y 1.1 1.2 y 1.3 Fermi

Multiprocesadores / GPU

Limitación Impacto

16

30

16

HW.

Escalabilidad

8

8

32

HW.

Escalabilidad

32

32

32

SW.

Throughput

8

8

8

SW.

Throughput

Hilos / Bloque

512

512

512

SW.

Paralelismo

Hilos / Multiprocesador

768

1024 1536

SW.

Paralelismo

Registros de 32 bits / Multiproc.

8192

16384 4096

HW.

Working Set

Memoria compartida / Multiproc.

16384

16384 16 K

48K

HW.

Working Set

Procesadores / Multiprocesador

Hilos / Warp

Bloques de hilos / Multiprocesador

Tabla 3.3:Recursos y limitaciones según la GPU que utilicemos para programar CUDA

A continuación en la Tabla 3.4 se muestra la capacidad de computo y el número de

multiprocesadores de cada GPU de Nvidia.

Trabajo Fin de Máster

40

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Número de

Multiprocesadore

s

(1

Multiprocesador

= 8 Procesadores)

Compute

Capability

2x30

1.3

GeForce GTX 285, GTX 280

30

1.3

GeForce GTX 260

24

1.3

GeForce 9800 GX2

2x16

1.1

GeForce GTS 250, GTS 150, 9800 GTX,

9800 GTX+, 8800 GTS 512

16

1.1

GeForce 8800 Ultra, 8800 GTX

16

1.0

GeForce 9800 GT, 8800 GT, GTX 280M,

9800M GTX

14

1.1

GeForce GT 130, 9600 GSO, 8800 GS,

8800M GTX, GTX 260M, 9800M GT

12

1.1

GeForce 8800 GTS

12

1.0

GeForce 9600 GT, 8800M GTS, 9800M GTS

8

1.1

GeForce 9700M GT

6

1.1

GeForce GT 120, 9500 GT, 8600 GTS, 8600 GT,

9700M GT, 9650M GS, 9600M GT, 9600M GS,

9500M GS, 8700M GT, 8600M GT, 8600M GS

4

1.1

GeForce G100, 8500 GT, 8400 GS, 8400M GT,

9500M G, 9300M G, 8400M GS, 9400 mGPU,

9300 mGPU, 8300 mGPU, 8200 mGPU,

8100 mGPU

2

1.1

GeForce 9300M GS, 9200M GS, 9100M G,

8400M G

1

1.1

Tesla S1070

4x30

1.3

Tesla C1060

30

1.3

Tesla S870

4x16

1.0

Tesla D870

2x16

1.0

Tesla C870

16

1.0

Quadro Plex 2200 D2

2x30

1.3

Quadro Plex 2100 D4

4x14

1.1

GeForce GTX 295

Trabajo Fin de Máster

41

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

Quadro Plex 2100 Model S4

4x16

1.0

Quadro Plex 1000 Model IV

2.16

1.0

Quadro FX 5800

30

1.3

Quadro FX 4800

24

1.3

Quadro FX 4700 X2

2x14

1.1

Quadro FX 3700 M

16

1.1

Quadro FX 5600

16

1.0

Quadro FX 3700

14

1.1

Quadro FX 3600M

12

1.1

Quadro FX 4600

12

1.0

Quadro FX 2700 M

6

1.1

Quadro FX 1700, FX 570, NVS 320M, FX 1700M,

FX 1600M, FX 770M, FX 570M

4

1.1

Quadro FX 370, NVS 290, NVS 140M, NVS 135M,

FX 360M

2

1.1

Quadro FX 370M, NVS 130M

1

1.1

Tabla 3.4:Capacidad de cómputo y número de multiprocesadores de cada GPU de Nvidia

Trabajo Fin de Máster

42

Sergio Sánchez Martínez

Implementación de algoritmos de análisis hiperespectral en tarjetas gráficas

programables (GPUs)

4 Método

En este apartado se describe el método de extracción de endmembers considerado

en el presente estudio e implementado de forma eficiente utilizando tarjetas gráficas

programables de la gama Nvidia. La implementación paralela de este algoritmo en GPUs

será descrita en la próxima sección del presente documento.

4.1 Pixel Purity Index (PPI)

Uno de los algoritmos más satisfactorios para la extracción automática de

endmembers ha sido el método Píxel Purity Index (PPI) [ 9 ] desarrollado por Boardman,

Kruse, y Green en 1993, y que se incorporo al sistema de búsqueda ENVI de Kodak. El

algoritmo procede mediante la generación de un gran número de vectores aleatorios Ndimensionales llamados “skewers”. Cada punto de la imagen se proyecta en cada skewer y

los puntos que correspondan a los extremos en la dirección de un skewer se identifican y se

almacenan en una lista. Como se generan más skewers, la lista crece, y el número de veces

que un píxel dado se almacena en la lista también se incrementa. Los píxeles con mayores

incrementos son considerados como endmembers finales.

El algoritmo PPI pertenece al conjunto de los métodos interactivos y es el más

representativo. Su objetivo es localizar los puntos espectralmente más puros de la imagen