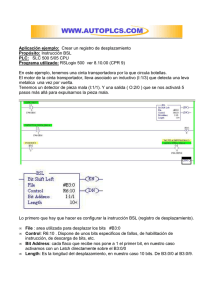

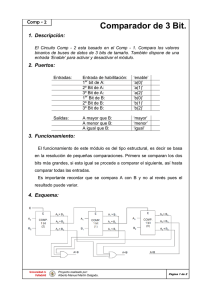

Descripción Detallada del PIC16F877

Anuncio