Científicos de la UIB diseñan métodos que puedan verificar en un

Anuncio

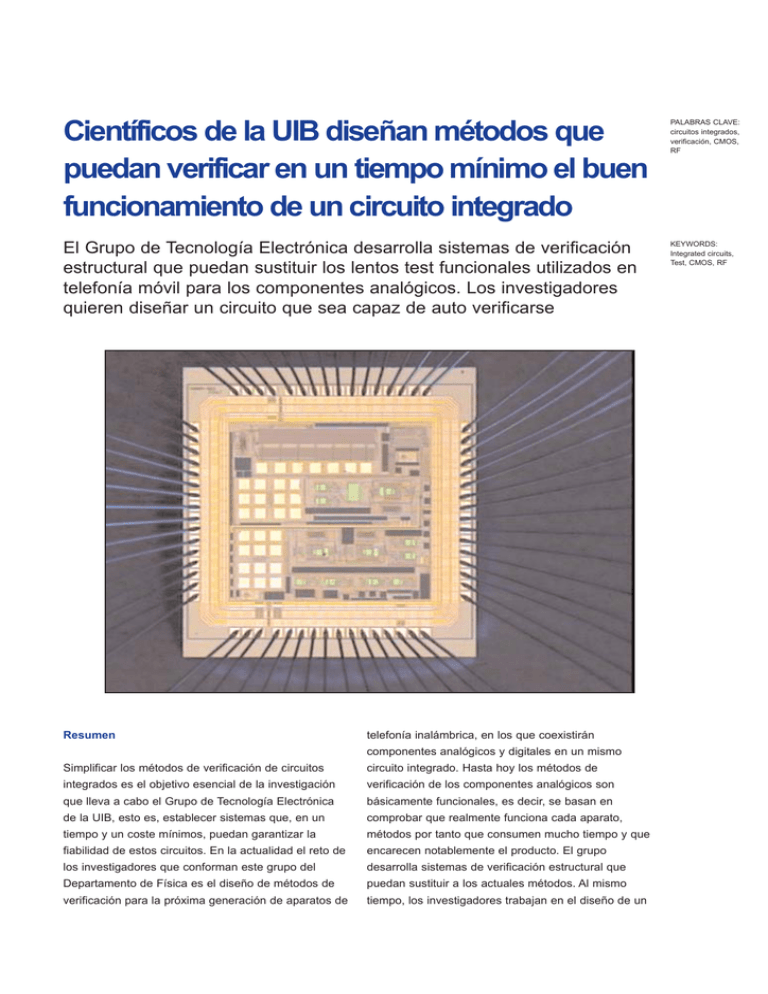

Científicos de la UIB diseñan métodos que puedan verificar en un tiempo mínimo el buen funcionamiento de un circuito integrado El Grupo de Tecnología Electrónica desarrolla sistemas de verificación estructural que puedan sustituir los lentos test funcionales utilizados en telefonía móvil para los componentes analógicos. Los investigadores quieren diseñar un circuito que sea capaz de auto verificarse Resumen telefonía inalámbrica, en los que coexistirán componentes analógicos y digitales en un mismo Simplificar los métodos de verificación de circuitos circuito integrado. Hasta hoy los métodos de integrados es el objetivo esencial de la investigación verificación de los componentes analógicos son que lleva a cabo el Grupo de Tecnología Electrónica básicamente funcionales, es decir, se basan en de la UIB, esto es, establecer sistemas que, en un comprobar que realmente funciona cada aparato, tiempo y un coste mínimos, puedan garantizar la métodos por tanto que consumen mucho tiempo y que fiabilidad de estos circuitos. En la actualidad el reto de encarecen notablemente el producto. El grupo los investigadores que conforman este grupo del desarrolla sistemas de verificación estructural que Departamento de Física es el diseño de métodos de puedan sustituir a los actuales métodos. Al mismo verificación para la próxima generación de aparatos de tiempo, los investigadores trabajan en el diseño de un PALABRAS CLAVE: circuitos integrados, verificación, CMOS, RF KEYWORDS: Integrated circuits, Test, CMOS, RF sistema de verificación que se pueda integrar en el integrado es una especie de cápsula donde se ubican propio circuito, consiguiendo así circuitos capaces de todos los componentes electrónicos necesarios para auto verificar su buen funcionamiento. realizar una función: transistores, resistencias, diodos, etc. El primer chip fue desarrollado por Jack St. Clair Kilby, ingeniero de la Texas Instruments. Kilby recibió Introducción La aparición de circuitos integrados o chips a principios de la década de los sesenta permitió el desarrollo de lo que se conoce como tercera generación de ordenadores. Fue entonces cuando empezó la miniaturización, gracias a la cual se consiguió entre otras ventajas un inferior consumo energético y una mayor fiabilidad. Esa tercera generación de ordenadores utilizaba en el año 2000 el Premio Nóbel de Física. Del primer circuito que integraba seis transistores sobre una misma base de semiconductor, hemos pasado, tal como había profetizado Gordon Moore, a circuitos no más grandes que la uña del dedo meñique, capaces de integrar más de cuatrocientos millones de transistores todavía circuitos integrados SSI y MSI, es decir, de bajas y medianas escalas de integración. Aún así se acababa de iniciar un nuevo camino, cuyas expectativas supo sintetizar Gordon Moore en 1965 De aquel primer circuito que integraba seis transistores cuando se dio cuenta de que el número de transistores sobre una misma base de semiconductor, tal como en un chip se duplicaba cada 18-24 meses. Esta había profetizado Gordon Moore, hemos pasado a observación es conocida como la ley de Moore. circuitos no más grandes que la uña del dedo meñique, capaces de integrar más de cuatrocientos Digamos, de manera introductoria, que un circuito Imagen obtenida al microscopio de un circuito integrado desarrollado por el Grupo de Tecnología Electrónica de la UIB. millones de transistores. La evolución de este proceso de integración durante cuarenta años queda reflejada sus componentes. Eso supondría un tiempo de en la manera en que son clasificados los circuitos verificación excesivo. Por regla general, el test se integrados, en función del número de componentes realiza automáticamente mediante una maquinaria que integran: de los SSI (Small Scale of Integration) o expresamente diseñada para esa labor. Dependiendo los MSI (Medium Scale of Integration) que no de la calidad del producto y de su precio, la sobrepasan los cien componentes, hasta llegar a los verificación puede realizarse sobre una muestra VLSI (Very Large Scale of Integration) y los ULSI (Ultra aleatoria de cada serie producida o bien sobre sobre Large Scale of Integration), capaces de contener más todos y cada uno de los productos (es lo de veinte millones de transistores que operan a acostumbrado, por ejemplo, en el caso de circuitos velocidades extremadamente elevadas. para satélites). De hecho, con el circuito de Kilby había nacido una nueva disciplina científica y tecnológica: la Se precisan técnicas que permitan la verificación del microelectrónica, ahora ya nanoelectrónica. buen funcionamiento de todo el circuito en un tiempo muy breve, en cuestión de segundos, si no se quiere encarecer todo el proceso productivo. Eso sólo puede Los problemas asociados a la miniaturización conseguirse mediante el llamado test de puntos clave del sistema, cuyo estado nos informe del estado de las distintas partes de ese sistema. Dicho en otras El coste de fabricación de este tipo de circuitos se ha reducido considerablemente ya que puede ser automatizada. Aun así, un tercio de ese coste corresponde a la verificación. Y es que la miniaturización lleva aparejada una serie de problemas asociados a las propiedades y a la degradación de los materiales utilizados en la construcción de los circuitos (metal, óxido, semiconductor). Nos hallamos pues ante un amplio abanico de problemas en cuya resolución trabajan un buen número de equipos de investigación en todo el mundo: las corrientes de fuga (Stress Induced Leakage Current, SILC); las pérdidas de capacidad aislante del óxido, conocidas también como roturas, etc. El grupo de Tecnología Electrónica del Departamento de Física de la UIB, dirigido por el doctor Eugeni Garcia, focaliza su investigación hacia el diseño experimental de circuitos integrados y muy especialmente hacia el desarrollo de sistemas de verificación que puedan ser aplicables a la industria. Tal como afirma el doctor Eugeni Garcia, "para un fabricante es esencial poder garantizar la fiabilidad de sus productos y, en estos momentos, la verificación de este tipo de circuitos se ha convertido en todo un reto ya que al aumentar la complejidad también se complica esa verificación". Resulta evidente que la tarea de verificar estos circuitos no puede basarse en comprobar cada uno de Fig. 1 El doctor Eugeni Garcia ante la máquina de puntas, dotada de micromanipulado res y microscopio. secuencia de entradas para trasladar el voltaje desde ese punto a uno de los pads externos (observación) i así poder compararlo con el valor esperado. Como que a cada nueva generación de chips la relación entre los puntos internos a medir y el número de pads crece, los problemas de verificación se agravan. La labor que desarrolla el grupo dirigido por el doctor Eugeni Garcia es precisamente esta: diseñar y construir prototipos de circuitos integrados que incorporen los puntos clave necesarios para que la verificación sea segura y, al mismo tiempo, rápida. La verificación en telefonía inalámbrica de última generación palabras: cualquier disfunción en el circuito es detectada por una disfunción en un punto clave determinado. Desde la década de los setenta hasta principios de los La verificación se realiza midiendo la tensión de las telefonía inalámbrica llamados de primera generación. conexiones externas (pads) del xip situadas en la Arriba y abajo: miembros del Grupo de Tecnología Electrónica en el laboratorio del edificio Mateu Orfila i Rotger, en el campus de la UIB periferia. Las reducidísimas dimensiones de los pads obligan a utilizar maquinaria dotada de micromanipuladores y adicionalmente de un microscopio, lo que comúnmente es conocido como noventa dominaron el mercado los sistemas de Estos teléfonos utilizaban tecnologías analógicas para transmitir información. Como es sabido, una señal se dice que es analógica cuando sus magnitudes se representan mediante variables continuas, sin saltos bruscos de los valores en un intervalo de tiempo máquina de puntas. (Fig. 1 ) determinado. De hecho, las magnitudes son El proceso de verificación de cada punto clave implica nos ocupa un emisor de radio frecuencia. La irrupción dos etapas. En primer lugar se aplica a los pads del circuito una determinada secuencia de valores para conseguir que el voltaje en este punto tenga un valor determinado (control). En segundo lugar se aplica otra "análogas" a las que generan la señal, en el caso que de la tecnología digital en la telefonía móvil supuso una serie de ventajas entre ellas el aumento de prestaciones y de portabilidad. Pronto empezaron a coexistir componentes analógicos y componentes digitales en un mismo aparato. En los últimos años, sin embargo, la tendencia es integrar la totalidad de los componentes en el mismo chip. El futuro de la telefonía inalámbrica pasa, por tanto, por la utilización de la tecnología CMOS VLSI (Complementary Metal Oxide Semiconductor Very Large Scale of Integration), que permite un menor consumo y una mayor inmunidad al ruido. Esta nueva tecnología tendrá que integrar tanto los componentes digitales como los analógicos. Ahora bien, mientras la verificación en circuitos integrados digitales recordemos que una señal digital responde a magnitudes físicas limitadas por valores discretos. Por ejemplo, en los ordenadores la información se codifica en un sistema binario 0,1 - está relativamente desarrolla un sistema de test no funcional, sino desarrollada, no pasa lo mismo en el caso de los estructural a imagen de los test en base a puntos circuitos analógicos. clave desarrollados para circuitos digitales. De esta manera, la verificación de una tara estructural del El Grupo de Tecnología Electrónica de la UIB ha circuito informa de la disfuncionalidad. La sustitución centrado precisamente su investigación en desarrollar de la verificación funcional por la estructural supondría sistemas de verificación para circuitos de telefonía un gran ahorro económico. móvil fabricados con tecnología CMOS VLSI que integren, junto con los componentes digitales también componentes analógicos, por ejemplo las primeras etapas de un receptor de radiofrecuencia. Los investigadores intentan adaptar técnicas de verificación ya suficientemente exploradas en circuitos digitales a esos circuitos analógicos integrados en CMOS. En síntesis, el grupo intenta permutar los actuales métodos de verificación de circuitos analógicos, básicamente funcionales, por métodos Hasta hoy, la verificación de circuitos analógicos de radiofrecuencia consiste en comprobar la recepción de la señal, la corrección del consumo, controlar el nivel de ruido, etc. Se trata en definitiva de un muestreo de variables continuas, muy lento y laborioso, porque en realidad debe hacerse funcionar cada circuito estructurales Hasta hoy, la verificación de circuitos analógicos de radiofrecuencia consiste en comprobar la recepción de la señal, la corrección del consumo, controlar el nivel El grupo también trabaja en el diseño de sensores de ruido, etc. Se trata en definitiva de un muestreo de integrados en el mismo chip para medir las variables variables continuas, muy lento y laborioso, porque en de test en los puntos clave (internos). Al final aquello realidad debe hacerse funcionar cada circuito. que se quiere conseguir es un circuito que se capaz de verificarse a si mismo. El grupo de Tecnología Electrónica de la UIB Dos integrantes del grupo de Tecnología Electrónica de la UIB en el laboratorio. Proyecto financiado Título: Desarrollo de nuevas estrategias de test para circuitos integrados CMOS RF. Referencia: TIC2003-01075. Entidad financiadora: Ministerio de Ciencia y Tecnología. Modalidad: Tecnologías de la información y las comunicaciones. Acrónimo: DET-CIRF. Periodo: 2003 - 2006. Investigador responsable Dr. Eugeni García Moreno, catedràtico de Universidad de Tecnología Electrónica. Grup de Tecnología Electrónica. Departamento de Física. Edificio Mateu Orfila i Rotger Tel. 971 17 32 31 E-mail: [email protected] Otros miembros del equipo Dr. Sebastià A. Bota Ferragut, profesor titular de Universidad de TE Dr. Eugeni Miquel Isern Riutort, profesor titular de Universidad de TE Dr. Miquel Roca Adrover, profesor titular de Universidad de TE Dr. Jaume segura Fuster, profesor titular de Universdad de TE Dr. Josep Lluís Rosselló Sanz, profesor titular de Escuela Universitaria de TE Sr. Joan Font Rosselló, profesor titular de Escuela Universitaria de TE Sr. Óscar Alberto Calvo Ibáñez, profesor titular de Escuela Universitaria de TE Sr. Rodrigo P. Picos Gayà, profesor colaborador Sra. Dèbora Coll Mayor, profesora colaboradora Instituciones y entidades colaboradoras Etienne Sicard, INSA Toulouse Sonia Delmas-Bendhia, INSA Toulouse José Antonio Sainz Gómez, Universidad del País Vasco Luís Ángel Aguado Rodríguez, Universidad del País Vasco José Miguel Gil-García Leiva, Universidad del País Vasco Fernando Oterino Echávarri, Universidad del País Vasco Jesús M. Sánchez Etchegaray, Universidad del País Vasco Webs de interés http://www.uib.es/depart/dfs/GTE/index.html# Página del Grupo de Tecnología Electrónica Publicaciones (2002-2003) Font, J.; Ginard, J.; Picos, R.; Roca, M.; Isern, E.; Segura, J. y García, E. 'A BICS for CMOS OpAmps by Monitoring the Supply Current Peak'. Journal of Electronic Testing-Theory and Applications. Vol. 19, pp 597-603, 2003 Font, J.; Picos, R.; Isern, E.; Roca, M. y García, E. 'A New BICS for CMOS Operational Amplifier by using Oscillation Test Techniques'. Microelectronics Journal. Vol. 34. núm.10, pp. 919-926, 2003 Moll, F.; Roca, M.; Isern, E. 'Analysis of dissipation energy of switching digital CMOS gates with coupled outputs'. Microelectronics Journal. Vol.34. pp. 833- 842, 2003 Font, J.; Ginard, J.; Isern, E.; Roca, M.; Segura, J.; Garcia, E. 'Oscillation-test technique for CMOS operational amplifiers by monitoring supply current'. Analog Integrated Circuits and Signal Processing, Vol.33, pp.213-224. 2002 Comunicaciones a congresos (2002-2003) Picos, R.; Isern, E.; Bota, S.A.; Roca, M. y Garcia, E. 'A Built-in current sensor with configurable capability'. XVIII Conference on Design of circuits and Integrated Systems Electronics (DCIS'03). 2003 Picos, R.; Font, J.; Isern, E.; Roca, M. y García, E. Títol: 'A configurable Built-in Current Sensor for Mixed-Signal Circuit Testing'. IEEE IOLTS. 2003 Font, J.; Ginard, J.; Isern, E.; Roca, M.; Segura, J.; Garcia, E. 'Voltage and current testing of CMOS operational amplifiers by using the oscillation- test technique'. IEEE International Mixed-Signal Test Workshop, pàg. 31-37, Montreux (Suïssa), Juny 2002. Font, J.; Ginard, J.; Isern, E.; Roca, M.; Segura, J.; Garcia, E. 'A BICS for CMOS Opamps by Monitoring the Supply Current Peak'. IEEE International On-Line Testing Workshop, pàg. 94-98, Ille de Bendor (França), Juliol 2002.