- Ninguna Categoria

00 Registros del PIC16F84A

Anuncio

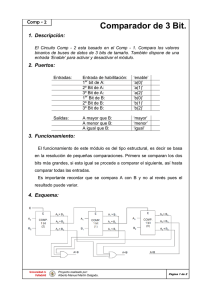

Registros del PIC16F84A Anteriormente ya localizamos la sección de registros especiales en el bloque de memoria RAM, estos estaban repartidos en dos bancos, el 0 y el 1, y situados en las 12 primeras posiciones o registros de cada uno (00h-0Bh, y 80h-8Bh). A continuación se presentan en bloque y en una tabla: Banco 0 Direcc Nombre Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 00h INDF Dirección de FSR (no es físicamente un registro) 01h TMR0 Contador/Temporizador de 8 bits 02h PCL 8 bits LSB del PC 03h STATUS IRP 04h FSR Puntero para el Direccionamiento Indirecto 05h PORTA - - - RA4 RA3 T0CKI 06h PORTB RB7 RB6 RB5 RB4 07h - No implementado 08h EEDATA Registro de Datos EEPROM 09h EEADR Registro de Direcciones EEPROM 0Ah PCLATH - - - 5 bits MSB del PC 0Bh INTCON GIE EEIE T0IE INTE RP1 RP0 TO PD RB3 RBIE Z DC C RA2 RA1 RA0 RB2 RB1 RB0 INT INTF RBIF T0IF Banco 1 Direcc Nombre Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 80h INDF Dirección de FSR (no es físicamente un registro) 81h OPTION RBPU INTE T0CS T0SE PSA PS2 PS1 PS0 82h PCL 8 bits LSB del PC 83h STATUS IRP 84h FSR Puntero para el Direccionamiento Indirecto 85h TRISA - 86h TRISB Dirección de los datos del Puerto B 87h - No Implementado 88h ECON1 - 89h ECON2 2º REGISTRO DE Control de la EEPROM 8Ah PCLATH - - - 5 bits MSB del PC 8Bh INTCON GIE EEIE T0IE INTE RP1 - - RP0 - - TO PD Z DC C Dirección de datos del Puerto A EEIF WRR RBIE WEN T0IF WR RD INTF RBIF Registro W En la figura siguiente se representa un diagrama simplificado de la arquitectura interna de los datos en la CPU de los microcontroladores PIC y de los microprocesadores tradicionales relacionado con la ALU: Podemos ver los buses por donde circulan los datos, y la Unidad Aritmético-Lógica ó ALU (Arithmetic-Logic Unit). Que es la encargada de hacer las operaciones aritméticas tales como suma y resta, y operaciones lógicas. Observamos que la principal diferencia entre ambos se encuentra en la ubicación del registro de trabajo, que para los PIC’s se denomina W (Working Register), y para los sistemas tradicionales es el Acumulador. En los microcontroladores tradicionales todas las operaciones se realizan sobre el acumulador. La salida del acumulador esta conectada a una de las entradas de la ALU, y por lo tanto éste es siempre uno de los dos operandos de cualquier instrucción. Por convención, las instrucciones de simple operando (borrar, incrementar, decrementar, complementar), actúan sobre el acumulador. La salida de la ALU va solamente a la entrada del acumulador, por lo tanto el resultado de cualquier operación siempre quedara en el acumulador. Para operar sobre un dato de memoria, después de realizar la operación tendremos que mover siempre el acumulador a la memoria con una instrucción adicional. En los microcontroladores PIC, la salida de la ALU va al registro W y también a la memoria de datos, por lo tanto el resultado puede guardarse en cualquiera de los dos destinos. En las instrucciones de doble operando, uno de los dos datos siempre debe estar en el registro W, como ocurría en el modelo tradicional con el acumulador. En las instrucciones de simple operando el dato en este caso se toma de la memoria (también por convención). La gran ventaja de esta arquitectura es que permite un gran ahorro de instrucciones ya que el resultado de cualquier instrucción que opere con la memoria (sea de simple o doble operando), puede dejarse en la misma posición de memoria o en el registro W, según se seleccione con un bit de la misma instrucción. Las operaciones con constantes provenientes de la memoria de programa (literales) se realizan sólo sobre el registro W. En la memoria de datos de los PIC’s se encuentran ubicados casi todos los registros de control del microcontrolador y sus periféricos autocontenidos, y también las posiciones de memoria de usos generales.Sin embargo el registro W no está implementado dentro de los registros especiales del bloque de memoria, si no que está situado a la entrada de la ALU como ya hemos visto anteriormente. En resumen, el registro W servirá para guardar temporalmente un dato leído de memoria, y lo usaremos como si del portapapeles del escritorio se tratase. Cuando copiamos algo (texto, un fichero o lo que sea), el contenido se guarda en el portapapeles, y cuando lo pegamos en su destino, este se copia y el contenido todavía permanece en el portapapeles hasta que cortemos o copiemos otro objeto. La pila o stack En los microcontroladores PIC el stack es una memoria interna dedicada, de tamaño limitado, separada de las memorias de datos y de programa, inaccesible al programador, y organizada en forma de pila, que es utilizada solamente, y en forma automática, para guardar las direcciones de retorno de subrutinas e interrupciones. Cada posición es de 11 bits y permite guardar una copia completa del PC. Como en toda memoria tipo pila, a los datos se accede de forma LIFO (Last In First Out) de manera que el último en entrar es el primero en salir. El tamaño del stack en los 16F84 es de 8 posiciones. El stack y el puntero interno que lo direcciona, son invisibles para el programador, solo se accede a ellos automáticamente para guardar o rescatar las direcciones de programa cuando se ejecutan las instrucciones de llamada o retorno de subrutinas, cuando se produce una interrupción o cuando se ejecuta una instrucción de retorno de ella. Registro INDF (00h y 80h) El registro INDF (Indirect File) que ocupa la posición 00 no tiene existencia física, por lo que no se podrá acceder a él. En realidad este registro sirve únicamente para especificar la utilización del direccionamiento indirecto junto con el registro FSR. Ver el direccionamiento indirecto en "El PIC16F84A". Registro TMR0 (01h) El registro TMR0 (Timer 0) almacena el valor del contador TMR0, que como ya sabemos, está funcionando continuamente e incrementando el valor que tiene almacenado. Las opciones que controlan este contador residen en el registro OPTION. El registro TMR0 se incrementa en una unidad con cada impulso de reloj seleccionado mediante el registro OPTION. Cada vez que llega al valor FF, vuelve a 00 generando una interrupción, si se ha autorizado, y continúa su ciclo indefinidamente. El registro TMR0 se puede leer o escribir directamente con cualquier instrucción, con el fin de conocer su posición actual, o para inicializarlo en un estado determinado. Es importante saber que después de cualquier escritura en este registro, es necesario un retardo de dos ciclos de instrucción para que se retome la incrementación. Este retraso es independiente de la fuente de reloj usada. Las instrucciones concernidas son MOVF TMR0 o CLRF TMR0. Para comprobar el paso por cero sin inferir en el desarrollo regular del recuento, es aconsejable utilizar, por ejemplo, una instrucción MOVF TMR0,W, que no hace mas que una lectura. El reloj interno deja de funcionar en el modo SLEEP, por lo que no se puede contar con sus interrupciones en este modo ni por consiguiente, que salga de este modo de funcionamiento por medio de dicha interrupción. Obsérvese que todas las instrucciones que escriben en el TMR0 ponen a cero al prescaler (divisor), cuando éste está asignado al temporizador. El Contador de programa PC (02h y 82h) Este registro, normalmente denominado PC (Program Counter), es equivalente al de todos los microprocesadores y contiene la dirección de la próxima instrucción a ejecutar. Se incrementa automáticamente al ejecutar cada instrucción, de manera que la secuencia natural de ejecución del programa es lineal, una instrucción después de la otra. Algunas instrucciones (que llamaremos de control) cambian el contenido del PC alterando la secuencia lineal de ejecución. Dentro de estas instrucciones se encuentran GOTO y CALL que permiten cargar en forma directa un valor constante en el PC haciendo que el programa salte a cualquier posición de la memoria. Otras instrucciones de control son los SKIP o saltos condicionales, que producen un incremento adicional del PC si se cumple una condición específica, haciendo que el programa salte, sin ejecutar, la instrucción siguiente. El PC del 16F84 es un registro de 13 bits, lo que permite direccionar 8.192 posiciones de memoria de programa, pero que internamente solamente podrá direccionar las 1.024 posiciones de memoria de programa del 16F84. Esto significa que solo hace realmente falta tener en cuenta 10 bits del PC (2 10=1.024). El PC está implementado por dos registros, PCLATH (5 bits) y PCL (8 bits) Los 8 bits de menor peso del PC los proporciona el registro PCL (02h) y a diferencia de la mayoría de los microprocesadores convencionales, es también un registro accesible al programador como registro de memoria interna de datos. Es decir que cualquier instrucción común que opere sobre registros puede ser utilizada para alterar el PCL y desviar la ejecución del programa. Los 5 bits de mayor peso del PC que no pueden leerse ni escribirse directamente proceden del registro PCLATH en la dirección 0Ah vy 8Ah. En la instrucción de salto relativo, el resultado de las mismas sólo afecta a los 8 bits de menor peso. Los 5 bits de mayor peso se suministran desde PCLATH. En las instrucciones GOTO y CALL se efectua la misma operación teniendo presente que el PC se codifica mediante 11 bits y se suministran en la propia instrucción, desde el código OP. Los dos bits de más peso del PC de cargan con los bits 4 y 3 del registro PCLATH. Dado que la memoria de programa se organiza en páginas de 2 K, la posición de la memoria la indican los 11 bits de menor peso del PC y los 2 bits de mayor peso indican la página. A continuación se muestra como se carga el PC: El reset pone a 0 todos los bits de PCL y PCLATH haciendo que el reinicio comience en la dirección 0000h. El contador de programa y la pila Los ocho registros de pila no estan situados en el mismo espacio de memoria que los demás. Son registros de trece bits capaces de contener íntegramente al PC. Su utilización es automática, ya que el PC se introduce en la pila durante la ejecución de una instrucción CALL o de una interrupción, y se extrae de la pila durante la ejecución del retorno correspondiente. Cuando los datos contenidos en el PC son almacenados o extraídos de la pila el registro PCLATH no se ve modificado. Estos registros de pila deben considerarse como un buffer de memoria circular, lo que significa que, si se introduce más de 8 valores del PC, el noveno valor tomará la posición del primero, y así sucesivamente. Ningún bit de registro indica que la pila está llena, por lo que debemos tener cuidado de que no se desborde. Registro de Estado (03h y 83h) El registro de Estado (STATUS) contienen varios bits de estado de la unidad central, el estado aritmético de la ALU, el estado del reset y un par de bits de selección de página denominados RP1 y RP0. Ocupa la posición 03h del banco 0 y la 83h del banco 1. Algunos de estos bits los podemos cambiar manualmente a través del programa. Otros no los activamos nosotros, si no que los activa automáticamente el PIC cuando se dan ciertos procesos. Estos bits se llaman flags (banderas). Para hacernos una idea práctica una bandera se levanta (se pone a 1) cuando ha pasado algo, al igual que ocurre en el fútbol con los linieres. El registro STATUS está formado por 8 bits: R/W-0 R/W-0 R/W-0 R-1 R-1 R/W-x R/W-x R/W-x IRP RP1 RP0 /TO /PD Z DC C bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 R/W significa que el bit correspondiente se puede leer y escribir, mientras que R significa que solamente puede ser leído. También se indica el estado que se establece tras un reset. Bit 7, IRP: Selección del banco en direccionamiento indirecto. Este bit junto con el de más peso del registro FSR sirven para determinar el banco de la memoria de datos seleccionado. En el PIC16X84 al disponer de dos bancos no se usa y debe programarse como 0. Bit 6 y 5, RP0 y RP1: Register Bank Select. Selección de página o banco de la memoria con direccionamiento directo. Cada página contiene 128 bytes. Como el PIC16X84 sólo tiene dos bancos únicamente se emplea RP0 de forma que cuando vale 0 se accede al banco 0 y cuando vale 1 se accede al banco 1. Después de un reset, RP0 se pone automáticamente a 0. RP1 debe mantenerse a 0. El bit RP1 deberá ser puesto a cero, ya que si no nos saldríamos del rango de memoria. Bit 4 (flag), TO: Time Out (Tiempo acabado) o 1. Se pone a 1 tras conectar la alimentación o al ejecutar CLRWDT o SLEEP. o 0. Se pone a 0 por desbordamiento del Perro Guardián WDT. Bit 3 (flag), PD: Power Down (Apagado). o 1. Se pone automáticamente a 1 tras conectar la alimentación Vdd o ejecutar CLRWDT, que resetea el contador WatchDog. o 0. Se pone a 0 al ejecutar la instrucción SLEEP. Bit 2 (flag), Z: Cero o 1 = El resultado de una operación aritmética o lógica es 0. o 0 = El resultado es distinto de 0. Bit 1 (flag), DC (Digit Carry). Acarreo en el 4º bit de menos peso. Funciona igual que el bit de Carry descrito a continuación. De interés en operaciones en BCD Bit 0 (flag), C (Carry). Acarreo en el 8º bit o bit de mas peso. Es el bit de "acarreo" en operaciones de suma AADWF y ADDLW así como también el bit de "llevada" en las instrucciones de sustracción SUBWF y SUBLW. También lo emplean las instrucciones RLF y RRF de rotación de bits. o Suma 1. Se pone a 1 cuando se ha producido acarreo en la suma en el bit de mayor peso con las operaciones AADWF y ADDLW. 0. Se pone a 0 si en la suma no se ha producido acarreo. o Resta 1. Se pone a 1 si en la resta no se ha producido llevada. 0. Se pone a 0 cuando se ha producido llevada en la resta con las operaciones SUBWF y SUBLW. Posibles configuraciones de los bits de selección de página RP1 y RP0: RP1 RP0 Banco Dirección 0 0 0 00h a 7Fh 0 1 1 80h a FFh 1 0 2 100h a 17Fh 1 1 3 180h a 1FFh Registro FSR (04h y 84h) El contenido del FSR se utiliza para el direccionamiento indirecto junto con el registro INDF. Este registro contiene 8 bits. Ver el direccionamiento indirecto en "El PIC16F84A". Registro PORTA y PORTB (05h y 06h) Cuando vimos los puertos se comentó el uso de estos registros que contienen los niveles lógicos de las patillas de E/S. Cada bit se puede leer o escribir según la patilla correspondiente se haya configurado como entrada o como salida. Conviene recordar que cualquier línea puede funcionar como entrada o como salida. Sin embargo, si actúa como entrada la información que se introduce no se memoriza, por lo que la información debe ser mantenida hasta que sea leída. Si la línea actúa como salida, el bit que procede del bus de datos se guarda en la báscula, con lo que la información que ofrece esta patilla permanece invariable hasta que se reescriba este bit. bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 RB7 RB6 RB5 RB4 RB3 RB2 RB1 RB0 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 RA4 RA3 RA2 RA1 RA0 Registro EEDATA (08h) El registro EEDATA (Datos de EEPROM) guarda el contenido de una posición de la memoria EEPROM de datos antes de su escritura o después de su lectura, según leamos o escribamos en ella. Para leerla se sigue un proceso especial que se comentará mas adelante. Como ya sabemos la memoria EEPROM es bastante lenta, dato que tendremos en cuenta cuando accedamos a ella para escribirla, pues tarda unos 10 ms en completar el proceso. Registro EEADR (09h) El registro EEADR (Dirección de EEPROM) guarda la dirección de la posición de memoria EEPROM cuando queramos acceder a ella, bien para su lectura, o bien para su escritura. El igual que con el registro anterior, veremos su uso más a fondo cuando lleguemos a las instrucciones que lo utilizan. El registro EEADR puede direcconar como máximo 256 bytes de los cuales sólo los 64 primeros están disponibles, con lo que los dos bits de mayor peso han de tener el valor de '0'. Registro PCLATH (0Ah y 8Ah) El registro PCLATH (Contador de Programa Alto) ya lo vimos cuando analizamos el PCL y su relación con el PC. Registro INTCON (0Bh y 8Bh) Este registro contiene varios bits de selección de fuentes de interrupción, el bit de activación global de interrupciones y varios flag que indican la causa de una interrupción. Sirve para el control global de las interrupciones y para indicar la procedencia de algunas de ellas, gracias a los bits de estado. Se dispone de cuatro potenciales recursos de interrupción: Una fuente externa a través del pin RB0/INT. El desbordamiento del temporizador 0 (TMR0). Un cambio de estado en los pines RB4 a RB7. Programación de la EEPROM de datos. Cada bit del registro INTCON tiene un significado concreto que se muestra en la siguiente tabla: R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-x GIE EEIE T0IE INTE RBIE T0IF INTF RBIF bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0 Bit 7, o o Bit 6, o GIE: Habilitación global de interrupciones (Global Interrupt Enable). 1: Concede el permiso de interrupciones. 0: Cancela el permiso de las interrupciones. EEIE: Habilitación de las Interrupciones de la memoria EEPROM. 1: Permite que se produzcan interrupciones debidas al fin de escritura de la EEPROM, etc. o 0: Este tipo de interrupciones estarán inhibidas. Bit 5, T0IE: Habilitación de la interrupción del temporizador por desbordamiento (Timer 0 Interrupt Enable). o 1: Autoriza las interrupciones debidas al desbordamiento del temporizador. o 0: Interrupción del temporizador deshabilita de manera que cuando se produzca el flag correspondiente permanecerá inactivo. Bit 4, INTE: Habilitación de la entrada de interrupción externa (Interrupt Enable) por patilla RB0/INT. o 1: Autoriza las interrupciones provocadas RB0/INT del puerto B. o 0: Interrupción externa deshabilita de manera que cuando se produzca una interrupción externa el flag correspondiente permanecerá inactivo. Bit 3, RBIE: Habilitación de las interrupciones del puerto B (RB Interrupt Enable). o 1: Autoriza las interrupciones provocadas por un cambio de estado de las líneas RB4 a RB7 del puerto B. o 0: Interrupción del puerto B deshabilitada. Bit 2 (flag), T0IF: Bit de interrupción de desbordamiento del TMR0. o 1: El TMR0 ha rebosado. Se borra por software. o 0: El TMR0 no ha rebosado. Bit 1 (flag), INTF: Bit de interrupción de la Entrada de Interrupción INT (patilla RB0/INT). o o Bit 0 o o 1: La entrada de interrupción se ha activado (patilla RBO/INT del puerto B). Se borra por software. 0: No hay interrupción externa. (flag), RBIF: Bit de interrupción del puerto B. 1: Cambio de estado en una de las líneas de RB4 a RB7 del puerto B. Se borra por software. 0: Ninguna línea de RB4 a RB7 del puerto B ha cambiado. Cada flag o bandera individual debe ponerse a cero por software. Solamente hay un vector de interrupción en la memoria de programa (dirección 0004h), por lo que se deben comprobar los bits de INTCON en la subrutina de interrupción para saber cual es la fuente de la misma. Cuando llega una interrupción, el PIC pone el bit GIE a cero, de forma que no se perturbe el tratamiento de la interrupción en curso, debido a otras interrupciones eventuales. Este bit se pone automáticamente a uno al terminar la subrutina de interrupción, con la ejecución de la instrucción RETFIE. Los indicadores de interrupciones correspondientes permanecen funcionales incluso cuando no se han autorizado. En este caso también pueden leerse y escribirse todos los bits que componen este registro. Registro OPTION (80h) El registro OPTION (o registro de opciones) se emplea para programar las opciones del temporizador TMR0, el tipo de flanco con el que se detecta una interrupción y la activación de las resistencias de polarización del puerto B. Ocupa la posición 81h de la página 1 del banco de registros. Debe escribirse usando la instrucción especial OPTION. Esta instrucción carga el contenido de W en el registro OPTION. R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 /RBPU INTEDG T0CS T0SE PSA PS2 PS1 PS0 Bit 7 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Bit 6 Bit 5 Bit 7, /RBPU (RB Pull Up). Conexión de las resistencias de polarización del Puerto B. Se conectan todas cuando el puerto B actua como entrada. o 1: Todas las resistencias son desconectadas. o 0: Las resistencias se activan de forma individual. Bit 6, INTDEG (INTerrupt EDGe). Selecciona el tipo de flanco para la interrupción externa. Este bit indica el tipo de flanco de la señal externa que ha de provocar una interrupción en la patilla RB0/INT. o 1: La interrupción es producida por el flanco ascendente o de subida. o 0: La interrupción es producida por el flanco descendente o de bajada. Bit 5, T0CS (Timer 0 Signal Source). Selección de la fuente de reloj para el TMR0. o 1: TMR0 se usa en modo contador de los pulsos introducidos a través de RA4/T0CKI o 0: TMR0 se usa en modo temporizador haciendo uso de los pulsos de reloj internos (Fosc/4). Bit 4, T0SE (Timer 0 Signal Edge). Tipo de flanco activo de T0CKI (patilla RA4/T0CKI). o 1 = El TMR0 se incrementa con el flanco descendente de la señal aplicada a RA4/T0CK1. o 0 = El TMR0 se incrementa con el flanco ascendente. Bit 3, PSA (PreScaler Assignement). Se usa para la asignación del divisor de frecuencias o Prescaler. o 1 = El divisor de frecuencia se asigna al WDT. o 0 = El divisor de frecuencia se asigna a TMR0. Bits 0, 1 y 2, PS0, PS1 y PS2 (Prescaler Rate Select Bits). Configura la tasa del valor del divisor de frecuencia o prescaler. Difiere dependiendo que se haya asignado al TMR0 o al WDT. PS2 PS1 PS0 Divisor TMR0 Divisor WDT 0 0 0 1:2 1:1 0 0 1 1:4 1:2 0 1 0 1:8 1:4 0 1 1 1:16 1:8 1 0 0 1:32 1:16 1 0 1 1:64 1:32 1 1 0 1:128 1:64 1 1 1 1:256 1:128 Registro TRISA y TRISB (85h y 86h) Los registros TRISA y TRISB los vimos cuando estudiamos los puertos (ver "Puertos de E/S" de "El PIC16F84A"), pero conviene recordar lo siguiente: Estos registros son idénticos para el puerto A y el puerto B, con la diferencia de que uno será de 5 bits y otro de 8 bits, el mismo número de bits que tiene cada puerto. Los registros TRIS, también son llamados así, sirven para configurar si los bits de cada puerto serán de entrada o de salida: o 1: La patilla del puerto correspondiente será de entrada o 0: En este caso la patilla actuará como una salida. Para mas información, ver "Instrucciones y puertos" de "Técnicas de programación". Registro EECON1 (88h) Este registro contiene configuraciones importantes acerca de la escritura y la lectura de la EEPROM de datos. En concreto tiene 5 bits de control, cuya distribución y significado es el siguiente. U-0 U-0 - - U-0 - R/W-0 R/W-x EEIF Bit 7 Bit 6 Bit 5 Bit 4 R/W-0 R/S-0 R/S-0 WRERR WREN WR RD Bit 3 Bit 0 Bit 2 Bit 1 U (Unimplemented), No implementado. Se lee como 0. Bit 4 (flag): EEIF. Bit de interrupción de escritura en la memoria EEPROM ( EEPROM Interrupt Flag) o 1: Este bit se pone a uno al terminar la operación de escritura en la EEPROM, y debe ponerse a cero por software o 0: No se ha completado la operación de escritura o no ha empezado. Bit 3 (flag), WRERR. Bit de error de escritura (Write Error) o 1: Este bit se pone a 1 si se produce un error de escritura de forma prematura (Reset o Watchdog). En este caso, los contenidos de EEADR y EEDATA no varían, de manera que el proceso pueda ser repetido correctamente. o 0: Se ha completado la operación de escritura. Bit 2, WREN. Bit de habilitación de escritura. (Write Enable) o 1: Este bit debe ser habilitado para poder escribir en la EEPROM o 0: Deshabilita la escritura de datos en la memoria EEPROM. Bit 1, WR. Bit de control de escritura (Write Data) o 1: Indica que se ha iniciado una operación de escritura. Este bit debe ponerse a uno para escribir un dato. o 0: Indica que se ha completado una operación de escritura. El PIC lo pone automáticamente a cero Bit 0, RD. Bit de control de lectura (Read Data) o o 1: Inicia una lectura de la memoria EEPROM. Este bit debe ponerse a uno para poder leer un dato. 0: No se ha iniciado una lectura de la EEPROM. El PIC lo pone automáticamente a cero En el registro EECON1, los tres primeros bits no están implementados por los que su lectura es '0'. Los bits de control RD y WR inician operaciones de lectura y escritura respectivamente. Estos bits sólo pueden ser puestos a '1' por software, nunca a '0'. Son puestos a '0' cuando se completa la operación de lectura o escritura. Para leer una posición de memoria, se debe escribir la dirección en el registro EEADR y colocar a '1' el bit de control RD. El dato estará disponible en un próximo ciclo de instrucción, normalmente en el siguiente, en el registro EEDATA hasta que se lea otro o se escriba en este registro. Para escribir un dato en la EEPROM, se debe primero colocar la dirección en el registro EEADR y el dato en el registro EEDATA. Luego. Después se debe seguir una secuencia específica para comenzar a escribir cada byte, para garantizar no escribir datos en la EEPROM por error. La secuencia es: MOVLW 55h MOVWF EECON2 MOVLW AAH MOVWF EECON2 BSF EECON1,WR ; Escribe 55h en EECON2 ; Escribe AAh en EECON2 ; Pone WR a 1 para comenzar la escritura Además, el bit WREN del registro EECON1 debe estar puesto a '1' para habilitar la operación de escritura. Más información en Uso de la EEPROM. Registro EECON2 (89h) Este registro no está implementado físicamente, por lo cual no se puede leer. Tan sólo sirve para un proceso de protección de escritura que consiste en copiar en él unos datos específicos, con el fin de evitar que un programa por error pueda programar la EEPROM, manipulando simplemente los bits del EECON1. Lo veremos mas adelante en Uso de la EEPROM. Estado predeterminado de los registros En la siguiente tabla, se muestran los estados que tienen los registros al alimentar el PIC, después de un reset y al salir del modo SLEEP. Leyenda: ( ( ( ( u ) = no cambia x ) = desconocido - ) = no existe, se lee como 0 ? ) = depende de otras condiciones Notas: 1. Uno o más bits de INTCON pueden quedar afectados a causa de la salida del modo SLEEP. 2. Cuando la salida del modo SLEEP se produce por una interrupción y GIE está activado, el PC se carga con el vector de interrupción (0004 h). Las posibles fuentes de reset afectan de forma diversa a los contenidos de los diferentes registros de control, de estado o de datos. En la descripción de cada registro se indica el estado de los bits después de un reset de alimentación. Es aconsejable examinar esta tabla después de un reset antes de cualquier utilización, excepto en el caso de que se reinicie por programa cada registro. en modo normal en modo SLEEP Reset por WDT en modo normal Reset por MLCR Reg Direc. Conexión de la alimentac. Salida del modo SLEEP por WDT por interrupci ón PC - 000 h 000 h 000 h 000 h PC + 1 PC + 1 W - xxxx xxxx uuuu uu uu uuuu uu uu uuuu uu uu uuuu uuu u uuuu uuuu IND F 00 h ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- TMR 0 01 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu PCL 02 h 0000 0000 0000 0000 0000 0000 0000 0000 PC+1 PC+12 STA TUS 03 h 0001 1xxx 000u uuuu 0001 0uuu 0000 1uuu uuu0 0uuu uuu1 0uuu FSR 04 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu POR TA 05 h ---x xxxx ---u uuuu ---u uuuu ---u uuuu ---u uuuu ---u uuuu POR TB 06 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu EED ATA 08 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu EEA DR 09 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu PCL ATC H 0A h ---0 0000 ---0 0000 ---0 0000 ---0 0000 ---u uuuu ---u uuuu INT CON 0B h 0000 000x 0000 000u 0000 000u 0000 000u uuuu uuuu1 uuuu uuuu1 IND F 80 h ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- OPT ION 81 h 1111 1111 1111 1111 1111 1111 1111 1111 uuuu uuuu uuuu uuuu PCL 82 h 0000 0000 0000 00 00 0000 00 00 0000 00 00 PC+1 PC+12 STA TUS 83 h 0001 1xxx 000u uuuu 0001 0uuu 0000 1uuu uuu0 0uuu uuu1 0uuu FSR 84 h xxxx xxxx uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu uuuu TRI SA 85 h ---1 1111 ---1 1111 ---1 1111 ---1 1111 ---u uuuu ---u uuuu TRI SB 86 h 1111 1111 1111 1111 1111 1111 1111 1111 uuuu uuuu uuuu uuuu EEC ON1 88 h ---0 x000 ---0 ?000 ---0 ?000 ---0 ?000 ---u uuuu ---u uuuu EEC ON2 89 h ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- ---- PCL ATC H 8A h ---0 0000 ---0 0000 ---0 0000 ---0 0000 ---u uuuu ---u uuuu INT CON 8B h 0000 000x 0000 000u 0000 000u 0000 000u uuuu uuuu1 uuuu uuuu1

Anuncio

Documentos relacionados

Descargar

Anuncio

Añadir este documento a la recogida (s)

Puede agregar este documento a su colección de estudio (s)

Iniciar sesión Disponible sólo para usuarios autorizadosAñadir a este documento guardado

Puede agregar este documento a su lista guardada

Iniciar sesión Disponible sólo para usuarios autorizados