Unidad 3 parte 3

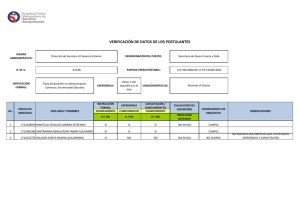

Anuncio

Hardware 8086 • Canal de direcciones de 20 bits y canal de datos de 16 bits de tiempo multiplexado. • Línea (ALE) para el demultiplexado, necesitando un par de "latches“ externos • El temporizado es el de un reloj de simple fase operando a 5 MHz (200nseg) u 8 MHz (125nseg) • Ciclo de bus consiste al menos de 4 períodos de reloj (T1, T2, T3 y T4). • Dos espacios de direccionamiento: uno de memoria de hasta 1 Mbyte y otro de I/O de hasta 64 Kbyte (o 32 Kword). • Opera en dos modos: mínimo y máximo. – Modo mínimo: la CPU opera como un único procesador. – Modo máximo: la CPU, con un controlador de bus 8288, se configuran para soportar aplicaciones de multiprocesamiento. Descripción de los pines • • AD15-AD0:(I/O). Estas líneas constituyen el canal de tiempo compartido de direcciones de memoria-I/O, durante T1 y el canal de datos durante T2, T3 y T4. • • A19/S6-A18/S5-A17/S4-A16/S3:(O). Estas líneas constituyen el canal de tiempo compartido de direcciones de memoria y líneas de estado. Durante T1, son las 4 líneas de direcciones de memoria más altas. Para operaciones de I/O están en 0. Durante T2, T3 y T4, son las líneas de información de estado, con las cuales se encodifica la información referida a la habilitación de interrupciones y cual registro segmento se está empleando para el acceso a memoria. • • /BHE/S7: (O). Durante T1, se comporta como señal "bus high enable", para habilitar la parte más significativa del canal de datos (byte correspondiente a direcciones impares). Durante T2, T3 y T4, es la línea de información de estado S7 cuya función es indefinida. Descripción de los pines • • • • • /RD: (O) Es la línea de control de un ciclo de lectura de memoria-I/O. Se activa durante los períodos de reloj T2 y T3 . READY:(I) Es el reconocimiento de parte de la memoria o dispositivo de I/O direccionado, indicando que se completó una transferencia de datos. • • INTR:(I) Interrupción enmascarable. • • NMI:(I) Interrupción no enmascarable. • • /TEST:(I) Esta entrada es examinada por la instrucción WAIT. Si la línea TEST está baja la ejecución del programa continúa, de otra manera el procesador espera en un ciclo ocioso. Descripción de los pines • • RESET:(I) Cuando se activa esta línea, la CPU inicializa al sistema con los siguientes valores: CS= FFFF, IP= 0000, Flags= 0, DS=ES=SS= 0000. • • CLK: (I) Reloj • • VCC: (I) Alimentación • • GND: Tierra. • • MN/MX:(I) Determina en que modo va a operar el procesador: mínimo o máximo. Descripción de los pines Modo mínimo: • • M/IO:(O) Distingue el acceso al mapa de memoria del acceso al mapa de I/O. • • /WR: (O) Es la línea de control de un ciclo de escritura de memoria-I/O. Se activa durante los períodos de reloj T2 y T3. • • /INTA:(O) Es la línea de control del ciclo de reconocimiento de la interrupción INTR. Se activa durante los períodos de reloj T2 y T3. • • ALE: (O) Esta línea la provee la CPU para "latchear" las direcciones en el latch de direcciones. Descripción de los pines Modo máximo: • • S0,S1,S2:(O) Esta líneas de estado son empleadas por el controlador de canal 8288, para generar todas las señales de control de acceso a memoria o I/O. • • RQ/GT0 - RQ/GT1:(I/O) Estas líneas le permite a la CPU que otro procesador utilice el bus local de la CPU, por medio de un protocolo enviado y transmitido por cada una de las líneas bidireccionales. Es equivalente a una función de DMA. Comúnmente empleado para la conexión del procesador de I/O 8089, al 8086/88. • • /LOCK:(O). En una configuración de multiprocesamiento, cuando está activo, sirve para indicarle a los restantes masters del sistema, que el canal compartido está ocupado. Esta línea se activa por la instrucción prefijo LOCK y permanece activa hasta que se complete la ejecución de la próxima instrucción. • • QS0,QS1:(O). Estas líneas permiten conocer el estado interno de la cola de instrucciones, para realizar un seguimiento "tracking" externo de la misma. Esto es útil para implementar un emulador de la CPU. Además permite que un coprocesador pueda procesar el conjunto extendido de instrucciones. Interface de memoria para el microprocesador 8086 1 Mbyte RAM Dinámica Decodificador de bancos separados Memoria Dirección EPROM F0000H FFFFFH RAM 00000H – 03FFFH Señal de control /WR separada por banco Decodificación de Espacio de I/O Decodifica 4 Entradas y 4 Salidas Decodificación de Espacio de I/O Operación del Canal • Un ciclo de canal en el 8086/88 consiste de un número mínimo de 4 períodos de reloj (T estados) T1, T2, T3 y T4 • Durante el período T1, la CPU coloca los bits de direcciones en el canal de direcciones, generando además el pulso de ALE. La línea BHE también se genera durante este período. Operación del Canal • Durante el período T2, se quitan las direcciones del canal y estas líneas o permanecen en tres-estados en espera de un dato, si corresponde a un ciclo de lectura, o la CPU coloca el dato a ser enviado a memoria o dispositivo de I/O, si corresponde a un ciclo de escritura. • Durante el período T3, o muestrea el dato a ser leído, si corresponde a un ciclo de lectura, o mantiene el dato a ser escrito, si corresponde a un ciclo de escritura. • Durante el período T4, termina el ciclo de canal. Operación del Canal • El 8086/88 tiene la capacidad de insertar estados Twait entre T3 y T4, para compensar el tiempo de acceso en aquellos dispositivos (memoria o I/O) que no pueden transferir datos a la máxima velocidad. Además se pueden generar tiempos ociosos, referenciados como TI, entre ciclos de canal. Ellos se pueden deber a accesos al canal otorgados a un coprocesador o a la ejecución de una instrucción larga. • Los temporizados descriptos corresponden al modo mínimo. Características de Multiprocesamiento • Facilidades para coordinar actividades entre dos o más procesadores que trabajan en paralelo. • La señal y prefijo LOCK, útiles para examinar los semáforos • La instrucción WAIT, que trabaja en conjunto con la señal de entrada TEST, para coordinar actividades con otro procesador. • La instrucción ESCAPE, para trabajar en paralelo con coprocesadores • REQUEST/GRANT (I/O), para la solicitud y entrega de los canales entre el microprocesador y otros maestros del sistema. Señal y Prefijo LOCK • En un sistema de multiprocesamiento, la línea LOCK sirve para coordinar el acceso de varios procesadores a un recurso común (memoria). • La señal de salida LOCK se utiliza (con el c. integrado árbitro de canal 8289) para garantizar el exclusivo acceso al canal del sistema compartido. • Esta señal la activa la BIU durante todo el período de ejecución de una instrucción precedida por el prefijo de instrucción LOCK. • La señal LOCK (mientras permanezca activa), bloquea a otro procesador que solicita el uso del canal, debiendo esperar hasta que lo liberen. El prefijo y señal LOCK, en conjunto con la instrucción XCHG [memory,registro], permite coordinar el uso de un espacio de memoria compartida, entre dos o más procesadores. Instrucción WAIT y Señal TEST • La instrucción WAIT en conjunto con la señal TEST permiten sincronizar la ejecución de subprogramas con eventos externos • Ejemplo: coordina actividades entre procesador y coprocesador. • La instrucción WAIT examina la línea TEST • Detiene la ejecución (permaneciendo en estado ocioso) mientras TEST está inactiva • Si TEST está en estado activa, continúa con la ejecución de la próxima instrucción Instrucción WAIT y Señal TEST • La instrucción WAIT en conjunto con la señal TEST permiten sincronizar la ejecución de subprogramas con eventos externos • Ejemplo: coordina actividades entre procesador y coprocesador. • La instrucción WAIT examina la línea TEST • Detiene la ejecución (permaneciendo en estado ocioso) mientras TEST está inactiva • Si TEST está en estado activa, continúa con la ejecución de la próxima instrucción Instrucción ESCAPE • La instrucción ESCAPE permite que coprocesador pueda obtener un código de operación y/o operando de memoria • Una instrucción y un operando (si fuese necesario) se "escape" de la corriente de instrucciones tomadas por el microprocesador, para que un procesador externo o un coprocesador lo utilicen. • Ejemplo: es común el uso de la instrucción ESC en conjunto con la instrucción WAIT y la señal TEST. Instrucción ESCAPE en conjunto con la instrucción WAIT y la señal TEST Acceso Directo a Memoria • El microprocesador 8086 soporta las transferencias de datos mediante Acceso Directo a Memoria (DMA) tanto en el modo mínimo como en el modo máximo Modo Mínimo (HOLD/HOLDA) Acceso Directo a Memoria Modo Máximo (Líneas Request/Grant) • Las líneas HOLD y HOLDA se transforman en un par líneas bidireccionales, independientes una de la otra (RQ/GT) • La secuencia Request/Grant consiste en un ciclo de tres fases: pedido, concesión y devolución. Coprocesador Coprocesador Tiempos de ejecución (en µseg) de diferentes funciones aritméticas, empleando el 8087 y por medio de un software implementado en el 8086.