Practica No 1 - Electrónica Digital II. Prof.Zulay Franco (Unexpo

Anuncio

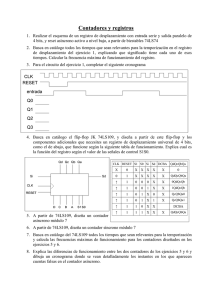

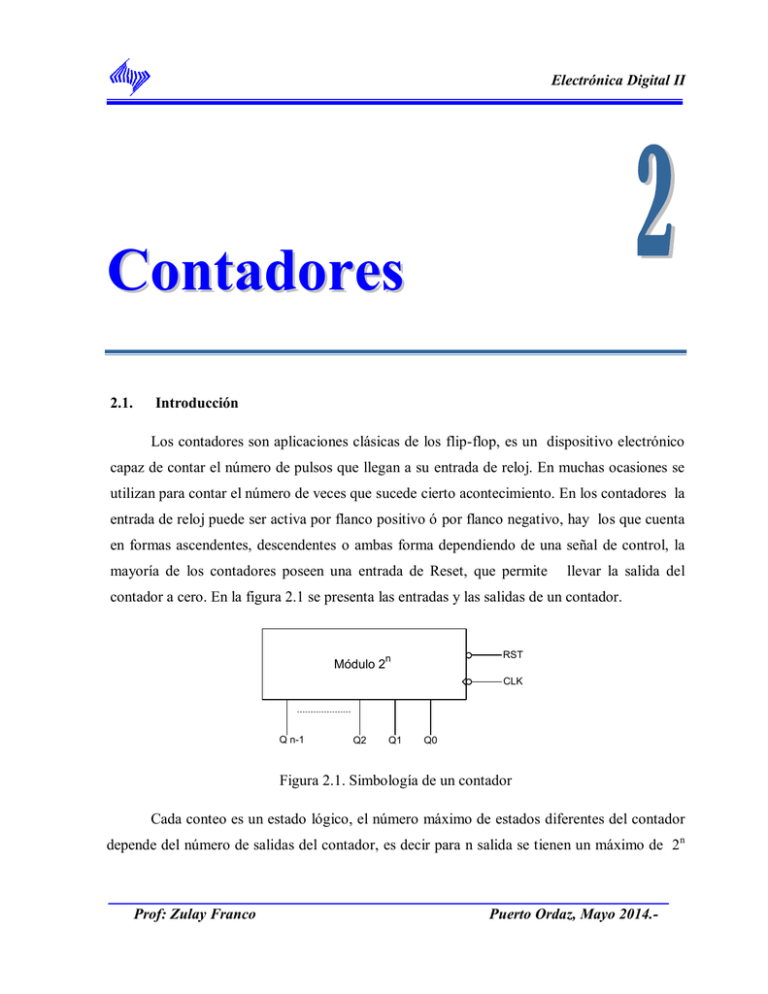

Electrónica Digital II Contadores 2.1. Introducción Los contadores son aplicaciones clásicas de los flip-flop, es un dispositivo electrónico capaz de contar el número de pulsos que llegan a su entrada de reloj. En muchas ocasiones se utilizan para contar el número de veces que sucede cierto acontecimiento. En los contadores la entrada de reloj puede ser activa por flanco positivo ó por flanco negativo, hay los que cuenta en formas ascendentes, descendentes o ambas forma dependiendo de una señal de control, la mayoría de los contadores poseen una entrada de Reset, que permite llevar la salida del contador a cero. En la figura 2.1 se presenta las entradas y las salidas de un contador. RST n Módulo 2 CLK Q n-1 Q2 Q1 Q0 Figura 2.1. Simbología de un contador Cada conteo es un estado lógico, el número máximo de estados diferentes del contador depende del número de salidas del contador, es decir para n salida se tienen un máximo de 2n Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II estados diferentes. El número de estados diferentes que se tienen a la salida del contador se le denomina Módulo. Estos dispositivos se pueden clasificar en: Asíncronos: conocidos también como contadores serie ó de propagación. Síncronos: conocidos también como contadores en paralelo. En los contadores síncronos todas sus salidas cambian de estado simultáneamente con la señal de reloj, mientras que en los asíncronos todas las salidas no están sincronizadas con la señal de reloj. 2.2. Contadores asíncronos Los contadores asíncronos son llamados contadores serie ó contadores de propagación debido a su implementación. Los contadores son circuitos electrónicos construidos a base de flip-flop, el número de flip-flop utilizados va a depender del módulo del contador. Para los contadores asíncronos la señal de reloj externa está conectada a la entrada de reloj del flip-flop menos significativo y la entrada de reloj de los demás flip-flop estará gobernada por la salida Q ó Q del flip-flop inmediatamente anterior. De esta forma, el efecto de un pulso de reloj, introducida en el primero, se propagará de un flip-flop a otro hasta que llegue al último de la secuencia. Por este motivo se le llama contadores de propagación o también contadores serie. 2.2.1. Contadores Ascendentes con módulo igual a 2n Son contadores con n salidas, en cada pulso de reloj realiza el conteo hacia arriba desde cero hasta su máxima cuenta de 2n – 1, al llegar a su máximo conteo su próximo estado es el cero, iniciando así de nuevo la secuencia. Para estos contadores el flip flop menos significativo conmuta en cada estado, el siguiente flip flop cada 2 estado el tercero cada 4 estado y así sucesivamente, es decir cada salida X, cambia cada 2X estado, X indica el valor posicional de la salida y va desde 0 hasta n-1. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Por ejemplo si se desea diseñar un contador módulo 4 se necesitan 2 salidas del contador para poder obtener los conteo binario “00”, “01”, “10” y “11”, por tanto se requieren dos flip-flop, uno para cada salida, y así si se desea diseñar un contador módulo 8 se necesitan 3 salidas del contador para poder obtener los 8 estados diferentes y por tanto se requieren tres flip-flop, uno para cada salida y así sucesivamente para contadores con módulo 16, 32, 64, etc. Para un contador módulo 8 se requieren 3 Flip Flop para realizar el conteo ascendente Simbología: Conteo: RST Módulo 8 CLK Q2 Q1 Q0 Q2 Q1 Q0 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 Figura 2.2. Simbología y tabla de la secuencia de conteo de un contador Ascendente De la tabla se puede realizar el análisis para implementar el contador: De lo anterior se deduce que se deben utilizar flip flop en modo de conmutación los cuales pueden ser el tipo J-K ó el tipo T y a través de su entrada de reloj CLK se controla el instante en que debe hacer la conmutación. Entonces observando la tabla tenemos: La salida Q0 conmuta en cada estado, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK conectar el reloj externo. La salida Q1 conmuta cada vez que la salida Q0 pasa de 1 a 0, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK Prof: Zulay Franco debe ir Puerto Ordaz, Mayo 2014.- Electrónica Digital II conectada la salida Q0 , si el flip-flop es disparado por flanco de bajada y Q0 si el flip.flop es disparado por flanco de subida La salida Q 2 conmuta cada vez que la salida Q1 pasa de 1 a 0, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK debe ir conectada la salida Q1 , si el flip-flop es disparado por flanco de bajada y Q1 si el flipflop es disparado por flanco de subida Si se desea llevar la salida del contador en cualquier momento a una cuenta igual a cero, se debe utilizar para la implementación flip-flop que dispongan de la entrada asíncrona Clear. Para que el contador cuente el pulso que llega por su entrada de reloj esta entrada asíncrona debe estar en su estado inactivo. Si la entrada asíncrona de Preset está disponible en los biestable esta debe colocarse en su nivel inactivo, no debe dejarse sin conectar. En la figura 2.3. se implementa un contador ascendente módulo 8 utilizando flip flop J-K con entradas de excitación activas en alto y entradas asíncronas Preset y Clear activas en bajos. Vcc Q P J K Vcc Q P Q C Clk J K Vcc Q P Q C Clk J K Q C Clk Vcc Entrada de reloj Entrada de reset Q2 Q1 Q0 Figura 2.3 Implementación de un contador asíncrono ascendente MOD=8 Este procedimiento debe seguirse para el diseño de cualquier contador asíncrono ascendente con módulo 2n. En la figura 2.4 se puede observar el diagrama de tiempo de cada salida del contador. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Diagrama de tiempo del contador módulo 8 CLK externa=CLK de Q0 Q0=CLK de Q1 Q1=CLK de Q2 Q2 Conteo 0 1 2 3 4 5 6 7 0 Figura 2.4 Diagrama de tiempo del contador módulo 8 Frecuencia de la señal de reloj Debido a la forma como se implementa este tipo de contador la frecuencia de la señal de reloj externa va depender del número de flip-flop y del tiempo de respuesta ó propagación t p de cada uno de ellos ya que para que el siguiente flip-flop realice un cambio en su salida tiene que esperar que el anterior se lo indique como se puede observar en la grafica del diagrama de tiempo de la figura 2.5 Es decir si en el ejemplo anterior se utilizan flip-flop que tienen un tiempo de respuesta de 25nseg, en el caso de que el conteo binario vaya de “011” al “100” donde todos los flip- flop tienen que conmutar, el tiempo total para ver a la salida el estado binario “100” es 75 nseg . Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II CLK Q0 25 nseg Q1 50 nseg Q2 Conteo 0 1 2 3 75 nseg 4 5 6 7 0 Estado transitorio “000” por el que pasa el contador para finalmente colocar el estado “010” a su salida Figura 2.5. Diagrama de tiempo del contador módulo 8 El inverso de este valor nos daría el periodo mínimo de la señal de reloj externa, es decir la frecuencia máxima de operación para el correcto funcionamiento del contador, pues si no se respeta esta condición y se coloca una frecuencia mayor, el primer flip-flop puede conmutar nuevamente y aun el último flip-flop no ha realizado el cambio correspondiente y se puede tener un estado no deseado a la salida del contador como es el conteo “001”. Es importante que si se desea trabajar con contadores asíncrono se tenga en cuenta que entre un conteo a otro, por ser estos contadores de propagación, a la salida del contador se tiene estados transitorios hasta que finalmente se estabiliza, si se va conectar a la salida de este contador otro dispositivo se debe tener en cuenta este tiempo de respuesta del contador para que dicho dispositivo no realice una lectura herrada. Se puede observar en la figura 2.5. que cuando el contador va del conteo ”001” al conteo “010” en la salida del contador se tiene un estado transitorio “000” , debido a que cuando la salida Q0 conmuta el siguiente flip-flop detecta este flanco de bajada, pero aun su salida permanece en cero debido al tiempo de respuesta del flip-flop para llevar su salida Q1 a 1, durante este tiempo la salida del contador tiene el estado cero hasta que trascurrido el tiempo de respuesta lleva a su salida a 1 y se Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II obtiene finalmente el conteo “010”. Estos estados transitorios no son visualizados en los leds o el display conectado a la salida del contador, ellos no son capaces de responder a estos cambios momentáneos del contador, una vez estabilizado el conteo se leerá en el displays o los leds. Ejercicio propuesto. Diseñar un contador asíncrono ascendente módulo 16 utilizando el C.I 74XX109. El contador debe poseer la entrada de reset asíncrona. 2.2.2. Contadores Ascendente con módulo menor a 2n Son llamados contadores con módulo truncado, aunque se tenga n salidas no se tienen n los 2 estados a su salida, su implementación es similar a un contador ascendente con módulo 2n, solo que se debe colocar un circuito lógico combinacional que tiene como entradas las salidas del contador y la salida de este bloque va a la entrada de reset (RST) del contador, ver la figura 2,6. En el bloque combinacional se debe colocar un circuito decodificador del estado donde se quiere truncar el conteo con la finalidad de colocar en la entrada de reset del contador el nivel activo para llevar al contador a su inicialización, que puede ser cero o cualquier estado menor al que se utiliza para truncar. RST Módulo=2 n CLK Q n-1 Q2 Q1 Q0 CLC Figura 2.6. Contador asíncrono ascendente con módulo < 2n Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Ejemplo. Diseñar un contar módulo 5. Si es módulo 5 el contador debe pasar por 5 estados diferentes por tanto se requieren de 3 flip-flop, estos estados pueden ser: 0,1,2,3,4,0….., pero también puede ser 2,3,4,5,6,2.. ó 3,4,5,6,7,3 y así cualquiera secuencia consecutiva entre el estado 0 y el estado 7 que son todos los estados posibles con 3 flip-flop como se observa en la siguiente tabla. Q2 Q1 Q0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Si se escoge la primera secuencia: 0, 1, 2, 3, 4,0... , se debe colocar a la salida del contador un circuito tal que al tener a la salida el contador el número 5 el circuito coloque el nivel adecuado a la señal de reset del contador para llevarlo en forma asíncrona al estado cero. RST Módulo 8 CLK Q2 Q1 Q0 Figura 2.7. Contador asíncrono ascendente con módulo =5 Se coloca a la salida del contador una compuerta NAND de tres entradas cuya salida va ser cero cuando en el contador se encuentre el estado lógico 5 y con ello se realiza el reset Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II asíncrono, es decir se comienza de nuevo el conteo y de esta forma se estaría contando desde el cero al cuatro, a pesar que a la salida del contador se tiene el cinco cuando el conteo se observa a través de leds ó display este conteo no se ve puesto que tan solo permanece el tiempo equivalente al tiempo de propagación de la compuerta que se utilice y este no es un tiempo suficiente para que los visualizadores desplieguen este valor, sin embargo se puede observar utilizando un osciloscopio adecuado. En la tabla anterior se puede observar que para el conteo ascendente los 1 lógicos van apareciendo por lo cual se puede utilizar sólo las salidas del contador que tienen un 1 lógico porque se garantiza que esa combinación de unos no va estar presente anteriormente. 2.2.3. Circuitos Integrados de Contadores Asíncronos Ascendentes 74xx93: Contador Binario Módulo 16 (0 al 15). Ejemplo de un contador MOD=2n Este dispositivo dispone internamente de un contador módulo 8 y un módulo 2, que si se conecta en cascada se obtiene un contador módulo 16. Es decir la salida Q0 se conecta a la entrada Clk1. En la figura 2.8 se muestra la configuración del dispositivo. MR1 MR2 CLK1 Módulo 8 Módulo 2 CLK0 Q3 Q2 Q1 Q0 Figura 2.8. Configuración interna 74xx93 El 74xx93 dispone de 2 entradas de reset asíncrono activas en alto, que al activarse coloca las salidas del contador en cero lógico. Estas entradas deben estar inactivas para que el Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II dispositivo pueda contar. Si observa la figura 2.8 ambas entradas deben estar en alto para poder realizar el RESET. El contador módulo 8 y el contador módulo 2 se pueden utilizar en forma independiente siempre y cuando no se trunque el módulo de los contadores, pues el truncamiento se realiza a través de la entrada de Reset y como el circuito es común para ambos, entonces el funcionamiento del otro es afectado. 74xx90: Contador BCD. Módulo 10 (0 al 9). Ejemplo de un contador MOD<2n Este dispositivo dispone internamente de un contador módulo 5 y un módulo 2, que si se conecta en cascada se obtiene un contador módulo 10. Es decir la salida Q0 se conecta a la entrada Clk1. En la figura 2.9 se muestra la configuración del dispositivo. MS1 MS2 MR1 MR2 CLK1 Módulo 8 Módulo 2 CLK0 Q3 Q2 Q1 Q0 Figura 2.9. Configuración interna 74xx90 El 74xx90 dispone de 2 entradas de reset asíncrono activas en alto (MR1 y MR2), que al activarse coloca las salidas del contador en cero lógico, estas entradas deben estar en cero lógico para que el dispositivo pueda contar. Si observa la figura 2.9 ambas entradas deben estar en alto para poder realizar el RESET. Adicionalmente dispone de 2 entradas de SET asíncrono activas en alto (MS1 y MS2), que al activarse coloca la salida del contador en nueve, estas entradas deben estar en cero lógico para que el dispositivo pueda contar. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II El contador módulo 5 y el contador módulo 2 se pueden utilizar en forma independiente siempre y cuando no se trunque el módulo de los contadores, pues el truncamiento se realiza a través de la entrada de Reset y como el circuito es común para ambos, entonces se afecta el funcionamiento del otro. A continuación se presenta las hojas de especificaciones proporcionada por los fabricantes de estos dispositivos. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Figura 2.10.Configuracion de pines 74X90 y 74xx93 Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Ejercicios Utilizando el 74xx93 Implemente los siguiente contadores: a) contador MOD=16, Contador MOD=12, contador módulo 100. Contadores Descendente con módulo igual a 2n 2.2.4. Son contadores con n salidas y los cuales con cada pulso de reloj harán el conteo hacia abajo desde una cuenta igual a 2n – 1 hasta una cuenta igual a cero y luego su próximo conteo es el 2n – 1 , es decir se repite la secuencia. Para estos contadores el flip flop menos significativo conmuta en cada estado, el siguiente flip flop cada 2 estado el tercero cada 4 estado y así sucesivamente, es decir cada salida X, cambia cada 2 X estado, X indica el valor posicional de la salida y va desde 0 hasta n-1. Para contadores con módulo igual a 2n se requieren n flip-flop, por tanto si se desea diseñar un contador módulo 4 se necesitan 2 salidas del contador para poder obtener los conteo binario “11”, “10”, “01” y “00”, por tanto se requieren dos flip-flop, uno para cada salida, y así si se desea diseñar un contador módulo 8 se necesitan 3 salidas del contador para poder obtener los 8 estados diferentes y por tanto se requieren tres flip-flop, uno para cada salida y así sucesivamente para contadores con módulo 16, 32, 64, etc. Para un contador módulo 8 se requieren 3 Flip Flop para realizar el conteo descendente Simbología: Conteo: Inicio Módulo 8 CLK Q2 Q1 Q0 Q2 Q1 Q0 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 0 0 0 Figura 2.11. Simbología y tabla de la secuencia de conteo de un contador Ascendente De la tabla se puede realizar el análisis para implementar el contador: Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Se deben utilizar flip flop en modo de conmutación los cuales pueden ser el tipo J-K ó el tipo T y a través de su entrada de reloj CLK se controla el instante en que debe hacer la conmutación. Entonces observando la tabla tenemos: La salida Q0 del primer flip flop conmuta en cada estado, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK se debe conectar el reloj externo. La salida Q1 conmuta cada vez que la salida Q0 pasa de 0 a 1, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK debe ir conectada la salida Q0 , si el flip-flop es disparado por flanco de bajada y Q0 si el flip.flop es disparado por flanco de subida La salida Q 2 conmuta cada vez que la salida Q1 pasa de 0 a 1, por tanto este flip-flop debe estar configurado en modo de conmutación y en su entrada CLK debe ir conectada la salida Q1 , si el flip-flop es disparado por flanco de bajada y Q1 si el flipflop es disparado por flanco de subida Si se desea llevar la salida del contador en cualquier momento a una cuenta igual a 2n – 1 se bebe utilizar flip-flop que tenga la entrada asíncrona Pre-set, las cuales debe estar todas conectadas y colocando un nivel activo en esta entrada Inicio, el contador se encuentra en su máximo conteo, es decir en el estado 2n – 1, para que el contador cuente el pulso de reloj esta entrada debe estar en su estado inactivo. Si la entrada asíncrona de clear esta disponible en los biestable esta debe colocarse en su nivel inactivo, no debe dejarse sin conectar. En la figura 2.12, se implementa un contador descendente módulo 8 utilizando flip flop J-K con entradas de excitación activas en alto y entradas asíncronas Pre-set y Clear activas en bajos y con un tiempo de propagación de 25 nseg. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Inicio Q P J Vcc P Q Vcc J K K Q C Clk Q C Clk Q P J Vcc K Q Entrada de reloj (CLK) C Clk Vcc Q2 Q0 Q1 Figura 2.12. Implementación de un contador asíncrono descendente MOD=8 Este procedimiento debe seguirse para el diseño de cualquier contador asíncrono descendente con módulo 2n. Diagrama de tiempo del contador módulo 8 CLK 25 nseg Q0 Q0 50 nseg Q1 Q1 75 nseg Q2 7 6 5 4 3 2 1 0 7 Estado transitorio “111” por el que pasa el contador para finalmente colocar el estado “101” a su salida Figura 2.13. Diagrama de tiempo del contador módulo 8 Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II 2.2.5. Contadores Descendente con módulo menor a 2n Son llamados contadores con módulo truncado, aunque se tenga n salidas no se tienen los 2 n estados a su salida, su implementación es similar a un contador descendente con módulo 2n solo que se debe colocar un circuito lógico combinacional (CLC) que tiene como entradas las salidas del contador y la salida de este bloque va a la entrada de Inicio del contador. En el bloque combinacional se debe colocar un circuito decodificador del estado donde se quiere truncar el conteo con la finalidad de colocar en la entrada de Inicio del contador el nivel activo para llevar al contador a su inicialización, que puede ser su máximo conteo o cualquier estado mayor al que se utiliza para truncar. Inicio Módulo = 2N CLK CLC Q n-1 Q1 Q0 Figura 2.14. Contador asíncrono descendente con módulo < 2n Ejemplo. Diseñar un contar módulo 5. Si es módulo 5 el contador debe pasar por 5 estados diferentes por tanto se requieren de 3 flipflop, estos estados pueden ser: 7,6,5,4,3,7….., pero también puede ser 6,5,4,3,2,6.. ó 4,3,2,1,0,4 y así cualquiera secuencia consecutiva entre el estado 7 y el estado 0 que son todos los estados posibles con 3 flip-flop como se observa en la siguiente tabla. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Q2 Q1 Q0 1 1 1 1 1 0 1 0 1 1 0 0 0 1 1 0 1 0 0 0 1 0 0 0 Si se escoge la primera secuencia: 7, 6, 5, 4, 3,... se debe colocar a la salida del contador un circuito tal que al tener a la salida el contador el número 2 el circuito coloque el nivel adecuado a la señal de inicio del contador para llevarlo en forma asíncrona al estado siete. Inicio Módulo 8 CLK Q2 Q1 Q0 Figura 2.15. Contador asíncrono descendente con MOD= 5 Se coloca a la salida del contador una compuerta OR de tres entradas cuya salida va ser cero cuando en el contador se encuentre el estado lógico 2 y con ello se realiza el Inicio asíncrono, es decir se comienza de nuevo el conteo y de esta forma se estaría contando desde el siete al Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II tres, a pesar que a la salida del contador se tiene el dos cuando el conteo se observa a través de leds ó display este conteo no se vé puesto que tan solo permanece el tiempo equivalente al tiempo de propagación de la compuerta que se utilice y este no es un tiempo suficiente para que los visualizadores desplieguen este valor, sin embargo se puede observar utilizando un osciloscopio adecuado. En la tabla anterior se puede observar que para el conteo descendente los 0 lógicos van apareciendo por lo cual se puede utilizar solo las salidas del contador que tienen un 0 lógico porque se garantiza que esa combinación de ceros no va estar presente anteriormente. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II Ejercicios de repaso 1.- Diseñe un contador asíncrono ascendente módulo 16 utilizando 74XX76. Debe poseer RESET externo. 2.- Diseñe un contador asíncrono descendente módulo 16 utilizando 74XX76. Debe poseer RESET externo. 3.- Diseñe un contador asíncrono ascendente módulo 11 utilizando 74XX76. Debe poseer RESET externo. 4.- Diseñe un contador asíncrono descendente módulo 11 utilizando 74XX76. Debe poseer RESET externo. 5.- Diseñe un contador asíncrono ascendente desde 2 hasta 13, el circuito debe posee RESET externo. El tipo de biestable que se utiliza para su diseño es 74XX109 6.-Diseñe un contador asíncrono módulo 12 descendente desde 14 hasta 1, el circuito debe posee RESET externo. El tipo de biestable que se utiliza se 74XX109 7.- Implementente un contador asíncrono módulo 4 con las siguiente características M:=0 Ascendente, M:1 descendente Posee una señal externa de inicialización, que para M=0 coloca las salidas del contador en cero y para M=1 en su máximo conteo. Tanto para A/D su mínimo conteo es cero. 8.-Diseñe un contador asíncrono módulo 14 ascendente / descendente. El tipo de biestable que se utiliza para su diseño 7476. El contador que se diseña posee un RESET externo: si es ascendente se inicializa en cero y si es descendente se inicializa en su mayor conteo. Nota: En ambos caso su menor conteo es el cero. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II 9.- Implementente un contador binario asíncrono ascendente módulo 26 utilizando el biestable 74109. Posee una señal externa de inicialización, que coloca las salidas del contador en su mínimo conteo 0. 10.- Diseñe un contador BCD asíncrono ascendente módulo 26. Utilizando el biestable 74XX76. El conteo se debe visualizar en Displays. 11.- Implementente un contador asíncrono descendente binario módulo 13 utilizando 74109. El contador posee una señal externa de inicialización, que coloca las salidas del contador en su mínimo conteo 2. 12.- Realice las conexiones del 7490 de manera que pueda contar: a. De 0 a 9 , 1, 2, 3, 4, 5, 6, 7, 8, 9, 0, 1... b. De 0 a 6. 0, 1, 2, 3, 4, 5, 6, 0, 1... c. De 9 a 3. 9, 0, 1, 2, 3, 9, 0... d. De 0 a 8. 0, 1, 2, 3, 4, 5, 6, 7, 8, 0, 1... e. Biquinary 13.- Realice las conexiones del 7493 de manera que pueda contar: a. De 0 a 15 , 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 0, 1... b. De 0 a 6. 0, 1, 2, 3, 4, 5, 6, 0, 1... 14.-Realice un circuito que sea capaz de: .- Contar en BCD desde 0 a 85 utilizando el 7490 .- Contar en BCD desde 0 a 85 utilizando el 7493 Prof: Zulay Franco Puerto Ordaz, Mayo 2014.- Electrónica Digital II .- Contar en Binario desde 0 a 85 utilizando el 7490 .- Contar en Binario desde 0 a 85 utilizando el 749332 15.- Utilizando 7493 diseñe un contador BCD desde 000 a 125. 16.- Utilizando el 7490 diseñe un contador binario asíncrono módulo 41 17.- Utilizando el 7490 diseñe un contador octal asíncrono módulo (41)d. 18- Implemente un contador octal módulo 31 utilizando el 7493. Visualizar en Displays y utilizar el menor número posibles de integrados. Diseñe la señal se reloj utilizando el 74279. 19.- Utilizando el C.I 7474 diseñe un contador asíncrono módulo 6 Ascendente/descendente. Debe poseer un pulsador que lo inicializa en cero cuando cuenta en ascendente o en su máximo conteo cuando cuenta en descendente. ¿ Cree Ud. que este contador presentará el problema del laboratorio cuando cuenta en descendente?. ¿En cuál conteo? Y como lo puede corregir? Explique 20.-Diseñe un contador que realice el siguiente conteo: 00, 01,02,03,04,15,16,20,21....64,00 21.- Utilizando el 7490 diseñe un circuito que siga el siguiente conteo: 00,01,02,13,14,25,26,30,31,32,43.............74,00,01... 22.- Utilizando el 7493 realice un circuito decodificador de un teclado matricial. El circuito debe poseer reset externo. Prof: Zulay Franco Puerto Ordaz, Mayo 2014.-