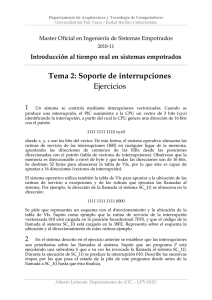

funcionamiento de interrupciones

Anuncio

Sistemas Digitales II Interrupciones en el µC51. INTRODUCCIÓN Una interrupción es la ocurrencia de un evento o condición la cuál causa una suspensión temporal del programa mientras la condición es atendida por otro subprograma. Una interrupción dá la apariencia de que un sistema realiza varias tareas simultáneamente, pero la CPU sólo puede ejecutar una instrucción cada ciclo de máquina. El proceso anterior se conoce como SUBRUTINA. La diferencia de un sistema con interrupciones es que la interrupción no se genera con una instrucción CALL, sino en respuesta a una llamada generada por HARDWARE o por SOFTWARE. El programa que se ejecuta cuando se genera una interrupción se llama: RUTINA DE ATENCIÓN A INTERRUPCIÓN (ISR). Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. INTRODUCCIÓN Cuando se genera una interrupción el programa principal se detiene y “salta” a atender la llamada a interrupción (subrutina). La ISR se ejecuta y regresa al programa principal mediante la instrucción de retorno de interrupción RETI, entonces, el programa principal continua desde donde ocurrió la interrupción. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. TIPOS DE INTERRUPCIONES La familia de los µC51 tiene cinco fuentes de interrupción: 2 interrupciones externas, 2 interrupciones por timer y 1 interrupción por puerto serial. Después de un reset al sistema, todas las interrupciones son deshabilitadas y se habilitan individualmente por software. Cada una de las fuentes de interrupción es habilitada o deshabilitada individualmente mediante direccionamiento por bit en el registro de funciones especiales (SFR) IE. Además, pueden habilitarse o deshabilitarse las interrupciones de manera global. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. VECTORES DE INTERRUPCIONES Cuando una interrupción es aceptada, el valor cargado dentro del PC es llamado VECTOR DE INTERRUPCIÓN. Este es una dirección en la cual se tiene el inicio de la ISR solicitada. Los vectores de interrupción que son direccionados cuando ocurre alguna interrupción están distribuidos dentro de la memoria de programa espaciados 8 bytes cada uno: Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Registro SFR IE (Interrupt Enable) Este registro se utilíza para controlar el funcionamiento de las interrupciones (bits IE.0 hasta IE.7). EA (IE.7). Bit de control de habilitación global de interrupciones. ES (IE.4). Bit de control de habilitación de interrupción por puerto serie. ET1 (IE.3). Bit de control de habilitación de interrupción por timer 1. EX1 (IE.2). Bit de control de habilitación de interrupción externa 1. ET0 (IE.1). Bit de control de habilitación de interrupción por timer 0. EX0 (IE.0). Bit de control de habilitación de interrupción externa 0. bit = 1, hab. int.; bit = 0, deshab. int. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Registro SFR TCON (Control Timer) Este registro se utilíza para controlar el modo de operación de las interrupciones externas (bits TCON.0 hasta TCON.3). IE1 (TCON.3). Bandera de sobre flujo de interrupción externa 1. IT1 (TCON.2). Bit de control de interrupción por nivel bajo ó flanco negativo de la interrupción externa 1. (0 = nivel, 1 = flanco) IE0 (TCON.1). Bandera de sobre flujo de interrupción externa 0. IT0 (TCON.0). Bit de control de interrupción por nivel bajo ó flanco negativo de la interrupción externa 0. (0 = nivel, 1 = flanco) Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Prioridades de las Interrupciones Existen dos niveles de interrupción: alta prioridad y baja prioridad de interrupción. Una prioridad baja puede ser interrumpida por una prioridad alta, pero no por otra de baja prioridad, es decir, una de alta prioridad trabaja como interrupción no mascarable. Si dos fuentes de interrupción son recibidas simultaneamente, se ejecutará la rutina de interrupción que tenga la mayor prioridad de las dos. Si dos fuentes de interrupción tienen la misma prioridad, entonces se ejecutará una secuencia aleatoria (polling) la cuál determinará la atención a dicha interrupción. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Registro SFR IP (Interrup Priority) Este registro se utilíza para asignar el nivel de prioridad para cada interrupción. (bits IP.0 hasta IP.4). PS (IP.4). Bit de prioridad para interrupción por puerto serie. PT1 (IP.3). Bit de prioridad para interrupción por timer 1. PX1 (IP.2). Bit de prioridad para interrupción externa 1. PT0 (IP.1). Bit de prioridad para interrupción por timer 0. PX0 (IP.0). Bit de prioridad para interrupción externa 0. bit = 1, prioridad alta; bit = 0, prioridad baja Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES Registro SFR PCON (Power Control) Este registro se utilíza para controlar el consumo de energia por el microcontrolador. Esto se consigue mediante dos modos de operación. SMOD (PCON.7). Bit para doblar la velocidad comunicación del puerto serie en los modos 1 y 2. de PD (PCON.1). Bit de control para modo POWER DOWN. IDL (PCON.0). Bit de control para modo IDLE MODE. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES POWER DOWN (Modo de bajo consumo). En este modo el oscilador se detiene, y por tanto, todas las funciones son desactivadas, pero la RAM interna se mantiene. La zona de SFR’s no se mantiene. Vcc puede ser reducida para minimizar el consumo de corriente despues de entrar en el modo POWER DOWN y ha de ser reestablecida antes de volver al modo normal, dejando un lapso de tiempo suficiente para que el oscilador se estabilice (normalmente menos de 10 mseg). La única manera de salir de este modo es mediante un RESET externo. Ing. Ricardo Godínez Bravo. Sistemas Digitales II Interrupciones en el µC51. FUNCIONAMIENTO DE INTERRUPCIONES IDLE MODE (Modo de espera). En este modo se conservan los datos de: SP, PC, PSW, Acc y Registros. La señal de reloj no se envia a la CPU, pero sí a los circuitos de interrupción, Timer’s y USART. Para iniciar este modo se ha de activar el bit IDL. La manera de salir de este modo es mediante un RESET externo ó al reconocer la solicitud de alguna fuente de interrupción. Ing. Ricardo Godínez Bravo.