PRÁCTICA 2. Programación de un sumador

Anuncio

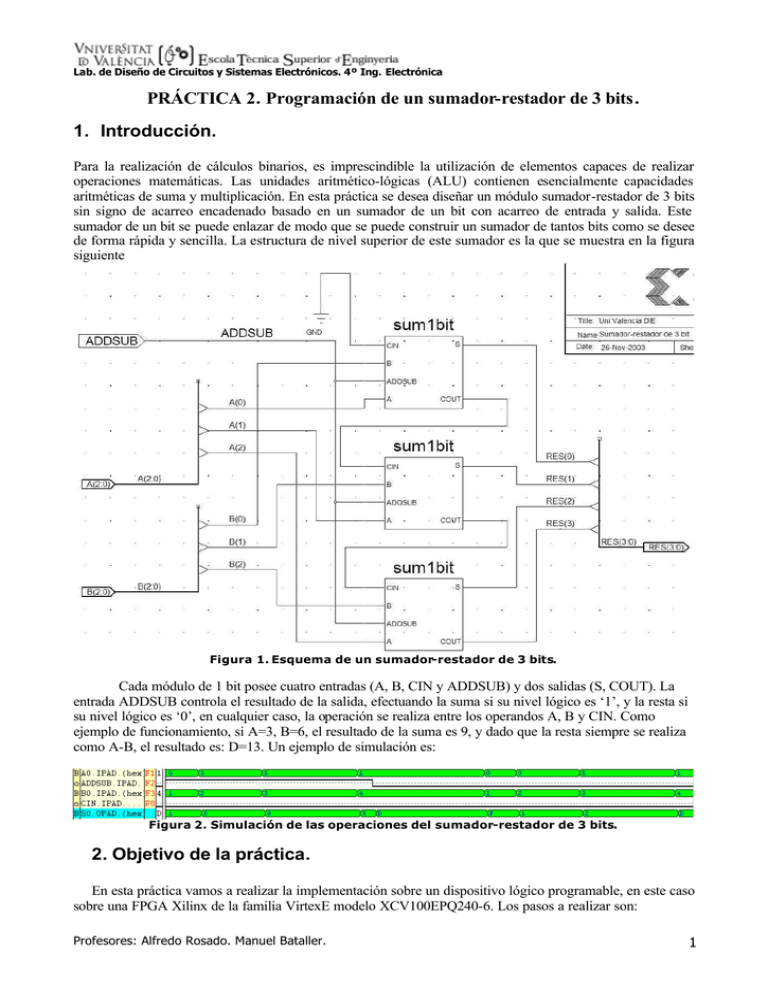

Lab. de Diseño de Circuitos y Sistemas Electrónicos. 4º Ing. Electrónica PRÁCTICA 2. Programación de un sumador-restador de 3 bits. 1. Introducción. Para la realización de cálculos binarios, es imprescindible la utilización de elementos capaces de realizar operaciones matemáticas. Las unidades aritmético-lógicas (ALU) contienen esencialmente capacidades aritméticas de suma y multiplicación. En esta práctica se desea diseñar un módulo sumador-restador de 3 bits sin signo de acarreo encadenado basado en un sumador de un bit con acarreo de entrada y salida. Este sumador de un bit se puede enlazar de modo que se puede construir un sumador de tantos bits como se desee de forma rápida y sencilla. La estructura de nivel superior de este sumador es la que se muestra en la figura siguiente Figura 1. Esquema de un sumador-restador de 3 bits. Cada módulo de 1 bit posee cuatro entradas (A, B, CIN y ADDSUB) y dos salidas (S, COUT). La entrada ADDSUB controla el resultado de la salida, efectuando la suma si su nivel lógico es ‘1’, y la resta si su nivel lógico es ‘0’, en cualquier caso, la operación se realiza entre los operandos A, B y CIN. Como ejemplo de funcionamiento, si A=3, B=6, el resultado de la suma es 9, y dado que la resta siempre se realiza como A-B, el resultado es: D=13. Un ejemplo de simulación es: Figura 2. Simulación de las operaciones del sumador-restador de 3 bits. 2. Objetivo de la práctica. En esta práctica vamos a realizar la implementación sobre un dispositivo lógico programable, en este caso sobre una FPGA Xilinx de la familia VirtexE modelo XCV100EPQ240-6. Los pasos a realizar son: Profesores: Alfredo Rosado. Manuel Bataller. 1 Lab. de Diseño de Circuitos y Sistemas Electrónicos. 4º Ing. Electrónica 1. Diseño del módulo sumador-restador de un bit. 2. Simulación del módulo sumador-restador de un bit. 3. Creación de un elemento de librería para obtener un símbolo capaz de ser utilizado como un elemento más. 4. Simulación funcional del módulo de 3 bits, probando los diversos modos de operación, es decir, en modo suma, en modo resta, y con varias combinaciones de entrada para A y B. 5. Generación de un módulo de nivel superior donde se realice una decodificación de las salidas para ser mostradas en un display de 7 segmentos, en este nivel también se incluirá una señal de entrada que permita visualizar un nuevo resultado de la suma de los elementos de entrada cada vez que ocurre el paso de estado bajo a alto para esta entrada. Se incluye una entrada de reset por la que cuando se activa, la salida toma un valor cero. 6. Simular el sistema total. El aspecto del dispositivo a nivel de entradas y salidas externas es el siguiente: Figura 3. Símbolo completo con entradas y salidas del sistema fina l a diseñar. 4. Diseño y simulación. Primeramente se debe diseñar el sumador-restador de un bit, una vez simulado, se genera un elemento de librería para el mismo. A continuación se diseña el sistema sumador-restador de 3 bit empleando el símbolo de librería que se acaba de crear. Una vez diseñado y simulado correctamente se genera otro símbolo de librería para el módulo de 3 bits. Como se desea visualizar el resultado en un display de 7 segmentos, se debe incluir en el proyecto el fichero hex2led.vhd proporcionado. Para este fichero VHDL, también se genera el símbolo esquemático. En nuevo esquema se incluye el módulo de 3 bits, el decodificador a 7 segmentos y la lógica necesaria para hacer que el sistema sólo actualice el cálculo cuando se le proporcione la orden desde la entrada “Actualiza”. Se simula el sistema completo y se comprueba que funciona correctamente. NOTA: Si se necesita poner señales de entrada a nivel lógico cero ó uno, en la librería de símbolos se dispone de los símbolos GND y VCC respectivamente. 5. Implementación. Una vez simulado, para que el diseño disponga de las entradas y salidas que corresponden a la ubicación de los interruptores y LED que existen en la placa, es necesario conocer el número de patilla donde cada uno se ubica. En los anexos a esta memoria se muestran unos esquemas y una descripción de la placa donde, junto con la exploración física de la placa disponible en el laboratorio, debéis ser capaces de encontrar el número de patilla que demos asignar a cada entrada y salida del diseño. Escribe a continuación la asignación de cada patilla: NET "suma<6>" LOC = ; NET "suma<5>" LOC = ; NET "suma<4>" LOC = ; NET "suma<3>" LOC = ; Profesores: Alfredo Rosado. Manuel Bataller. 2 Lab. de Diseño de Circuitos y Sistemas Electrónicos. 4º Ing. Electrónica NET NET NET NET NET NET NET NET NET NET NET NET "suma<2>" "suma<1>" "suma<0>" "reset" "a<2>" "a<1>" "a<0>" "addsub" "actualiza" "b<2>" "b<1>" "b<0>" LOC LOC LOC LOC LOC LOC LOC LOC LOC LOC LOC LOC = = = = = = = = = = = = ; ; ; ; ; ; ; ; ; ; ; ; Para realizar la asignación de patillas es necesario que en la ventana de fuentes añadamos una nueva fuente (New Source), en este caso del tipo User Constraint File. Una vez creada, aparece un fichero con extensión .ucf, que teniéndolo seleccionado ejecutaremos la opción de la ventana de procesos llamada User Constraints -> Assign Package Pins. Esta opción nos abre el editor PACE, donde tenemos las entradas y salidas que podemos llevar a la patilla a asignar. Figura 4. Imagen de PACE, editor de restricciones, empleado en este caso para asignar patillas en el dispositivo FPGA a emplear. Una vez realizada la asignación de patillas ya podremos proceder a la implementación del sistema. Para ello, ejecutaremos la opción Implement Design que automáticamente realizará el proceso de asignar los recursos lógicos. Si el proceso finaliza correctamente, visualizar los informes y buscar la información que se solicita a continuación: Number of Number of Number of IOB Slices: 4 input LUTs: bonded IOBs: Flip Flops: …………… out of …………… out of …………… out of ………………………… 1,200 2,400 158 6. Programación de la placa. Para generar el fichero que sirve para descargar el programa en la placa se ejecuta la acción Generate Programming File. Profesores: Alfredo Rosado. Manuel Bataller. 3 Lab. de Diseño de Circuitos y Sistemas Electrónicos. 4º Ing. Electrónica Figura 5. Ventanas de fuentes y procesos para el diseño de esta sesión. Una vez finalizado el proceso estaremos en disposición de encender la fuente de alimentación de la placa para posteriormente entrar dentro del programa iMPACT que es el encargado de configurar el proceso de programación. Al arrancar este programa aparece un asistente que solicita información acerca del tipo de programación que se desea realizar. Las opciones que se deben elegir son: Figura 6. Opciones a seleccionar en iMPACT para programar el dispositivo. El proceso de reconocimiento automático debe reconocer dos dispositivos de programación, una memoria EEPROM XC18v01 que no vamos a emplear y la FPGA, para ello, nos pedirá el fichero de programación de cada dispositivo, para el caso de la memoria, le decimos que lo ignore (Bypass), y para el caso de la FPGA procederemos a indicarle el fichero .bit que se nos ha generado en la carpeta de nuestro proyecto. Finalmente, el aspecto de iMPACT es el que sigue: Profesores: Alfredo Rosado. Manuel Bataller. 4 Lab. de Diseño de Circuitos y Sistemas Electrónicos. 4º Ing. Electrónica Figura 7. Ventana principal de iMPACT. Se selecciona la FPGA (se selecciona en un color verde), y se ejecuta la opción Operations -> Program, procediendo a la verificación de la misma. Profesores: Alfredo Rosado. Manuel Bataller. 5 Xilinx® Virtex™ -E Evaluation Kit November 28, 2000 (Version 1.1) DRAFT Features • FPGA Ÿ Xilinx® Virtex-E XCV100E-6PQ240C • SPROM Ÿ Xilinx® XC18V01SO20C • Board I/O Connectors Ÿ Two 50-pin, 0.1 Header connector Ÿ Pads for three MICTOR connectors Ÿ Pads for one 140 pin General Purpose I/O interface • Power Ÿ +5.0 Power Connector Ÿ +3.3 V Regulated Supply Ÿ +1.8 V Regulated Supply Ÿ Full Bypass Capacitance • Communication Ÿ RS232 Serial Port • Configuration Ÿ JTAG Header Connector Ÿ In-System Programmable PROM Ÿ JTAG Download Cable • Miscellaneous Ÿ 8 DIP switches Ÿ 2 Push-buttons, Ÿ Dual Digit 7 Segment LED, right hand decimal Ÿ Infrared Transceiver Ÿ 8 LEDs Ÿ 40 MHz Oscillator Ÿ Digital Thermometer • Demonstration application (Source VHDL) Ÿ Simple RS232 Ÿ Digital Thermometer Ÿ LED Patterns Advance Product Specification The Virtex-E device is located in the center of the board. It can be configured via a JTAG download or from the on board configuration PROM. The configuration PROM is also programmable through the JTAG cable. Over 85 IO signals are connected from the FPGA to 0.1 header connectors for user connections. Other IO are connected to 8 LED, 8 dip switches, Two push buttons, RS-232 line driver/receiver, and a digital thermometer. Demo Application. The board is supplied with complete VHDL source code that: 1) Sequences LEDs 2) Reads Dip Switches/push buttons 3) Senses Temperature and displays value on dual 7 segment LED 4) Transmits startup message through RS-232 connector. 5) Echoes RS-232 commands. (Serial cable not included) Description The Evaluation Virtex-E Kit is used by engineers as a platform to test FPGA designs that are targeted to the Xilinx Virtex-E device. It is also a great tool for beginners to get aquatinted with FPGAs and VHDL. Ordering Information The following table lists the development system part numbers and available software options. Internet Link at http://www.em.avnet.com/. Table 1 Evaluation Virtex-E Board Part Number ADS-XLX-VE-EVL November 28, 2000 (Version 1.1) Hardware Xilinx Virtex-E Evaluation Kit Literature # ADS-001205 ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Page - 1 Xilinx Virtex-E Evaluation Kit ADS Evaluation Virtex-E Board Virtex-E FPGA This section provides information basic to the design of Evaluation Virtex-E Board board. The Virtex-E Field-Programmable Gate Array device (U1) utilized in this design is the 100+K-system gate device (XCV100E) in a PQ240 package. FPGA Configuration Configuration information is provided from two sources; the JTAG Connector (JTAG0), and configuration PROM. Table 2 JTAG Connector Power The majority of the design is powered at 3.3V with the Virtex-E FPGA core powered at 1.8V. The board should be powered by a 5-volt bench supply. The 3.3V is derived via a linear regulator. A linear regulator from the 3.3V provides the 1.8V Xilinx core voltage. A barrel connector J3 (RAPC712) is provided on the board for lab supply connections. The center tap is +5.0 volts and the outer is GND. Note: The lab supply should be regulated at 5.0 volts. While current requirements are dependent on the user application, it is suggested to limit your supply to 1.5 amps on initial power up. φ0.098 in pin diameter φ0.25 in housing diameter Signal Name VCC TDI TMS TCK TDO GND JTAG Connector Pin # 1 2 3 4 5 6 Jumpers JP1, JP2 and JP3 select the configuration mode of the Virtex. The following table shows the jumper setting needed for each mode. Table 3 Mode Select Configuration Mode Master-serial Boundary-scan SelectMAP Slave-serial Master-serial Boundary-scan SelectMAP Slave-serial Pullups No No No No Yes Yes Yes Yes JP3/M2 JP2/M1 JP1/M0 OFF /LOW ON /HIGH ON /HIGH ON /HIGH ON /HIGH OFF /LOW OFF /LOW OFF /LOW OFF /LOW OFF /LOW ON /HIGH ON /HIGH OFF /LOW OFF /LOW ON /HIGH ON /HIGH OFF /LOW ON /HIGH OFF /LOW ON /HIGH OFF /LOW ON /HIGH OFF /LOW ON /HIGH The LED D1 indicates the output level of the DONE pin of the Virtex-E device. It will illuminate when the Virtex-E configuration is complete. +5.0 Volts GND System Clock Printed Circuit Board The Evaluation Virtex-E Board printed circuit board is an 6-layer board with four signal layers, a full 3.3V power plane incorporating an isolated 1.8V mini-plane, and full ground plane. The board stack-up layers 1 through 6 is: 1) ”Component side”/signal 2) Ground Plane 3) Signal 4) Signal 5) Power: 3.3V and 1.8V 6) ”Solder side”/signal Page - 2 Literature # ADS-001205 An oscillator socket clock output is connected to the Virtex-E device. U5 is connected to Global Clock Input #0 (PQ240 pin #P92), The U5 socket is populated with a 40 MHz oscillator. Asynchronous (RS232) Communication Interface The ADM3222 device provides level translation for a single RS232 interface (DB9 connector). The second translation port on the device is terminated and unused. November 28, 2000 (Version 1.1) ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Xilinx Virtex-E Evaluation Kit Table 4 RS232 Interface Signals RS232 SIGNAL R1OUT T1IN EN_N SD_N Virtex-E PIN # P216 P217 P218 P219 Table 5 RS232 Connector Pinout Signal Name TX out RX in GND P2 (DB9) connector Pin # 2 3 5 Miscellaneous The “Miscellaneous” interfaces on the Virtex-E board consist of a single 8-position DIP switch (8-individual SPST switches), 8 LEDs, and two push-button switches. Table 9 Dual Segmented LED Signals LED A1 B1 C1 D1 E1 F1 G1 Dp1 A2 B2 C2 D2 E2 F2 G2 Dp2 Virtex-E PIN # P221 P222 P223 P224 P228 P229 P230 P231 P234 P235 P236 P237 P238 P186 P187 P188 Table 6 Dip Switch Signals DIP SW #1 #2 #3 #4 #5 #6 #7 #8 Virtex-E PIN # P194 P195 P199 P200 P201 P202 P203 P205 Table 7 Push Button Switch Signals BUTTON SW1 SW2 Virtex-E PIN # P206 P208 Table 10 Infrared Signals LED TXD RXD SHDN Virtex-E PIN # P102 P101 P100 Table 11 Digital Themometer LED CE SCLK SDI SDO Virtex-E PIN # P160 P159 P161 P162 Table 8 LED Control Signals LED D2 D3 D4 D5 D6 D7 D8 D9 Virtex-E PIN # P27 P28 P3 P4 P5 P6 P7 P9 November 28, 2000 (Version 1.1) Literature # ADS-001205 ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Page - 3 Xilinx Virtex-E Evaluation Kit Table 13 GPIO Signals JP6 I/O Signal Headers Two 50-pin connectors provides 84 Virtex-E I/O lines and 6 ground pins. Table 12 GPIO Signals JP5 GPIO CONNECTOR PIN # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 Page - 4 Virtex-E PIN # P86 P84 P82 P81 P80 P79 P78 P74 P73 P72 P71 P70 P68 P67 P66 P65 P64 P63 P99 P97 P96 P95 P94 P118 P117 P115 P114 P113 P111 P110 P109 P108 P149 P147 P144 P142 P141 P140 P134 P133 P132 P131 P130 Reserved Reserved Reserved Reserved GND GND GND Literature # ADS-001205 GPIO CONNECTOR PIN # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 Virtex-E PIN # P31 P33 P34 P35 P36 P38 P39 P40 P41 P42 P46 P47 P48 P49 P50 P52 P53 P54 P56 P57 P10 P11 P12 P13 P17 P18 P19 P20 P21 P23 P24 P26 P128 P127 P126 P125 P175 P174 P173 P171 P170 P169 Reserved Reserved Reserved Reserved Reserved GND GND GND November 28, 2000 (Version 1.1) ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Xilinx Virtex-E Evaluation Kit Logic Analyzer Connector Table 15 MICTOR J5 Three AMP™ MICTOR connector pads are provided to connect to a logic analyzer’s mass termination cable. Table 14 MICTOR J4 Connector PIN # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 Virtex-E PIN # N/C N/C N/C N/C P210* P92 P108 P65 P109 P66 P110 P67 P111 P68 P113 P70 P114 P71 P115 P72 P117 P73 P118 P74 P94 P78 P95 P79 P96 P80 P97 P81 P99 P82 P63 P84 P64 P86 GND GND GND GND GND November 28, 2000 (Version 1.1) Name N/C N/C N/C N/C CLK_OUT OSC ADDRESS31 ADDRESS15 ADDRESS30 ADDRESS14 ADDRESS29 ADDRESS13 ADDRESS28 ADDRESS12 ADDRESS27 ADDRESS11 ADDRESS26 ADDRESS10 ADDRESS25 ADDRESS9 ADDRESS24 ADDRESS8 ADDRESS23 ADDRESS7 ADDRESS22 ADDRESS6 ADDRESS21 ADDRESS5 ADDRESS20 ADDRESS4 ADDRESS19 ADDRESS3 ADDRESS18 ADDRESS2 ADDRESS17 ADDRESS1 ADDRESS16 ADDRESS0 GND GND GND GND GND Connector PIN # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 Virtex-E PIN # N/C N/C N/C N/C P213* P89* P26 P52 P24 P50 P23 P49 P21 P48 P20 P47 P19 P46 P18 P42 P17 P41 P13 P40 P12 P39 P11 P38 P10 P36 P57 P35 P56 P34 P54 P33 P53 P31 GND GND GND GND GND Name N/C N/C N/C N/C GCK3 GCLK1 DATA31 DATA15 DATA30 DATA14 DATA29 DATA13 DATA28 DATA12 DATA27 DATA11 DATA26 DATA10 DATA25 DATA9 DATA24 DATA8 DATA23 DATA7 DATA22 DATA6 DATA21 DATA5 DATA20 DATA4 DATA19 DATA3 DATA18 DATA2 DATA17 DATA1 DATA16 DATA0 GND GND GND GND GND Literature # ADS-001205 ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Page - 5 Xilinx Virtex-E Evaluation Kit Table 16 MICTOR J6 Connector PIN # Virtex-E PIN # N/C N/C N/C N/C P210* P191* P178 P175 P208 P125 P206 P126 P162 P127 P161 P128 P160 P130 P159 P131 P220 P132 P218 P133 P217 P139 P216 P140 P169 P141 P170 P142 P171 P144 P173 P147 P174 P149 GND GND GND GND GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 Table 17 AvBus Connector P2 Name Name N/C N/C N/C N/C CLK_OUT CLK_IN DOUT CNTL15 SWITCH9 CNTL14 SWITCH8 CNTL13 TEMP_SDO CNTL12 TEMP_SDI CNTL11 TEMP_CE CNTL10 TEMP_SCLK CNTL9 RS232SD_N CNTL8 RS232EN_N CNTL7 RS232TX CNTL6 RS232RX CNTL5 CNTL20 CNTL4 CNTL19 CNTL3 CNTL18 CNTL2 CNTL17 CNTL1 CNTL16 CNTL0 GND GND GND GND GND ADDRESS0 GND ADDRESS3 ADDRESS4 GND ADDRESS7 ADDRESS8 AUX_+3.3V ADDRESS11 ADDRESS12 GND ADDRESS15 ADDRESS16 GND ADDRESS19 ADDRESS20 GND ADDRESS23 ADDRESS24 AUX_+3.3V ADDRESS27 ADDRESS28 GND ADDRESS31 DATA0 GND DATA3 DATA4 GND DATA7 DATA8 AUX_+3.3V DATA11 DATA12 GND DATA15 DATA16 GND DATA19 DATA20 GND DATA23 DATA24 AUX_+3.3V DATA27 DATA28 GND DATA31 CNTL0 GND CNTL3 CNTL4 GND CNTL7 CNTL8 AUX_+3.3V CNTL11 *Note: A zero ohm resistor may be required to access the noted signals. AvBus Connector High-density connector pads are located on bottom of the board. The signals are listed in the following table. Page - 6 Literature # ADS-001205 FPGA PIN # P86 GND P81 P80 GND P74 P73 +3.3V P70 P68 GND P65 P64 GND P97 P96 GND P118 P117 +3.3V P113 P111 GND P108 P31 GND P35 P36 GND P40 P41 +3.3V P47 P48 GND P52 P53 GND P57 P10 GND P13 P17 +3.3V P20 P21 GND P26 P149 GND P142 P141 GND P133 P132 +3.3V P128 Connector PIN # 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 FPGA PIN # N/C P84 P82 GND P79 P78 GND P72 P71 GND P67 P66 N/C P63 P99 GND P95 P94 GND P115 P114 GND P110 P109 N/C P33 P34 GND P38 P39 GND P42 P46 GND P49 P50 N/C P54 P56 GND P11 P12 GND P18 P19 GND P23 P24 N/C P147 P144 GND P140 P139 GND P131 P130 Name N/C ADDRESS1 ADDRESS3 GND ADDRESS5 ADDRESS6 GND ADDRESS9 ADDRESS10 GND ADDRESS13 ADDRESS14 N/C ADDRESS17 ADDRESS18 GND ADDRESS21 ADDRESS22 GND ADDRESS25 ADDRESS26 GND ADDRESS29 ADDRESS30 N/C DATA1 DATA2 GND DATA5 DATA6 GND DATA9 DATA10 GND DATA13 DATA14 N/C DATA17 DATA18 GND DATA21 DATA22 GND DATA25 DATA26 GND DATA29 DATA30 N/C CNTL1 CNTL2 GND CNTL5 CNTL6 GND CNTL9 CNTL10 November 28, 2000 (Version 1.1) ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Xilinx Virtex-E Evaluation Kit Name CNTL12 GND CNTL15 CNTL16 GND CNTL19 CNTL20 GND CLK_OUT TMS AUX_+3.3V TDI TRS FPGA PIN # P127 GND P175 P174 GND P170 P169 GND P210* ⊕ +3.3V ⊕ ⊕ Connector PIN # 128 129 130 131 132 133 134 135 136 137 138 139 140 58 59 60 61 62 63 64 65 66 67 68 69 70 FPGA PIN # GND P126 P125 N/C P173 P171 GND P191* P210* GND ⊕ ⊕ GND Name GND CNTL13 CNTL14 N/C CNTL17 CNTL18 GND CLK_IN CLK_OUT_FB GND TDO TCK GND *Note: A zero ohm resistor may be required to access the noted signals. ⊕ Note: Reference Schematic for current JTAG signal paths. Demonstration Program Supplied with the development system is a demonstration program file that utilizes several devices on the evaluation board. The demonstration program uses the evaluation development board as a standalone platform that is connected to a lab supply and a terminal emulation program. On power up the onboard PROM will configure the FPGA. Upon completion of the configuration the FPGA functionality and input/output signal will activate. A start up serial message will be sent to the terminal port via the RS-232 connection. The LEDs will display a back and forth scanning pattern or 8-bit value corresponding to the current temperature. The Dual segmented display will count up or display the current temperature. Additional Items Needed: Lab power supply, 5.0 volts at 1.5 amps. Serial Terminal or Terminal Emulator. RS-232 cable Ÿ Ÿ Ÿ Setup: 1) Attach the lab supply to the power connector on the Evaluation Board. 2) Attach the serial terminal to the P1 connector of the Evaluation Board. 3) Set the Serial Terminal to: 8 data bits, 1 stop , No parity, 9600 baud. 4) Verify jumper are NOT installed on JP1,JP2,and JP3. 5) Verify JP4 is installed across pins 1 and 2. Power UP: 6) Apply power to the Evaluation Board. 7) The DONE LED D1 will light on the completion of the download. Reset: November 28, 2000 (Version 1.1) 8) Press the Soft Reset button SW1 to reset the board. Serial Demo 9) Press the button SW2 to send the startup message. 10) The Power up message is displayed on the serial terminal. 11) All characters typed should be echoed to the terminal. 12) Press the Reset button again to “reset” startup message. LED SCAN 13) Set the dipswitch S1 dip 1 to ON (rocker up). 14) The LEDs should be blinking such that the illuminated led should be scanning back and forth through the LED array. UP COUNTER 15) Set the dipswitch S1 dip 2 to ON (rocker down). 16) The Dual segmented LEDs should be counting up. TEMPERATURE 17) Set the dipswitch S1 dip 1 to OFF (rocker down). 18) The LED should now display the temperature in °C in two’s complement binary. See the following table. 19) Set the dipswitch S1 dip 2 to OFF (rocker down). 20) The Dual segmented LEDs should now display the temperature in °C. 21) Hold your finger on U5 to change the temperature. LED Pattern (D9..D2) 0111 1000 0001 1001 0000 1010 0000 0000 1111 0101 1110 0110 1100 1001 Decimal Value (°C) +120C +25C +10C 0C -10C -25C -55C Literature # ADS-001205 ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. Page - 7 Xilinx Virtex-E Evaluation Kit Document XILINX XC18V01 Configuration PROM Data Sheet Relevant Documents Documents relevant to this application are listed in the following table. Analog Devices ADM3222 3V RS232 Line Driver/Receiver Data Sheet Table 18. Relevant Documents and Links Document XILINX VIRTEX-E FPGA Data Sheet Source http://www.xilinx.com/parti nfo/ds026.pdf http://www.analog.com/pdf/ ADM3202_0.pdf Source http://www.xilinx.com/parti nfo/ds022.pdf Block Diagram Dual 8-Segment LED RS-232 Infrared Transceiver 8 Dip Switches XILINX VIRTEX-E XCV100E-6PQ240 FPGA 2 Push Buttons XILINX XC18V01SO20C 50 Pin Header Digital Thermometer 50 Pin Header 3 MICTORs 40MHz OSC AvBus Board to Board 140 Pin Connector 8 LEDS JTAG Header Configuration PROM Revisions Version 1.0 Version 1.1 Page - 8 Initial Release. Fixed typographical errors. Literature # ADS-001205 November 28, 2000 (Version 1.1) ©2000, Avnet, Inc. All rights reserved. Xilinx is a registered trademark of Xilinx, Inc. Virtex is a trademark of Xilinx, Inc. All other trademarks and registered trademarks are the property of their respective owners. 5 4 3 2 REV Mini-Virtex-E Evauation Board A SHEET DESCRIPTION ALL Initial Release 1 DATE 11-OCT-2000 Avnet Design Services www.em.avnet.com D Function D Sheet Number Lead Sheet 1 FPGA, SPROM 2 Power 3 Mictor and Header Connectors 4 Switch, LED, OSC 5 Daughter Board Connector 6 C C B B Copyright 2000, Avnet, Inc. All Rights Reserved. This material may not bereproduced, distributed, republished, displayed, posted, transmitted or copied in any form or by any means without the prior written permission of Avnet, Inc. AVNET and the AV logo are registered trademarks of Avnet, Inc. All trademarks and trade names are the properties of their respective owners and Avnet, Inc. disclaims any proprietary interest or right in trademarks, service marks and trade names other than its own. A Avnet is not responsiblefor typographical or other errors or omissions or for direct, indirect, incidental or consequential damages elated r to this material or resulting from its use. Avnet makes no warranty or representation respecting this material, which is provided on an "AS IS" basis. AVNET HEREBY DISCLAIMS ALL WARRANTIES OR LIABILITY OF ANY KIND WITH RESPECT THERETO, INCLUDING, WITHOUT LIMITATION, REPRESENTATIONS REGARDING ACCURACY AND COMPLETENESS, ALL IMPLIED WARRANTIES AND CONDITIONS OF MERCHANTABILITY,SUITABILITY OR FITNESS FOR A PARTICULAR PURPOSE, TITLE AND/OR NON-INFRINGEMENT. This material is not design ed, intended or authorized for use inmedical, life support, life sustaining or nuclear applications or applications in which the failure of the product could result in personal injury, death or property damage. Any party using or selling products for use in any suc h applications do so at their sole risk and agree that Avnet is not liable, in whole or inpart, for any claim or damage arising from such use, and agree to fully indemnify, defend and hold harmless Avnet from and ag ainst any and all claims, damages, loss, cost, expense or liability arising out of or in connection with the use or performance of products in such applications. A LIT# Avnet, Inc. 4 Copyright 2000 Title Mini-Virtex-E Board - Lead Sheet Size B Date: 5 Design Services ADS-001207 3 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 Sheet 1 1 of 6 D0 CNTL7 CNTL8 CNTL9 CNTL10 CNTL11 CNTL12 CNTL13 CNTL14 CNTL2 CNTL3 CNTL4 CNTL5 CNTL6 CNTL0 CNTL1 INIT_N 1 DONE CNTL[0:20] B Do Not Populate VCCO GCK3 IO_LVDS_DLL_L6N IO_VREF IO_L5P_Y IO_VREF_L5N_Y IO_L4P_Y IO_L4N_Y IO IO_L3P_YY IO_L3N_YY VCCO IO_L2P_YY IO_VREF_L2N_YY IO IO_VREF VCCO IO_L1P_YY IO_L1N_YY IO_VREF_L0P_Y IO_L0N_Y IO 212 213 215 216 217 218 220 221 222 223 224 226 228 229 230 231 232 234 235 236 237 238 FPGA_TDO 3 B Com 2 SP_TDI J2 CONN_TDO FPGA_TDO 3 2 SP_TDI A GCK3 M2 M1 M0 VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT VCCINT Com MODE2 MODE1 MODE0 62 58 60 88 77 43 32 225 214 198 164 16 148 137 104 J1 Do Not Populate 1 CF_N TCK SP_TDO TMS PROGRAM TCK TDI TMS 122 239 183 2 10 11 12 13 15 17 18 19 20 21 23 24 240 25 26 27 28 3 4 5 6 7 9 Do Not Populate D VCC JP1 RS232RX RS232TX RS232EN_N RS232SD_N SEG1_A SEG1_B SEG1_C SEG1_D 1 2 MODE0 R3 1 2 HEADER 2x1 10K JP2 1 2 MODE1 SEG1_E SEG1_F SEG1_G SEG1_Dp R4 1 2 HEADER 2x1 10K JP3 SEG2_A SEG2_B SEG2_C SEG2_D SEG2_E CONN_TDI CONN_TMS CONN_TDO CONN_TCK GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND 1 2 MODE2 R5 1 2 HEADER 2x1 CS_N WRITE_N SEG2_F SEG2_G SEG2_Dp R6 CLK_IN 1 0R0/0805 NOT POPULATED SWITCH0 SWITCH1 VCC VCC 2 1 1 R8 Do Not Install R7 Do Not Install R10 Do Not Install SWITCH[0:9] 2 1 R11 0R0/0805 NOT POPULATED 2 R9 Do Not Install SWITCH9 C WRITE_N 1 1 2 CS_N 2 SWITCH2 SWITCH3 SWITCH4 SWITCH5 SWITCH6 SWITCH7 SWITCH8 2 180 184 185 186 187 188 189 191 192 193 194 195 197 199 200 201 202 203 205 206 207 208 209 210 CLK_OUT 2 204 196 190 182 172 166 158 151 143 14 135 129 119 112 106 1 VIRTEX E - PQ240 149 147 146 145 144 142 141 140 139 138 136 134 133 132 131 130 128 127 126 125 124 123 121 120 IR_TXD IR_RXD IR_SHDN U1 GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND GND ADDRESS25 ADDRESS26 ADDRESS27 ADDRESS28 ADDRESS29 ADDRESS30 ADDRESS31 CONN_TCK +1.8V VCCO IO_CS_L14P_YY IO_WRITE_L14N_YY IO_L13P IO_VREF_L13N IO_L12P_YY IO_L12N_YY IO_VREF_L11P_YY IO_L11N_YY IO IO_VREF_L10P_YY IO_L10N_YY VCCO IO_L9P_YY IO_L9N_YY IO IO_L8P_Y IO_L8N_Y IO_VREF_L7P_Y IO_L7N_Y VCCO IO_VREF IO_LVDS_DLL_L6P GCK2 98 91 83 8 75 69 59 51 45 37 29 233 227 22 219 211 ADDRESS23 ADDRESS24 C 1 Do Not Populate R2 1 2 TCK 10K IO_L37N_Y IO_VREF_L38P_Y IO_L38N_Y IO_L39P IO_VREF_L39N IO_LVDS_DLL_L40P GCK0 VCCO IO_L32P_YY IO_L32N_YY VCCO IO_VREF IO_L33P_YY IO_L33N_YY IO_VREF_L34P_YY IO_L34N_YY IO IO_VREF_L35P_YY IO_L35N_YY VCCO IO_L36P_YY IO_L36N_YY IO IO_L37P_Y CNTL15 CNTL16 CNTL17 CNTL18 CNTL19 CNTL20 OSC_FB OSC 99 97 96 95 94 93 92 90 118 117 116 115 114 113 111 110 109 108 107 105 103 102 101 100 TDO CCLK IO_DOUT_BUSY_L15P_YY IO_DIN_D0_L15N_YY VCCO IO_VREF IO_L16P_Y IO_L16N_Y IO_VREF_L17P_Y IO_L17N_Y IO IO_VREF_L18P_Y IO_D1_L18N_Y VCCO IO_D2_L19P_YY IO_L19N_YY IO IO_L20P_Y IO_L20N_Y IO_VREF_L21P_Y IO_D3_L21N_Y IO_L22P IO_VREF_L22N IO_L23P_YY IO_L23N_YY VCCO ADDRESS18 ADDRESS19 ADDRESS20 ADDRESS21 ADDRESS22 181 179 178 177 176 175 174 173 171 170 169 168 167 165 163 162 161 160 159 157 156 155 154 153 152 150 ADDRESS7 ADDRESS8 ADDRESS9 ADDRESS10 ADDRESS11 ADDRESS12 ADDRESS13 ADDRESS14 ADDRESS15 ADDRESS16 ADDRESS17 FPGA_TDO CCLK ADDRESS1 ADDRESS2 ADDRESS3 ADDRESS4 ADDRESS5 ADDRESS6 GCK1 IO_LVDS_DLL_L40N IO_VREF VCCO IO_VREF_L41P IO_L41N IO IO IO_L42P_YY IO_L42N_YY VCCO IO_L43P_YY IO_VREF_L43N_YY IO IO_L44P_YY IO_VREF_L44N_YY IO_L45P_YY IO_L45N_YY IO_VREF_L46P_Y IO_L46N_Y IO_L47P_YY IO_L47N_YY VCCO IO_L61N_Y IO IO_VREF_L60P_Y IO_L60N_Y VCCO IO_L59P_YY IO_L59N_YY IO IO_L58P_Y IO_L58N_Y IO_VREF_L57P_Y IO_L57N_Y VCCO VCCO IO_VREF IO_L56P_YY IO_L56N_YY IO IO_L63P IO_VREF_L63N IO_L62P_Y IO_L62N_Y IO_VREF_L61P_Y 30 31 33 34 35 36 38 39 40 41 42 44 46 47 48 49 50 52 53 54 55 56 57 ADDRESS0 IO IO_VREF VCCO IO_D4_L24P_Y IO_VREF_L24N_Y IO_L25P_Y IO_L25N_Y IO IO_L26P_YY IO_D5_L26N_YY VCCO IO_D6_L27P_Y IO_VREF_L27N_Y IO IO_L28P_Y IO_VREF_L28N_Y IO_L29P_Y IO_L29N_Y IO_VREF_L30P IO_L30N IO_D7_L31P_YY IO_INIT_L31N_YY VCCO DONE GCK1 GCK1_FB ADDRESS[0:31] VCCO IO IO_VREF_L55P IO_L55N IO_L54P_Y IO_VREF_L54N_Y IO_L53P_Y IO_L53N_Y IO IO_L52P_YY IO_L52N_YY VCCO IO_L51P_Y IO_VREF_L51N_Y IO IO_L50P_Y IO_VREF_L50N_Y IO_L49P_Y IO_L49N_Y IO_VREF VCCO IO_L48P_YY IO_L48N_YY D 2 TMS CONN_TMS CONN_TDI DATA31 LED0 LED1 LED2 LED3 LED4 LED5 LED6 LED7 DATA24 DATA25 DATA26 DATA27 DATA28 DATA29 DATA30 DATA20 DATA21 DATA22 DATA23 DATA18 DATA19 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 DATA16 DATA17 R1 3.3V 89 87 86 85 84 82 81 80 79 78 76 74 73 72 71 70 68 67 66 65 64 63 61 1 LED[0:7] DATA0 DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DATA8 DATA9 DATA[0:31] 2 1 3 A 4 B 5 NOT POPULATED 1 CLK_OUT_FB R12 0R0/0805 JTAG_TRS JTAG_TDI JTAG_TMS JTAG_TDO JTAG_TCK TEMP_SCLK TEMP_CE TEMP_SDI TEMP_SDO B R13 DOUT 2 1K D1 QTLP650C-4 D0 CF_N U2 3 8 10 1 16 2 15 7 14 9 12 VCC CLK VCC RST/OE VCC CE VCCO GND D0/DATA D1 D2 CEO D3 D4/CF TMS D5 TCK D6 TDI D7 TDO 18 20 19 11 1 R14 4.7K CCLK INIT_N DONE 0.1uF JTAG Header VCC 13 SP_TDI TMS TCK FPGA_TDO TMS TCK 5 6 4 17 SP_TDO XC1801SO20 1 2 3 4 5 6 JTAG1 R15 1 A C1 2 2 1 VCC 2 A Do Not Populate Avnet, Inc. Design Services Copyright 2000 Title Mini-Virtex-E Board - Lead Sheet Size C Date: 5 4 3 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 1 Sheet 2 of 6 5 4 JP4 HEADER 3 3 2 1 AUX+3.3V 1 2 3 +1.8V 14 13 15 16 2 18 17 2 0.1uF NC NC 1 2 9 10 NC NC GND/HS GND/HS GND/HS GND/HS GND/HS GND/HS GND/HS GND/HS 20 19 12 11 1 1 1 2 C28 C29 0.1uF 2 0.1uF 2 0.1uF C17 0.1uF 1 2 1 C27 2 2 C16 0.1uF 2 C26 0.1uF B 1 2 C15 0.1uF 1 C25 C37 + + 2 TANC_47uF 2 TANC_47uF 1 1 2 1 2 0.1uF 1 2 1 TANC_47uF C14 0.1uF C36 + 2 TANC_47uF 1 C24 0.1uF 2 C35 C13 0.1uF 2 1 2 1 C23 1 2 C12 0.1uF 0.1uF + 1 1 1 1 2 1 2 1 2 0.1uF C34 + TANC_47uF C11 0.1uF C22 1 2 C33 2 2 TANC_47uF 0.1uF 0.1uF + TANC_47uF 2 TANC_47uF C21 1 C32 + C10 2 C31 + C20 0.1uF 2 0.1uF 1 2 1 C30 0.1uF 2 C19 0.1uF C9 2 C18 C8 0.1uF 2 1 2 1 0.1uF C 1 C7 0.1uF B 1 C6 1 1 1 Virtex-E Decoupling Caps 0.1 uf per Vccco 47uf per Bank 3.3V C54 C46 + C47 + C48 C49 + 1 1 1 1 1 C53 1 C52 1 C51 1 1 1 C50 + + 0.1uF TANC_47uF TANC_47uF TAND_470uF 2 TANC_47uF 2 TANC_47uF 2 0.1uF 2 0.1uF 2 2 0.1uF 2 0.1uF 2 0.1uF C45 2 0.1uF C44 2 C43 2 0.1uF 1 1 C42 2 0.1uF 2 0.1uF C41 1 1 C40 2 0.1uF 2 2 0.1uF C39 2 C38 1 1 Virtex-E Decoupling Caps 0.1uf per Vccint four 47uF per device one 470uF per device 1 +1.8V TANB_10uF R18 TPS76718QPWP C 270K 10% C2 Do Not Populate 4 8 2 C5 2 OUT OUT FB RST D + 1 TANC_22uF 2 TANC_22uF IN IN EN GND 1 C4 4 C3 2 6 7 5 3 1 + R17 2 VCC 1 1 R16 U4 TAB 1 + 3.3V 3 OUT 1.8V 3.3V Do Not Populate IN GND 1 L4955V3.3 2 D U3 2 5V J3 RAPC712 1 A A Avnet, Inc. Design Services Copyright 2000 Title AVNET, INC. CONFIDENTIAL Mini-Virtex-E Board - Power Size B Date: 5 4 3 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 Sheet 3 1 of 6 3 ADDRESS[0:31] ADDRESS[0:31] CNTL[0:20] 2 OSC 1 DOUT R20 0R0/0805 NOT POPULATED 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 1 ADDRESS0 ADDRESS1 ADDRESS2 ADDRESS3 ADDRESS4 ADDRESS5 ADDRESS6 ADDRESS7 ADDRESS8 ADDRESS9 ADDRESS10 ADDRESS11 ADDRESS12 ADDRESS13 ADDRESS14 ADDRESS15 CNTL[0:20] OSC NOT POPULATED 0R0/0805 R19 1 2 2 4 2 GCK1_FB OSC_FB R21 0R0/0805 NOT POPULATED 2-102977-5 DATA[0:31] DATA0 DATA1 DATA2 DATA3 DATA4 DATA5 DATA6 DATA7 DATA8 DATA9 DATA10 DATA11 DATA12 DATA13 DATA14 DATA15 C DATA[0:31] CNTL[0:20] 2 NOT POPULATED R24 2 2 R25 0R0/0805 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 2-102977-5 DATA1 DATA3 DATA5 DATA7 DATA9 DATA11 DATA13 DATA15 DATA17 DATA19 DATA21 DATA23 DATA25 DATA27 DATA29 DATA31 CNTL12 CNTL14 CNTL16 CNTL18 CNTL20 GCK1 CNTL[0:20] 2 NOT POPULATED 0R0/0805 R22 1 2 1 37 35 33 31 29 27 25 23 21 19 17 15 13 11 9 7 A/D0:0 A/D2:0 A/D0:1 A/D2:1 A/D0:2 A/D2:2 A/D0:3 A/D2:3 A/D0:4 A/D2:4 A/D0:5 A/D2:5 A/D0:6 A/D2:6 A/D0:7 A/D2:7 A/D1:0 A/D3:0 A/D1:1 A/D3:1 A/D1:2 A/D3:2 A/D1:3 A/D3:3 A/D1:4 A/D3:4 A/D1:5 A/D3:5 A/D1:6 A/D3:6 A/D1:7 A/D3:7 CLK:1/Q1 CLK:0/Q0 n/c GND n/c n/c ADDRESS16 ADDRESS17 ADDRESS18 ADDRESS19 ADDRESS20 ADDRESS21 ADDRESS22 ADDRESS23 ADDRESS24 ADDRESS25 ADDRESS26 ADDRESS27 ADDRESS28 ADDRESS29 ADDRESS30 ADDRESS31 5 3 1 D CLK_OUT MICTOR(AMP 2-767004-2) 37 35 33 31 29 27 25 23 21 19 17 15 13 11 9 7 A/D0:0 A/D2:0 A/D0:1 A/D2:1 A/D0:2 A/D2:2 A/D0:3 A/D2:3 A/D0:4 A/D2:4 A/D0:5 A/D2:5 A/D0:6 A/D2:6 A/D0:7 A/D2:7 A/D1:0 A/D3:0 A/D1:1 A/D3:1 A/D1:2 A/D3:2 A/D1:3 A/D3:3 A/D1:4 A/D3:4 A/D1:5 A/D3:5 A/D1:6 A/D3:6 A/D1:7 A/D3:7 CLK:1/Q1 CLK:0/Q0 n/c GND n/c n/c 5 3 1 DATA16 DATA17 DATA18 DATA19 DATA20 DATA21 DATA22 DATA23 DATA24 DATA25 DATA26 DATA27 DATA28 DATA29 DATA30 DATA31 C GCK3 B CLK_IN CLK_OUT CNTL[0:20] R23 0R0/0805 NOT POPULATED CNTL0 CNTL1 CNTL2 CNTL3 CNTL4 CNTL5 CNTL6 CNTL7 CNTL8 CNTL9 CNTL10 CNTL11 CNTL12 CNTL13 CNTL14 CNTL15 0R0/0805 R26 0R0/0805 CLK_OUT_FB 1 1 NOT POPULATED GCK1 GCK3 J5 38 36 34 32 30 28 26 24 22 20 18 16 14 12 10 8 6 4 2 1 NOT POPULATED B JP6 MICTOR(AMP 2-767004-2) 43 42 41 40 39 DATA0 DATA2 DATA4 DATA6 DATA8 DATA10 DATA12 DATA14 DATA16 DATA18 DATA20 DATA22 DATA24 DATA26 DATA28 DATA30 CNTL11 CNTL13 CNTL15 CNTL17 CNTL19 J4 38 36 34 32 30 28 26 24 22 20 18 16 14 12 10 8 6 CLK_IN A J6 38 36 34 32 30 28 26 24 22 20 18 16 14 12 10 8 6 MICTOR(AMP 2-767004-2) A/D0:0 A/D2:0 A/D0:1 A/D2:1 A/D0:2 A/D2:2 A/D0:3 A/D2:3 A/D0:4 A/D2:4 A/D0:5 A/D2:5 A/D0:6 A/D2:6 A/D0:7 A/D2:7 A/D1:0 A/D3:0 A/D1:1 A/D3:1 A/D1:2 A/D3:2 A/D1:3 A/D3:3 A/D1:4 A/D3:4 A/D1:5 A/D3:5 A/D1:6 A/D3:6 A/D1:7 A/D3:7 CLK:1/Q1 CLK:0/Q0 n/c GND n/c n/c 4 2 37 35 33 31 29 27 25 23 21 19 17 15 13 11 9 7 5 3 1 CNTL16 CNTL17 CNTL18 CNTL19 CNTL20 SWITCH8 SWITCH9 RS232RX RS232TX RS232EN_N RS232SD_N TEMP_SCLK TEMP_CE TEMP_SDI TEMP_SDO SWITCH[0:9] DOUT A CLK_OUT Avnet, Inc. Date: 4 3 Copyright 2000 Mini-Virtex-E Board - Connectors Size B 5 Design Services Title 43 42 41 40 39 GND GND GND GND GND D 1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 ADDRESS1 ADDRESS3 ADDRESS5 ADDRESS7 ADDRESS9 ADDRESS11 ADDRESS13 ADDRESS15 ADDRESS17 ADDRESS19 ADDRESS21 ADDRESS23 ADDRESS25 ADDRESS27 ADDRESS29 ADDRESS31 CNTL1 CNTL3 CNTL5 CNTL7 CNTL9 1 43 42 41 40 39 ADDRESS0 ADDRESS2 ADDRESS4 ADDRESS6 ADDRESS8 ADDRESS10 ADDRESS12 ADDRESS14 ADDRESS16 ADDRESS18 ADDRESS20 ADDRESS22 ADDRESS24 ADDRESS26 ADDRESS28 ADDRESS30 CNTL0 CNTL2 CNTL4 CNTL6 CNTL8 CNTL10 JP5 2 GND GND GND GND GND 4 GND GND GND GND GND 5 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 Sheet 4 1 of 6 5 4 3 2 LED7 LED6 LED5 LED4 LED3 LED2 LED1 LED0 LED[0:7] VCC 2 2 2 2 2 2 2 2 D R31 R32 R33 R34 R35 R36 R37 R38 1K 1K 1K 1K 1K 1K 1K 1K 1 10K 1 R27 2 10K 1 R28 2 10K 1 R29 2 10K 1 R30 2 SWITCH[0:9] SWITCH0 D SWITCH1 SWITCH2 1 1 D7 D8 QTLP650C-2 D6 QTLP650C-2 1 1 D5 QTLP650C-2 D4 QTLP650C-2 1 1 D3 QTLP650C-2 D2 QTLP650C-2 1 QTLP650C-2 QTLP650C-2 1 S1 1 2 3 4 5 6 7 8 D9 16 15 14 13 12 11 10 9 SWITCH3 SWITCH4 SWITCH5 SWITCH6 3-435640-9 SWITCH7 SW2 0R0/0805 2 C R40 1 1 2 4 3 7914J-1-000E C55 R42 1 2 1 0.1uF U6 Do Not Populate VCC 4 TXD LEDA 1 R46 OSC/SOCKET LEDC RXD 1206, 1.8R VCC VCC Mode GND 2 2 7 8 SEG1_E 1 0R0/0805 B SEG1_D 1 SEG1_C 1 TFDU6101E C59 1 VCC 2 SEG1_Dp 1 0.1uF 1 RS232SD_N SEG2_E C60 U8 0.1uF C62 1 2 0.1uF ADM3222ARS A C63 2 1 20 19 18 17 16 15 14 13 12 11 0.1uF VCC 5 9 4 8 3 7 2 6 1 747844-6 SEG2_D 1 R50 220 R51 SEG2_G 1 R62 U9 TEMP_CE TEMP_SCLK 1 2 3 4 VDDD VDDA CE SERMODE SCLK SDI GND SDO 0R0/0805 8 7 6 5 SEG2_C 1 SEG2_Dp 1 TEMP_SDI TEMP_SDO SEG2_B 220 R52 220 R54 220 R56 220 R58 2 R48 2 C57 0.1uF 2 2 2 1 R61 220 R64 220 R65 220 R66 1 U7 1 2 3 4 5 6 7 8 9 10 E1 D1 C1 Dp1 E2 D2 G2 C2 Dp2 B2 2 N/C2 N/C1 F1 G1 A1 B1 S1 S2 F2 A2 20 19 18 17 16 15 14 13 12 11 1 1 1 1 2 R53 220 R55 220 R57 220 R59 220 R60 220 R63 2 SEG1_F 2 SEG1_G 2 SEG1_A 2 SEG1_B 2 SEG2_F 2 SEG2_A 220 2 A 2 Avnet, Inc. Design Services Copyright 2000 Title Mini-Virtex-E Board - Switch, LED, OSC DO NOT POPULATE 2 Size B RS232RX Date: 3 1 MAN6141C RS232TX 4 10K 1 B R67 DS1722U 5 R44 2 R45 2 2 220 1 0.1uF 10K 1 10K 1 2 220 1 2 EN SD C1+ VCC V+ GND C1T1OUT C2+ R1IN C2- R1OUT Vn/c T2OUT T1IN R2IN T2IN R2OUT n/c 2 C61 1 1 2 3 4 5 6 7 8 9 10 1 P1 2 RS232EN_N R43 2 C58 4.7uF, TAN + 2 C56 0.1uF R49 1 10K 1 C 6 1 SHDN R41 2 1206, 1.8R 1 1 5 IR_SHDN 10K 1 1 4 IR_RXD R39 2 R47 2 1 3 IR_TXD 10K 1 2 GND 2 ENABLE 2 OUT 2 OSC 5 OSC SWITCH9 8 1 VCC SWITCH8 SW1 1 2 4 3 7914J-1-000E VCC U5 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 Sheet 5 1 of 6 5 4 3 2 1 ADDRESS[0:31] AUX+3.3V ADDRESS0 ADDRESS3 ADDRESS4 ADDRESS7 ADDRESS8 D ADDRESS11 ADDRESS12 ADDRESS15 ADDRESS16 ADDRESS19 ADDRESS20 ADDRESS23 ADDRESS24 ADDRESS27 ADDRESS28 ADDRESS31 DATA0 DATA3 DATA4 DATA7 DATA8 C DATA11 DATA12 DATA15 DATA16 DATA[0:31] DATA19 DATA20 DATA23 DATA24 DATA27 DATA28 DATA31 CNTL0 CNTL3 CNTL4 CNTL7 CNTL8 B CNTL11 CNTL12 CNTL15 CNTL16 CNTL19 CNTL20 CLK_OUT 0R0/0805 2 R69 1 NOT POPULATED P2 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 92 93 94 95 96 97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 136 137 138 139 140 CNTL[0:20] JTAG_TMS JTAG_TDI JTAG_TRS IO GND IO IO GND IO IO +3.3V IO IO GND IO IO GND IO IO GND IO IO +3.3V IO IO GND IO IO GND IO IO GND IO IO +3.3V IO IO GND IO IO GND IO IO GND IO IO +3.3V IO IO GND IO IO GND IO IO GND IO IO +3.3V IO IO GND IO IO GND IO IO GND IO TMS +3.3V TDI TRST +5V IO IO GND IO IO GND IO IO GND IO IO +5V IO IO GND IO IO GND IO IO GND IO IO +5V IO IO GND IO IO GND IO IO GND IO IO +5V IO IO GND IO IO GND IO IO GND IO IO +5V IO IO GND IO IO GND IO IO GND IO IO +5V IO IO GND IO IO GND TDO TCK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 ADDRESS1 ADDRESS2 ADDRESS5 ADDRESS6 ADDRESS9 ADDRESS10 D ADDRESS13 ADDRESS14 ADDRESS17 ADDRESS18 ADDRESS21 ADDRESS22 ADDRESS25 ADDRESS26 ADDRESS29 ADDRESS30 DATA1 DATA2 DATA5 DATA6 DATA9 DATA10 DATA[0:31] C DATA13 DATA14 DATA17 DATA18 DATA21 DATA22 DATA25 DATA26 DATA29 DATA30 CNTL1 CNTL2 CNTL5 CNTL6 CNTL9 CNTL10 B CNTL13 CNTL14 CNTL17 CNTL18 CNTL[0:20] NOT POPULATED R68 0R0/0805 2 1 2 1 CLK_IN CLK_OUT_FB R70 0R0/0805 NOT POPULATED JTAG_TDO JTAG_TCK 5-179010-6 A A Avnet, Inc. Design Services Copyright 2000 Title Mini-Virtex-E Board - Daughter Board Connector Size B Date: 5 4 3 2 Document Number Rev A H394-XLX5-MVE-1002 Tuesday, October 17, 2000 Sheet 6 1 of 6