Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

Electrónica Digital

Prof: Ing. Aníbal Coto Cortés

Segundo Examen Parcial

II Cuatrimestre 2006

Diplomado en Electrónica

P1

P2

P3

Estudiante:

Indicaciones: resuelva la prueba de forma ordenada y legible. No se revisarán las partes que

presenten confusión o desorden. Muestre los pasos que lo conducen a la obtención de una

respuesta, como requisito para que ésta sea válida. Solo se atenderán consultas relativas al examen

en los primeros quince minutos del mismo. Presente este enunciado como portada.

P4

P5

1era Parte. Respuesta corta. 50 min. 10 pts c/u

P6

1-

P7

Dibuje el circuito que convierta el siguiente código Gray en binario natural de 3

bits.

D

0

0

0

0

0

1

1

1

C

0

0

0

1

1

1

0

0

B

0

1

1

1

0

0

0

0

A

1

1

0

0

0

0

0

1

Eq. Decimal

0

1

2

3

4

5

6

7

2- Escriba la tabla de verdad de un convertidor de BCD a un

display de 7 segmentos de cátodo común.

3- Dibuje el circuito de un codificador de prioridad de 4 entradas y 2 salidas.

4- Determine si el siguiente circuito es un flip-flop. Justifique plenamente su

respuesta. En caso de que lo sea, determine cual de las líneas es el SET,

RESET, Q y Q'.

5- Diseñe un contador asíncrono de 4 bits descendente. Calcule la frecuencia

máxima de operación de este contador y compárela con la de un contador

síncrono. Asuma tPff = 45 ns y tPand = 15 ns.

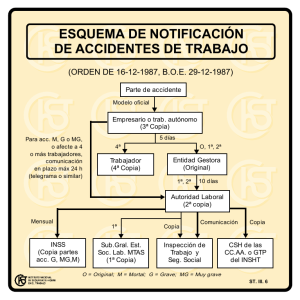

ACC/acc

NE

Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

Electrónica Digital

Prof: Ing. Aníbal Coto Cortés

Primer Examen Parcial

II Cuatrimestre 2006

Diplomado en Electrónica

Estudiante:

Indicaciones: resuelva la prueba de forma ordenada y legible. No se revisarán las partes que

presenten confusión o desorden. Muestre los pasos que lo conducen a la obtención de una

respuesta, como requisito para que ésta sea válida. Solo se atenderán consultas relativas al examen

en los primeros quince minutos del mismo. Presente este enunciado como portada.

2da Parte. Desarrollo. 50 min. 25 pts c/u

6- Se dispone de 4 MUX's normales de 4 entradas y de compuertas lógicas para

implementar un MUX especial de 16 entradas y 2 salidas que cumpla con lo

siguiente:

S3 S2

0 0

0 0

0 0

0 0

0 1

0 1

0 1

0 1

1 0

1 0

1 0

1 0

1 1

1 1

1 1

1 1

S1 S0

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

0 0

0 1

1 0

1 1

OUT1

I0

I1

I2

I3

I4

I5

I6

I7

I8

I9

I10

I11

I12

I13

I14

I15

OUT2

I8

I9

I10

I11

I0

I1

I2

I3

I12

I13

I14

I15

I4

I5

I6

I7

Dibuje el circuito que cumpla con lo anterior.

7-

Diseñe

un

cronómetro

que

cuente

décimas

de

segundo

(1 décima = 1/10 seg) y segundos. Los resultados deben mostrarse en el

formato: SS:D (dos dígitos para los segundos y uno para las décimas)

utilizando displays de 7 segmentos. El sistema debe tener botón de inicio,

pausa y reset. Indique la frecuencia de la señal de reloj del sistema.

ACC/acc

0

0