Luis González Varela

Anuncio

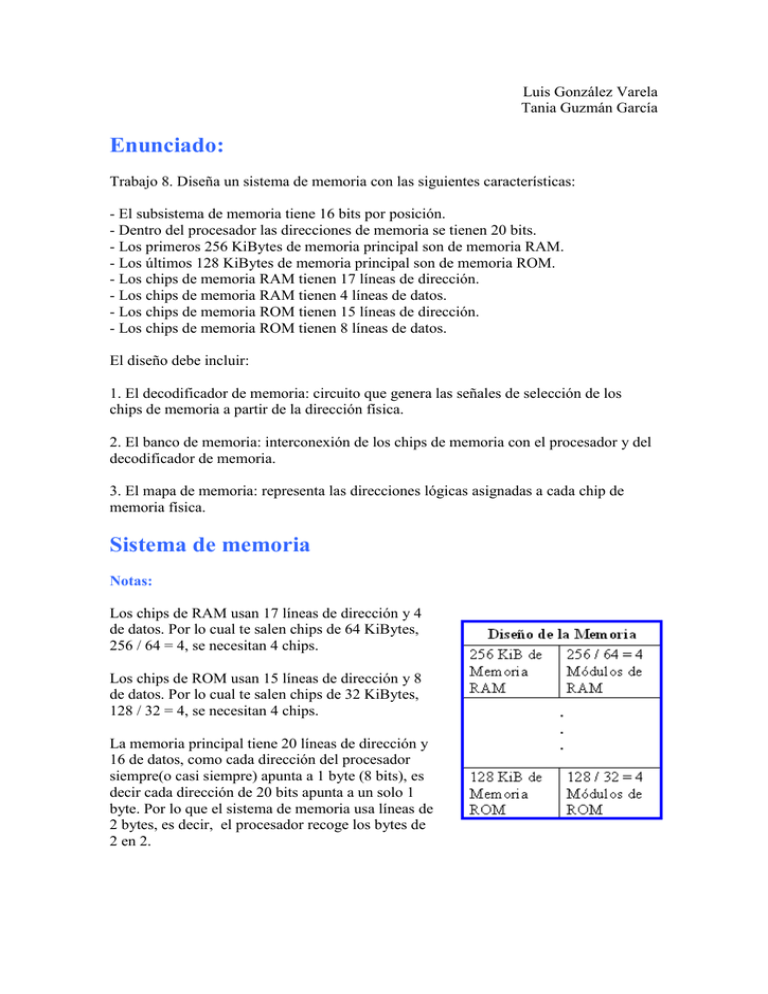

Luis González Varela Tania Guzmán García Enunciado: Trabajo 8. Diseña un sistema de memoria con las siguientes características: - El subsistema de memoria tiene 16 bits por posición. - Dentro del procesador las direcciones de memoria se tienen 20 bits. - Los primeros 256 KiBytes de memoria principal son de memoria RAM. - Los últimos 128 KiBytes de memoria principal son de memoria ROM. - Los chips de memoria RAM tienen 17 líneas de dirección. - Los chips de memoria RAM tienen 4 líneas de datos. - Los chips de memoria ROM tienen 15 líneas de dirección. - Los chips de memoria ROM tienen 8 líneas de datos. El diseño debe incluir: 1. El decodificador de memoria: circuito que genera las señales de selección de los chips de memoria a partir de la dirección física. 2. El banco de memoria: interconexión de los chips de memoria con el procesador y del decodificador de memoria. 3. El mapa de memoria: representa las direcciones lógicas asignadas a cada chip de memoria física. Sistema de memoria Notas: Los chips de RAM usan 17 líneas de dirección y 4 de datos. Por lo cual te salen chips de 64 KiBytes, 256 / 64 = 4, se necesitan 4 chips. Los chips de ROM usan 15 líneas de dirección y 8 de datos. Por lo cual te salen chips de 32 KiBytes, 128 / 32 = 4, se necesitan 4 chips. La memoria principal tiene 20 líneas de dirección y 16 de datos, como cada dirección del procesador siempre(o casi siempre) apunta a 1 byte (8 bits), es decir cada dirección de 20 bits apunta a un solo 1 byte. Por lo que el sistema de memoria usa líneas de 2 bytes, es decir, el procesador recoge los bytes de 2 en 2. ESQUEMA DEL DISEÑO DE LA MEMORIA R/W 4 4 4–7 0–3 RAM 0 RAM 2 12 – 15 4 RAM 3 BUS DE DATOS 19 18 RAM 1 8 – 114 18 ≥1 2 16 17 18 19 15 & ROM 0 ROM 1 0–7 8 8 – 15 8 1 4 19 BUS DE MEMORIA 18 15 ROM 2 0–7 ROM 3 8 – 15 8 8 16