m - Departamento de Arquitectura y Tecnología de Computadores

Anuncio

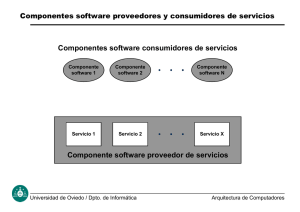

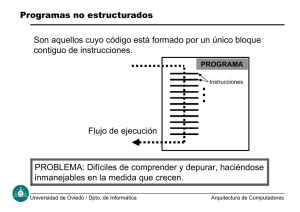

Proc. Superescalares con Planificación dinámica • Arquitectura muy distinta a la de los superescalares con planif. estática. • En estas máquinas superescalares se implementa un algoritmo de planificación o “scheduling” dinámico muy similar de Tomasulo • También emisión dinámica: en tiempo de ejecución • Fases: IF IS EX WB. Para Ld/St en EX se hace EA+MEM • La emisión en IS de todas las instr. de la ventana sólo suele depender de que existan R.S. (o búferes de acceso a memoria) libres y no tiene reglas de emisión. • El grado m suele ser las instrucciones que puede emitir hacia las R.S. • Recordar casi máxima: las técnicas dinámicas acaban imponiéndose a las estáticas en máquinas de propósito general, por compatibilidad del sw. • Compilador no debe influir, en principio (en realidad siempre ayuda). • No obstante: Más complejidad ⇒ más consumo, son peores para sist empotrados. • Se ha llegado casi al límite de ILP (m=4) extraíble dinámicamente y realizable físicamente con la tecnología actual ⇒ no olvidar alternativas estáticas (VLIW) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 27 Repaso de Algoritmo Tomasulo (Planif. dinámica) Caché de instrucciones Del caché de datos Buffers de carga 6 Instrucciones IF EX Registros ETQ (MEM) 5 4 3 2 1 IS IS Buses de operando 3 2 1 Buffers almacenamiento EX (MEM) Bus de operación Al caché de datos WB 3 2 1 Estaciones de reserva ALU INT EX 2 1 MULT OTRAS U.F. Bus Común de Datos (CDB) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 28 Implementación de Superescalares Planif. dinámica Todo similar al Algoritmo de Tomasulo Caché de instrucciones Del caché de datos Muchos más Buffers de carga 6 Instrucciones IF EX Registros Todo similar para instr. FP ETQ (MEM) 5 4 3 2 1 IS IS Buses de operando 3 2 1 Muchos más búferes almacenamiento EX (MEM) Bus de operación Al caché de datos WB Muchas más 2 Estaciones 1 de reserva 3 2 1 ALU INT EX MULT más U.F. INT U.F. FP Buses Comunes de Datos (CDB) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 29 • IF: se buscan m instr (o más). Si no se emiten todas, se quedan en cierto búfer de búsqueda (para nosotros la ventana de instrucciones). - Aquí la ventana rígida no reduce prácticamente las prestaciones (mientras haya R.S. se emiten todas). Muchos superescalares con planif. dinámica la implementan así para simplificar. - En realidad es una ventana de emisión (issue window) en una fase intermedia - Se accede a la BTB. • IS: (generalmente subdivida en varias etapas). Emite todas las m instrucciones mientras haya R.S. - Actualmente casi ningún procesador de propósito general impone reglas o criterios sobre las m instrucciones. Pueden ser de cualquier tipo y balanceo (no existe el concepto de “tubería”). La emisión rígida no tiene mucho sentido aquí. - Se van encolando las instrucciones en las diferentes estaciones de reserva R.S., que se enviarán (dispatch) hacia las U.F., cuando estén todos los operandos. - Luego si nada lo impide se alcanza el límite IPC=IPCideal=m - Si se agotan las R.S. (por ej. muchas instr del mismo tipo seguidas, muchas RAW en cadena, muchos fallos caché), sí habrá bloqueos de emisión. - La complejidad de muchos factores de la fase IS crece con m2 - Se aumenta el número de RS para que soporten la tasa de instrucciones. Nº R.S. debe tener relación con Nº instr. en vuelo (k x m = Nº fases x grado ) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 30 • EX: - Balanceo de U.F. en función del % tipos instr. - Debe ser Nº U.F. > m. - Muchas de ellas pueden estar ociosas. • MEM: - Doble puerto (o doble banco) cada vez más habitual. - El búfer de escritura (últimos Store) más importante. Los Load pueden leer de él sin bajar a caché (muchas dependencias en memoria en CISC). - Los cachés no son bloqueantes (non-blocking caches). Ante fallo de acceso a caché, las U.F. y R.S. siguen trabajando (el número de R.S. y de instrucciones en vuelo es altísimo) y se “oculta la latencia” de acceso a L2. • WB: Nº CDB’s proporcional a m. Además se complica con la especulación (apartado siguiente). > Con esta arquitectura (algor. Tomasulo), el cronograma de proc. encadenado (m=1) es similar al superescalar (m>1), pero con más de todo. Además suponemos que existen recursos abundantes (RS, CDB, puertos, etc.). Diferencias principales: - Se pueden saturar los búferes o RS por existir muchas RAW - Si el número de UF es menor que el número de instrucciones/ciclo de ese tipo, se saturará también las RS. - Fallos cache, de BTB hacen que se vacíen las RS Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 31 Algunos aspectos de las máquinas reales > En realidad se insertan búferes, colas o listas intermedias entre cada una de las fases Ejemplo: Búferes en el Pentium Pro (no se muestran todas las fases ni el superencad.) 6 µops 16 bytes IF 16 bytes por ciclo DEC 3 instr. por ciclo Alineamiento 20 R.S. REN (RAT) y DIS 3 µops por ciclo EX 5 U.F. FP+INT+ MEM WB 3 resultados por ciclo 40 ROB Cuello de Botella: m = 3 µops/ciclo > Nº máximo instr. en vuelo = suma de instrucc. o entradas de todos los búferes. > Difícil ver el cronograma. Se ocultan bloqueos de cualquier tipo, vaciando las colas. > Bloqueo total se produce p.ej. si en un bucle se van acumulando instrucciones hasta que se llena las R.S. completamente. > Las depend. reales RAW y fallos cachés marcan el ritmo de ejecución: se acerca al Data Flow Limit, límite del flujo de datos (recordar grafo de dependencias) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 32 Ejemplo 3: superescalar planif. dinámica Supongamos DLX superescalar con planificación dinámica que busca y emite hasta m=4 instrucciones por ciclo (similar al MIPS R10000). No hay reglas de emisión. - Dos ALU’s enteras EX1, EX2 (también ejecutan los saltos). - Una de carga/almacenamiento (EA+MEM). - Otra de punto flotante simple (ADD/SUB-FP) totalmente segmentada Las fases son IF REN DIS EX WB (IS se divide en REN+DIS). En REN se renombran registros lógicos por físicos (desaparecen WAR, WAW) Desenrollar en un procesador con algoritmo de planificación dinámica no aumenta mucho las prestaciones (al revés, se corre riesgo de que se agoten las R.S.) Calcular: a) Número de CDB enteros y FP para que no haya bloqueos estructurales. b) Renombrar los registros para eliminar falsas dependencias. ¿Qué ocurre con la segunda iteración (registro R1)? c) Dibujar el cronograma, calcular el IPC y el número de ciclos por elemento del vector procesado. d) Hallar el número de R.S. de cada tipo que se necesitan. ¿Qué ocurre si hubiera otras instrucciones con RAW tras la ADDD; ej. MULTD F4, F4, F4)? Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 33 e) ¿Qué ocurre si m=5? ¿Y si la fase IF tiene una ventana de 8 instrucciones con acceso a BTB en todas ellas? f) Calcular la aceleración respecto de la máquina ideal (IPC=5), si el porcentaje de fallos de la BTB es 3% y 5%. Proponer algunos mecanismos de penalidad de fallo de predicción, y calcular la nueva aceleración. g) Analizar el caso de tener en cuenta los accesos caché de datos de 64 bytes/línea. Calcular nº búferes de carga necesarios. h) ¿Qué ocurre si la primera instrucción fuera Loop: LD F0, 8(R1)? (se deja como ejercicio, ahora el bucle no sería paralelizable y habría una dependencia real en la memoria entre un Store de una iteración y un Load de la siguiente) Suponer BTB que siempre acierta. for (i=N ; i>0 ; i--) x[i] = x[i] +s; Loop: LD F0, 0(R1) ADDD F4, F0, F2 SD 0(R1), F4 SUBI R1, R1, 8 BNEZ R1, Loop Dpto. Arquitectura y Tecnología de Computadores. // F2←s ; R1← &x[N] ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 34 1.2. Implementación de Proc. Superencadenados • No complejidad desde el p de v de la arquitectura sino de la tecnología. Grado n. • La misma UF se supersegmenta y vale para n instrucciones (no hay que replicarla). • Problemas: > Se necesitan latches entre las microetapas (registros temporales de cadena) para independizarlas y permitir tener varias instrucciones en la misma etapa. Esto provoca que se alargue el tiempo total de la instruc. y un poco el espacio requerido por el hw. Latches (reg Temp.) τreloj τreloj Superencaden. IF1 Superescalar IF2 τetapa IF ID1 ID2 EX1 EX2 Etc. Diferencia ID EX Etc. > Periodo de reloj a mínimos => surgen problemas con el clock skew: desfases de la señal de reloj en distintas partes del procesador (máximo si es ida y vuelta de una señal). Ejemplo el Pentium 4 tiene dos fases que no hacen nada, sólo amplifican la señal para llevarla o conducirla (fases “Drive”) de un punto a otro del chip. Esto sucederá cada vez más con los superencadenados más “agresivos”. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 35 > Número de ciclos (del reloj acelerado) de bloqueo crece ahora. Idem con las penalidades de fallo de caché, de fallo de predicción de BTB, etc. Ejemplos: Superescalar Load ALU Superencaden. Load ALU Bloqueo (Latencia de acceso a memoria) por dependencia RAW IF IF1 ID EX ME WB IF ID - EX IF2 ID1 ID2 EX1 EX2 M1 M2 IF1 IF2 ID1 ID2 - - - M1 M2 τetapa ME τreloj WB1 WB2 EX1 EX2 M1 Superencaden. Salto Instr predicha 1 Instr predicha 2 Instr predicha 3 Instr predicha 4 Instr predicha 5 Instr correcta IF1 IF2 ID1 ID2 EX1 EX2 IF1 IF2 ID1 ID2 EX1 IF1 IF2 ID1 ID2 IF1 IF2 ID1 IF1 IF2 WB M2 WB1 WB2 Ejemplo: Fallo de BTB: WB1 WB2 ABORTAR: 5 CICLOS DE PENALIDAD τreloj IF1 IF1 IF2 ID1 ID2 EX1 EX2 M1 M2 WB1 WB2 Superescalar Salto Instr predicha 1 Instr predicha 2 Instr correcta IF ID EX IF ID Dpto. Arquitectura y Tecnología de Computadores. IF ME WB ABORTAR: SÓLO 2 CICLOS DE PENALIDAD IF ID EX ME τetapa WB ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 36 • Lo anterior reduce mucho las prestaciones de un superencadenado (si tiene planif dinámica es el problema principal en cuanto a ciclos perdidos). Se intentan reducir al máximo: mayores cachés, algoritmos de predicción más sofisticados, etc. Y se intentan recortar tales penalidades: ej. UltraSPARC III tiene un búfer que guarda las instrucciones siguientes para el caso de predicción de un salto como tomado: si falla la predicción, se recogen del búfer las instrucc. de la rama no tomada, y no se gasta la penalidad de buscarlas (se empieza por la fase ID1 directamente). • En general, las etapas con circuitos secuenciales (IF, MEM, IS) se supersegmentan mucho; mientras que las combinacionales (EX de INT) apenas se supersegmentan. • Conclusión: el CPI de superencadenado es mucho mayor que el de superescalar. Ejemplo: Pentium 4 / Pentium III: Pentium III Pentium 4 Nº fases 11 22 Frecuencia para la misma tecnología 1.5 GHz 2.5 GHz Prestaciones relativas SPEC INT2000 1 (1GHz) 1.26(1.7GHz) 1.45(2GHz) Prestaciones relativas SPEC FP2000 Dpto. Arquitectura y Tecnología de Computadores. 1 (1GHz) P4 / PIII 2 1.667 CPI de P4 es 1.34 mayor 1.85(1.5GHz) 2.22(2GHz) ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 37 Diferencias Superescalares vs VLIW MÁQUINAS SUPERESCALARES Deben decodificar una secuencia de instrucciones, comprobar que son independientes y pueden emitirse a la vez según las reglas de emisión. Organización del código no suele existir. Balanceo de instr. con respecto a UF en tiempo de ejecución (peor, ventana de instr. reducida). Cuello de botella en ID o IS: proporcional a m2 tamaño de los programas es menor. Código generado puede ser compatible con otras máquinas, tanto escalares como superescalares Dpto. Arquitectura y Tecnología de Computadores. MÁQUINAS VLIW Etapas IF e ID van a ser más simples (no hacer comprobación de depcias o criterios). Organización del código y balanceo de instr. con respecto a UF en tiempo de compilación (mejor, ventana de instr. que “ve” el compilador es infinita) La dificultad de ID o IS la resuelve el compilador. tamaño de los programas es mayor (algunos slots quedan vacíos, desenrollado masivo). Código generado no suele ser compatible con otras máquinas (incluso en otras versiones de VLIW tampoco). ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 38 Máquinas Superescalares vs Superpipeline MÁQUINAS SUPERESCALARES Necesitan replicar UF para poder ejecutar varias instr. en el mismo ciclo paralelismo espacial de UF Penalidades y c.bq. en ciclos menores MÁQUINAS SUPERPIPELINES UF de estarán supersegmentadas paralelismo temporal de UF Penalidades o c.bq. en ciclos altísimas (no dejarse engañar por los GHz) latches entre microetapas => ν (superenc.) nunca será n * ν (superescalar) Más problemas con el clock skew • Lo normal es tener combinadas las mejoras de ambas soluciones. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 39 Comparativa prestaciones superescalar-superencadenado • Ciclos que tarda un fragmento de código (saltos “rompen” la ejecución) • N instrucciones, K etapas Encadenado (CPI ideal, 0 c. bq.) K ETAPAS Instr 1 Instr 2 Instr 3 Instr 4 1 2 K IF ID EX M WB IF ID EX M WB IF ID EX M WB Total : K + N –1 ciclos Dpto. Arquitectura y Tecnología de Computadores. WB N-1 ciclos ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 40 Superescalar (CPI ideal, 0 c. bq.) K ETAPAS m m m Instr 1 Instr 2 Instr 3 Instr 4 Instr 5 Instr 6 Instr 7 Instr 8 Instr 9 1 IF IF IF 2 ID ID ID IF IF IF … EX EX EX ID ID ID IF IF IF … M M M EX EX EX ID ID ID K WB WB WB M M M EX EX EX WB WB WB M WB M WB M WB (N-m)/m ciclos Total : K + (N –m)/m = K + N /m - 1ciclos Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 41 SuperPipeline(CPI ideal, 0 c. bq.) K ETAPAS, K*n microetapas 1 Instr 1 Instr 2 Instr 3 Instr 4 Instr 3 IF1 - IF2 IF1 2 K ID1 - ID2 EX1- EX2 M1 - M2 IF2 - ID1 ID2 – EX1 EX2 - M1 IF1 - IF2 ID1 - ID2 EX1- EX2 IF1 IF2 - ID1 ID2 – EX1 IF1 - IF2 ID1 - ID2 WB1-WB2 M2 - WB1 WB2 M1 - M2 WB1-WB2 EX2 - M1 M2 - WB1 WB2 EX1- EX2 M1 - M2 WB1-WB2 (N-1)/n ciclos, N-1 microciclos Total : K + (N –1)/n ciclos Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 42 Aceleración Superescalar y Superpipeline. • Medida de prestaciones en función de lo anterior • Sea m el grado de superescalaridad de nuestra máquina. Entonces la aceleración de un superescalar respecto de un procesador básico será (suponiendo ningún c. bq.): A( m,1) = Tversiónbásica T (1,1) = = TversiónSE T ( m,1) K + N −1 ⎡ N − m⎤ K +⎢ ⎥ ⎢ m ⎥ siendo K el número de etapas de la máquina sin “supersegmentar”, N el número de instrucciones y m el grado SE. • Si llevamos el número de instrucciones a infinito, la máxima aceleración que se K + N −1 mN + m( K − 1) conseguirá será: lim A(m,1) = lim = lim =m N m − N →∞ N →∞ N → ∞ N + m( K − 1) K+ m • Sea n el grado de superpipeline (número de microetapas por etapa). La aceleración respecto a la máquina básica será (K=Nº etapas sin supersegmentar, sup. 0 c. bq.): A(1, n) = Dpto. Arquitectura y Tecnología de Computadores. Tversiónbásica T (1,1) K + N − 1 = = TversiónSP T (1, n) K + N − 1 n ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 43 • Llevando el número de instrucciones al infinito tendremos: K + N −1 nN + n( K − 1) ( 1 , ) A n = = =n lim lim lim N − 1 N → ∞ N + nK − 1 N →∞ N →∞ K+ n • Combinando ambas T(m,n) será los K ciclos de la máquina básica para las primeras m instrucciones y paras las N-m instrucciones restantes iremos terminando a razón de 1 por ciclo de reloj. Por tanto (suponiendo ningún c. bq.): m· n A(m, n) = Tversiónbásica T (1,1) = = TversiónSESP T (1, n) K + N −1 ⇒ lím A(m, n) = m·n ⎡ N − m⎤ N →∞ K+⎢ ⎢ m·n ⎥⎥ • Si m=n=4, y tenemos 1 salto cada 12 instrucciones, que nos rompe el límite, tendremos que la aceleración entre superescalar y superpipeline será ligeramente mayor que 2, ganándole la superescalar a la superpipeline en las mismas condiciones. Pero si K=9 (¡superencadenado con 36 microetapas!), la aceleración de cada frag. es pobre: Fragm. 12 instr. Superescalar m=4 Superencadenado n=4 Comp. K=5 A=16/(5+8/4)=2.29 A=16/(5+11/4)=2.06 10.7% K=9 A=16/(9+8/4)=1.45 A=16/(9+11/4)=1.36 6.8% Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 44 Máquinas reales con ILP (Superescalares, etc.) Intel Pentium Pro (válido para PII, PII en instr enteras). m=3, RISC Core. 2 UF Int, 1 UF FP, 3 UF para acc a mem. 20 R.S. compartidas. ROB (especulación). Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 45 Power PC 620 (Motorola + IBM). - Registros y buses de 64 bits. Superescalar de grado 4, con algor. de Tomasulo y 6 UF(XS0,XS1,MCFXU, LSU, FPU and BPU). R.S. separadas por UF - Similar a DLX con Tomasulo: Etapas IF, ID, IS, EX, CM (especulación) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 46 Alpha 21264 (Digital, ahora COMPAQ) - 80 Registros INT de 64 bits. 72 Reg FP (es como un pequeño caché) - Superescalar de grado m=4 (Los anteriores Alpha eran muy supersegm. y estáticos) - Primero renombran reg. Luego, R.S. (Integer y FP queue) se quedan a la espera de leer operandos. Cuando están disponibles, los leen (etapa posterior, no hay bypass CDB) - Los bancos de registros enteros están duplicados para permitir 4 UF enteros trabajando en paralelo. Se gasta un ciclo de reloj en actualizar ambos bancos. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 47 Microfotografías de procesadores reales con ILP Intel Pentium 4 (2001) Alpha 21264 (1999) • Decode + µcode ocupa mucho • UF (Int+FP) muy poco • Out of Order control+Scheduling: Mucho • Mem control+L1+L2+Trace Cache+System Interf.: casi el 50% del chip • Decode ocupa tan poco que no está puesto. • UF (Int+FP) muy poco. Registros mucho • FP, Integer Map and queues (R.S.) grande • Mem control+BIU+Bus Interf. Unit+ Instr. Fetch +L1(64KB datos, 64KB instr):casi 60% Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 48 1.3 Paralelismo de instrucciones disponible: programas enteros, científicos y multimedia. • Explotar más ILP => ¿ límite ILP del software? && ¿Máquina realizable? • Realidad: grado m superescalaridad no ha aumentado en los últimos años. • ¿Tiene sentido implementar más grado de superescalaridad? • ¿Qué factores limitan el paralelismo extraíble? o Balanceo de instrucciones. Evitarlo, añadiendo más UF (en el caso extremo m UF de cada tipo para que no haya problemas), aumenta el tamaño del chip considerablemente, mientras se desperdician transistores, cuando un proceso no sólo utiliza ciertas UF (p ej si es programa INT no usará las UF FP). o Dependencias reales (recordar límite del flujo de datos data-flow limit). El algor. Tomasulo las oculta al principio, pero las colas se llenan ⇒ bloqueo o Acierto en la predicción de saltos. BTB cada vez más sofisticada, compleja y grande. o Accesos a memoria de datos (caché): Ancho de banda altísimo, latencia de acceso no decrece casi, muchas dependencias en memoria... Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 49 Estudio de ILP según recursos tmcatv FP doduc fpppp ILP ideal ILP realizable li INT espresso gcc 0 20 40 60 80 ILP ideal (con simulador usando una traza) • ventana de infinitas instrucciones • predicción saltos perfecta • Toda dirección Ld/ST conocida • Infinitas UF • Duración toda UF=1 ciclo • Cache perfecto 100 % acierto • Infinita planificación estática y dinámica • SOLO LIMITA LAS PRESTACIONES EL DATA FLOW LIMIT 100 120 140 160 Instr emitidas/ciclo ILP para procesadores “realizables” • • • • • • • • Ventana de 64 instrucciones Predicción saltos: BTB 1K entradas Toda dirección Ld/ST comparada dinámicam. Emite hasta 64 inst/ciclo sin reglas emisión Duración toda UF=1 ciclo Cache perfecto 100 % acierto (64 puertos) Planificación dinámica: 64 etiq FP y 64 INT DEMASIADO OPTIMISTA... o Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 50 • Recordar: o Programas INT más algorítmicos (más RAW entre instrucciones). o Programas FP: bucles de vectores, procesador vectorial podría explotar ese ILP. • Pero dificultad hardware proporcional a m2: (muchos factores de la fase IS) • Número de comparadores en ID o IS para la detección de dependencias: (HP 8600 tiene pensados 7000 comparadores en sus R.S.) o Cálculo teórico: ALU1 Rd1, Rfa1, Rfb1 ALU2 Rd2, Rfa2, Rfb2 ... ALUm Rdm, Rfam, Rfbm Comparar Rd1 con Rfa2, Rfb2, ... Rfam, Rfbm, es decir 2(m-1) comparaciones Comparar Rd2 con Rfa3, Rfb3, ... Rfam, Rfbm, es decir 2(m-2) comparaciones. etc. j =m i =m−1 2 2 ( m − j ) = 2 i = m − m , crece orden cuadrático. ∑ Total Nº comp.= ∑ j =1 i =1 Idem Tomasulo: número CDB’s × número R.S. ; (ambos son proporcionales a m) Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 51 • Número de bypasses (en máquinas sin planificación dinámica, VRm2=m2), INTa → INTa INTa → INTb INTb → INTa INTb → INTb IF ID EX-INTa ME WB IF ID EX-INTb ME WB IF ID EX-INTa ME WB IF ID EX-INTb ME WB IF ID EX-INTa ME WB IF ID EX-INTb ME WB IF ID EX-INTa ME WB IF ID EX-INTb ME WB o El acceso a caché y detección dependencias en memoria se convierte en cuello de botella. • Para m alto la complejidad del superescalar lo hace inabordable actualmente. (por esto el VLIW es la otra alternativa que no debe olvidarse). • Por otro lado están otras técnicas: o Procesador consistente en una superRAM con “pequeña” unidad de ejecución. o Superespeculación : intentar adivinar la dirección de acceso a memoria antes de tener el valor del registro índice, etc. o Otra idea: VLIW con “code morphing” (traducción dinámica de otros ISA’s). o Computación reconfigurable: para programas con mucho ILP, se puede reconfigurar (FPGA) una parte del micro para que se “adapte” al programa Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 52 Simultaneous Multithreading, SMT - Un procesador ejecuta a la vez varios hilos. - Sólo replica los registros y el estado. - Intenta aprovechar los recursos (UF que están ociosas para un hilo), ejecutando otro hilo. - Con algoritmo de Tomasulo, y renombrando registros de forma que los dos hilos tienen registros físicos siempre diferentes, aunque se ejecutan en las mismas UF. - Caché instr. debe buscar dos trazas - Importante para que las prestaciones suban: balanceo de hilos (gestión del S.O.). - Pentium 4 HT (Hyper-Threading: nombre comercial) - NOTA: Procesador Dual y Programas paralelos: Tema 3, ASP2. Dpto. Arquitectura y Tecnología de Computadores. ASP2: TEMA 1: Arquitecturas encadenadas avanzadas: pág 53