DMA y Discos

Anuncio

DMA y Discos

Marı́a Elena Buemi

15 de junio 2010

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

1 / 27

Transferencias entre Módulos

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

2 / 27

DMA según Wikipedia

1

El acceso directo a memoria (DMA, del inglés Direct Memory Access)

permite acceso a la memoria para leer o escribir sin que CPU

intervenga.

2

Muchos sistemas hardware utilizan DMA, incluyendo controladores de

unidades de disco, tarjetas gráficas y tarjetas de sonido.

3

DMA es una caracterı́stica esencial en todos los ordenadores

modernos, ya que permite a dispositivos de diferentes velocidades

comunicarse sin someter a la CPU a una carga masiva de

interrupciones.

4

Una transferencia DMA consiste principalmente en copiar un bloque

de memoria de un dispositivo a otro.

5

En lugar de que la CPU inicie la transferencia, la transferencia se lleva

a cabo por el controlador DMA.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

3 / 27

Ejemplo, Wikipedia

1

Mover un bloque de memoria desde una memoria externa a una

interna más rápida

2

Qué Dispositivo se ocupa?

3

DMA

4

Consecuencia?

5

CPU puede hacer otras tareas.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

4 / 27

Ejemplo, Wikipedia

1

Por qué DMA?

2

Aumenta el rendimiento de aplicaciones que necesiten muchos

recursos.

3

Qué se necesita del Sistema, ya que no usa CPU?

4

Se necesitan las lı́neas del sistema de interconexión(System Bus)

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

5 / 27

Módulo DMA(Stallings)

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

6 / 27

Funciones de DMA Stallings

DMA es capaz de imitar al CPU, y efectivamente, toma el control del

sistema.

Para qué? Para hacer transferencias de datos - lectura o escritura - con la

memoria por el sistema de bus.

Cuando el procesador envı́a una petición de Lectura o Escritura, envı́a al

DMA la siguiente información:

1

Read o Write lı́neas entre CPU y DMA

2

Datos comunica la dirección del dispositivo de I/O, Posición en

Memoria, cantidad de Palabras.

3

Registro de dirección guarda la dirección de Memoria.

4

Qué se necesita del Sistema, ya que no usa CPU?

5

El sistema de bus.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

7 / 27

Ejercicio 1

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

8 / 27

Protocolo entre DMA y Dispositivo E/S

A continuación se describe el protocolo entre el controlador de DMA y un

dispositivo de E/S para realizar transferencias de datos usando el I/O Bus.

1. El controlador DMA pone en el bus de direcciones el identificador del dispositivo con el que

desea iniciar la comunicación y levanta la señal de Request, de RD o WR, según corresponda

y baja la lı́nea de M/IO.

2. El controlador del dispositivo detecta la señal de Request y compara su propio identificador

con el contenido del bus de direcciones.

3. Si coincide el identificador y el dispositivo se encuentra listo, el controlador del dispositivo

levanta la señal de Ready.

4. El controlador DMA detecta la señal de Ready. En el caso de tratarse de una escritura, el

controlador DMA pone el dato a escribir junto con su posición de memoria en los buses

correspondientes. Por otro lado, en el caso de una lectura, el controlador de DMA pone la

dirección del dato deseado.

5. El controlador DMA baja la señal de Request.

6. De tratarse de una escritura, el controlador del dispositivo ordena grabar el dato, o en el

caso de una lectura pone el dato en el bus. Luego, baja la señal de Ready.

7. Si se trata de una lectura el DMAC lee el dato del bus de datos.

8. En ambos casos, lectura y escritura, el DMAC retira las lı́neas y baja la señal de RD o WR

según corresponda.

9. Si es una lectura, cuando el DMAC baja la señal de RD la controladora del dispositivo quita

el dato del bus de datos.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

9 / 27

Protocolo entre DMA y Memoria

Equivalente al que hay entre DMA y Dispositivo.

Cambia el valor de la lı́nea M/IO y no se coloca en el bus el indentificador

del dispositivo.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

10 / 27

Registros de DMA mapeados a Memoria

La Placa de Captura de video tiene su espacio de direcciones mapeado

amemoria en las direcciones FE00 a FF00. por simplicidad se supone que

es una pantalla de video. El identificador de este dispositivo es 0x005F.(lo

usaremos más adelante)

El controlador de DMA posee los siguientes registros también mapeados a

memoria en las direcciones indicadas:

DEVICE (0xFFA0): identificador del dispositivo.

DEVICE ADDRESS (0xFFA1): dirección de memoria (en el espacio de

direccionamiento del dispositivo) que se desea leer/escribir.

MEM ADDRESS (0xFFA2): dirección de memoria (en el espacio de

direccionamiento de la memoria principal) que se desea leer/escribir.

SIZE (0xFFA3): cantidad de datos a transferir.

STATUS (0xFFA4):

si bit 0 contiene 1 indica que ya se han cargado todos los datos

necesarios, y se puede iniciar la transmisión.

el bit 1 contiene un 1 en caso de escritura, y un 0 en caso contrario.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

11 / 27

Comportamiento del controlador de DMA

Es el siguiente:

cuando el bit 0 de STATUS contiene un 1 significa que se puede comenzar

la transferencia. Si el bit 1 de STATUS es un 1 entonces será de IO a

Memoria, si es 0 sera de Memoria a IO. Serán transferidos la cantidad de

palabras que indique SIZE, de la dirección indicada por MEM ADDRESS a

DEVICE ADDRESS o viceversa.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

12 / 27

Primitivas para obtener/liberar el bus:

requestBus() : Solicita el bus para realizar cualquier transferencia.

releaseBus() : Libera el bus una vez que se termino de utilizar.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

13 / 27

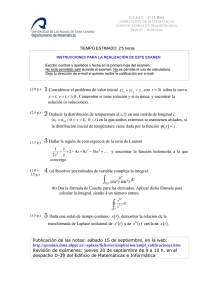

Primitivas para leer/escribir valores en las señales:

señal(es)

Request

Ready

RD

RW

M/IO

bus de datos

bus de direcciones

Marı́a Elena Buemi

()

primitivas

setRequest(x), getRequest()

setReady(x),getReady()

setRead(x),getRead()

setWrite(x),getWrite()

setMemoryIO(x),getMemoryIO()

setData(x),getData()

setAddress(x),getAddress()

DMA y Discos

15 de junio 2010

14 / 27

Qué hace cada primitiva

setRequest(x): Setea la señal de Request con el valor de x(x en 1

ó 0)

getRequest(): Devuelve el valor de Request

setReady(x): Setea la señal de Ready con el valor de x(x en 1 ó 0)

getReady(): Devuelve el valor de Ready

setRead(x): Setea la señal de RD con el valor de x(x en 1 ó 0)

getRead(): Devuelve el valor de RD

setWrite(x): Setea la señal de RW con el valor de x(x en 1 ó 0)

getWrite(): Devuelve el valor de RW

setMemoryIO(x): Setea la señal de M/IO con el valor de x(x en 1 ó

0)

getMemoryIO(): Devuelve el valor de M/IO

setData(x): Escribe x en el bus de datos

getData(): Lee el bus de datos

setAddress(x): Escribe x en el bus de direcciones

getAddress(): Lee el bus de direcciones

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

15 / 27

a) Escribir el seudo-codigo que realiza el controlador de

DMA

MIENTRAS (true){ SI STATUS Tiene bit 0 en 1 ENTONCES{ SI

STATUS tiene bit 1 en 1 ENTONCES {

1.Si se solicita transferir del I/O a Memoria

1.1 Leer del dispositivo al DMA

1.2 Escribir del DMA a la Memoria

1.3 actualiza registros

Sino 2. Si en cambio se solicita Transferir de Memoria a Dispositivo

2.1 Lee de Memoria al DMA

2.2 Escribe de DMA a Dispositivo

3.3 actualiza registros

FinSi FINSI} FINSI} FINMIENTRAS} }

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

16 / 27

a)1.1. Tranferir de I/O a Memoria: Leer del dispositivo a

DMA

while(true) {

if(STATUS AND [10...0] =/= 0 ) {

if( STATUS AND [010...0] =/= 0 ) {

//comentario: IO a Memoria

while( SIZE > 0 ) {

requestBus()

setMemoryIO(0)

setRead(1)

setWrite(0)

setAddress(DEVICE)

setRequest(1)

wait while( getReady() = 0 )

setAddress(DEVICE ADDRESS)

setRequest(0)

wait while( getReady() = 1 )

tempDato < − getData()

setRead(0)

releaseBus()

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

17 / 27

a)1.2 Tranferir de I/O a Memoria: Escribir de DMA a

Memoria

requestBus()

setMemoryIO(1)

setRead(0)

setWrite(1)

setRequest(1)

wait while(getReady() = 0)

setAddress(MEM ADDRESS)

setData(tempDato)

setRequest(0)

wait while(getReady() = 1)

setWrite(0)

setMemoryIO(0)

releaseBus()

MEM ADDRESS <- MEM ADDRESS + 1

DEVICE ADDRESS <- DEVICE ADDRESS + 1

SIZE <- SIZE - 1

}

STATUS <- STATUS AND [01...1]

}

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

18 / 27

a)2.1Tranferir de Memoria a I/O: Leer de Memoria a DMA

else {

//comentario: IO a Memoria

while( SIZE > 0 ) {

requestBus()

setMemoryIO(1)

setRead(1)

setWrite(0)

setRequest(1)

wait while( getReady() = 0 )

setAddress(MEM ADDRESS)

setRequest(0)

while( getReady() = 1 )

tempDato < − getData()

setMemoryIO(0)

setRead(0)

releaseBus()

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

19 / 27

a)2.2Memoria a I/O: Escribir de DMA a I/O

requestBus()

setMemoryIO(0)

setRead(0)

setWrite(1)

setAddress(DEVICE)

setRequest(1)

while(getReady() = 0)

setAddress(DEVICE ADDRESS)

setData(tempDato)

setRequest(0)

while(getReady() = 1)

setWrite(0)

setMemoryIO(0)

releaseBus()

MEM ADDRESS <- MEM ADDRESS + 1

DEVICE ADDRESS <- DEVICE ADDRESS + 1

SIZE <- SIZE - 1

}

STATUS <- STATUS AND [01...1]

}

enviarInterrupcion()

}

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

20 / 27

b)Escribir rutina de interrupción

La Placa de Captura de video tiene su espacio de direcciones mapeado

amemoria en las direcciones FE00 a FF00. por simplicidad se supone que

es una pantalla de video. El identificador de este dispositivo es 0x005F.

Suponga que existe un proceso que muestra en la pantalla los cuadros de

video capturados por la placa.

Este proceso posee una rutina que escribe en la memoria principal el

cuadro capturado.

La placa capturadora genera una interrupción, cada vez que se captura un

cuadro.

Realizar el seudo-código de la rutina que atiende la interrupción de la

placa.

(El rango de memoria AB00 a AC00 esta reservado para guardar la pantalla

capturada en memoria principal)

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

21 / 27

b) Rutina

rutina:

ciclo:

fin:

.....

.....

MOV R1, 0xAB00

MOV R2, 0xFE00

MOV R0, 0x0100

MOV [R1], [R2]

ADD R1, 1

ADD R2, 1

SUB R0, 1

CMP R0, 0

JE fin

JMP ciclo

.....

.....

RETI

Marı́a Elena Buemi

()

copia el ppio del rango de memoria en R1

DMA y Discos

15 de junio 2010

22 / 27

c) Escribir rutina usando el controlador de DMA

rutina:

Marı́a Elena Buemi

()

.....

.....

MOV [DEVICE], 0x005F

MOV [DEVICE ADDRESS], 0x0000

MOV [MEM ADDRESS], 0xAB00

MOV [SIZE], 0x0100

OR [STATUS], 0x8000

.....

.....

RETI

DMA y Discos

15 de junio 2010

23 / 27

Ejercicio 2: Discos

A continuación se presentan algunos parámetros caracterı́sticos de un

disco rı́gido.

Cantidad de Bytes por Sector : |Sectorbytes | Bytes

Cantidad de Platos o Cantidad de Cabezas : |Cabezas|

Cantidad de Pistas por Plato o Cantidad de Cilindros : |Cilindros|

Cantidad de Sectores por Pista : |Sectorespista |

Tiempo entre Pistas adyacentes : |Tadyasentes | Seg

Tiempo promedio entre Pistas : |Tpromedio | Seg

Latencia : |Tlatencia | Seg

Capacidad del Buffer : |Buffer | Mb

Velocidad de Rotacion : |Discorotacion | RPM

Velocidad de Transferencia de la Interfaz : |Interfazvelocidad | Mb/Seg

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

24 / 27

Se pide:

1

Calcular los siguientes valores caracterı́sticos a partir de los

parámetros presentados.

1

2

3

4

5

Cantidad de Sectores totales.

Capacidad máxima en Mbytes.

Tiempo de lectura de un sector.

Tiempo de transferencia de un sector.

Tiempo de transferencia de n sectores consecutivos sobre una misma

pista.

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

25 / 27

Resolución- ambos ej. D. González Márquez

1

|Sectorestotales | = |Cabezas| ∗ |Cilindros| ∗ |Sectorespista |

2

|Capacidadtotal | = |Sectorestotales | ∗ |Sectorbytes |

3

|TLectura.Sector | = 60/(|Discorotacion | ∗ |Sectorespista |)

4

|TTransferencia.Sector | =

|TLectura.Sector | + |Sectorbytes |/(220 ∗ |Interfazvelocidad |)

5

|TTransferencia.Sectores.Unica.Pista (n)| =

n ∗ |TTransferencia.Sector | + (n − 1)|Tlatencia |

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

26 / 27

Bibliografı́a

Computer Organization and Architecture: Designing for

Performance,8/E William Stallings.

ISBN-10: 0136073735. ISBN-13: 9780136073734 Publisher: Prentice

Hall. Copyright: 2010

Null, Linda. The essentials of computer organization and architecture

/ Linda Null, Julia Lobur. p. cm. ISBN 0-7637-0444-X

Marı́a Elena Buemi

()

DMA y Discos

15 de junio 2010

27 / 27