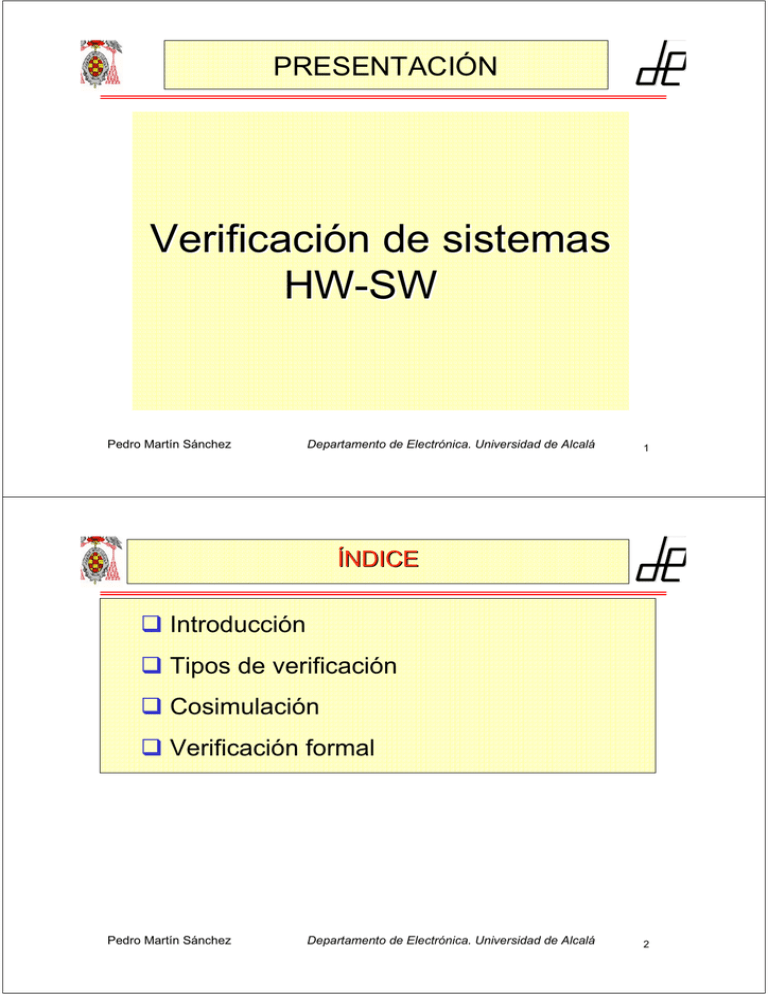

Verificación de sistemas HW-SW

Anuncio

PRESENTACIÓN Verificación de sistemas HW-SW Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 1 ÍNDICE Introducción Tipos de verificación Cosimulación Verificación formal Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 2 Introducción Definiciones ¾ La verificación es el proceso que permite determinar si un sistema funciona de acuerdo con las especificaciones. 9 Asegura que el diseño cumple las especificaciones funcionales y temporales para cada nivel de abstracción. ¾ Se aplica después de cualquier etapa de integración, transformación o refinamiento. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 3 Introducción Definiciones SINTESIS DEL SOFTWARE Particionado HW-SW Especificación software de alto nivel SINTESIS DEL HARDWARE Especificación hardware de alto nivel Integración y verificación Compilador Compilador Código en lenguaje de alto nivel Descripción hardware sintetizable Integración y verificación Compilador Sintetizador Código HW sintetizado Código objeto Integración y verificación Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 4 Tipos de verificación Simulación ¾ Se utilizan modelos matemáticos de los componentes del sistema. ¾ El resultado de la simulación es función del modelo y de los vectores de test (estímulos) introducidos al mismo. ¾ Se realiza en cualquier nivel de abstracción ¾ Valido para simulaciones funcionales y temporales ¾ Tipos de simuladores para sistemas digitales: 9 Basados en HDLs: dirigidos por eventos y basados en ciclo. 9 Basados en esquemas: a nivel de sistema o a nivel de puertas. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 5 Tipos de verificación Simulación ¾ Simulación dirigida por eventos: 9 Evento: cambio en el valor lógico de un nodo y el instante de tiempo en el que se produce. 9 Sólo considera los nodos activos (con eventos): 9 Utiliza una “rueda de tiempo” para gestionar las relaciones entre los componentes: • Lista de todos los eventos no procesados todavía y ordenados en el tiempo Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 6 Tipos de verificación Simulación 1 1 0 0 a c D=2 1 1 1 e D=1 b 0 0 3 4 6 1 d 0 5 e(6)=1 e(4)=0 b(1)=1 d(5)=1 d(5)=1 Pedro Martín Sánchez c(3)=0 d(5)=1 d(5)=1 Departamento de Electrónica. Universidad de Alcalá 7 Tipos de verificación Simulación ¾ Simulación basada en ciclo: 9 Tiene en cuenta que la mayoría de los sistemas digitales son síncronos. 9 Sólo se evalúa en los flancos de la señal de reloj. 9 Es más rápida que la conducida por eventos pero más inexacta: no detecta glitches. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 8 Tipos de verificación Verificación formal ¾ Demostración matemática de que: 9 Una especificación cumple una serie de propiedades: chequeo del modelo 9 Dos descripciones a diferentes niveles de abstracción son equivalentes: chequeo de equivalencias. La más utilizada. ¾ Verifica la funcionalidad sin vectores de test. ¾ Simulación vs verificación formal: 9 El grado de confianza en la simulación depende de los vectores de test seleccionados. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 9 Tipos de verificación Análisis temporal estático ¾ Análisis topológico del circuito que extrae las propiedades temporales y su impacto en el retardo ¾ No precisa de vectores de test ¾ Entradas: netlist, modelos del librerías de celdas y restricciones (periodo de reloj, skew, tiempos de setup y hold....) ¾ Salidas: retardo a través de la lógica combinacional. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 10 Tipos de verificación Emulación y prototipado ¾ Emulación: funcional 9 Mapea el diseño en los componentes HW (generalmente sobre FPGAS) del emulador y analiza la respuesta a estímulos que pueden proceder del entorno físico. ¾ Prototipado: funcional 9 Se construye una implementación HW del diseño. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 11 Cosimulación Definiciones ¾ La cosimulación se define como la simulación de sistemas HWSW de forma conjunta. 9 La sincronización deber ser fiable para que interactúen como lo harían en el diseño final. ¾ Figuras de mérito: exactitud y rendimiento: 9 Exactitud:definida por la complejidad de los modelos y el número de estímulos. 9 Rendimiento: tiempo bajo test. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 12 Cosimulación Problema ¾ Problema: 9 ¿cómo simular componentes HW-SW a la vez? ¾ Dificultades: 9 Se utilizan diferentes plataformas para la simulación 9 El SW se simula a mayor velocidad que el HW: problema con la sincronización. ¾ Aproximaciones: se utiliza un simulador HW para simular un modelo HDL del procesador junto con el modelo HDL del HW. 9 Diferentes resultados en función del modelo del procesador. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 13 Cosimulación Aproximaciones ¾ Modelo del procesador a nivel de puertas. Simulador de VHDL Modelo a nivel de puertas (VHDL) Simulador de VHDL Modelo del HW (VHDL) Software 9 Demasiado lenta debido a la complejidad del modelo 9 Se trata de la alternativa más exacta. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 14 Cosimulación Aproximaciones ¾ Modelo funcional-bus del procesador: Simulador de VHDL Modelo funcionalbus (VHDL) Simulador de VHDL Programa ejecutandose en el host Modelo del HW (VHDL) SW ejecutado por un modelo 9 El modelo HW del procesador sólo contempla la interfaz 9 El SW se ejecuta sobre un modelo de simulación del procesador 9 Es más rápido pero menos exacto que el anterior. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 15 Cosimulación Aproximaciones ¾ Modelo ISA del procesador: Programa ejecutandose en el host Modelo (C) Simulador de VHDL Modelo del HW (VHDL) Software 9 No existe modelo HW del procesador. El SW se ejecuta sobre el modelo. 9 La exactitud de la simulación depende de la interface (tiempos) 9 Alternativa más rápida. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 16 Cosimulación Aproximaciones ¾ Modelo basado en traslación. Programa ejecutandose en el host Simulador de VHDL Software compilado en el código nativo del procesador Modelo del HW (VHDL) 9 No existe modelo HW del procesador. La ejecución del SW proporciona la información de la interfaz necesaria para la cosimulacion. 9 Alternativa más rápida cuya exactitud depende de la información de la interfaz. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 17 Cosimulación Acoplo entre dominios ¾ En las aproximaciones donde el SW se simula ejecutándolo en el host, este debe interactuar con el simulador HW. ¾ Problemas: 9 Exactitud de la información temporal proporcionada por la interfaz. 9 Acoplo de los dos dominios con la sincronización necesaria. ¾ Se emplean fundamentalmente dos esquemas de sincronización: 9 El modo maestro-esclavo y el modo distribuido. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 18 Cosimulación Modo maestro-esclavo ¾ El entorno de cosimulación necesita un simulador maestro y uno o más esclavos. ¾ Los simuladores esclavos se invoca utilizando técnicas como llamadas a procedimientos. ¾ La mayoría de los simuladores proporcionan un modo básico para invocar funciones en C . 9 Por ejemplo, desde VHDL utilizando atributos permite que partes del código se puedan representar en otros lenguajes. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 19 Cosimulación Modo maestro-esclavo ¾ Limitación importante: el módulo esclavo no puede trabajar concurrentemente con el maestro 9 En el caso de cosimulación C-VHDL implica que el módulo en C no puede mantener el estado interno entre dos llamadas. 9 El caso de sistemas dominados por control el problema se acentúa ¾ Conclusión: el programa en C deber estructurado para solventar las limitaciones anteriores. 9 Estructuración en funciones. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 20 Cosimulación Modo distribuido ¾ El modelo distribuido se basa en un protocolo de comunicación en red, el cual se usa como un bus software. ¾ Cada simulador se comunica con el bus de cosimulación a través de llamadas a procedimientos ¾ Para una especificación C-VHDL, esta estrategia permite mantener el código C en su formato original. ¾ Además el simulador VHDL y el programa en C pueden correr de forma concurrente. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 21 Cosimulación Sistemas heterogéneos:otro enfoque Parte electrónica (SDL) Parte mecánica (Matlab) Cosimulación 1 Partición HW/SW Software (C) Hardware (VHDL) Cosimulación 2 Software Código binario Hardware Modelo C (Puertas) Cosimulación 3 C PROTOTIPO Mecánica Memoria Pedro Martín Sánchez ASIC Departamento de Electrónica. Universidad de Alcalá 22 Verificación formal Introducción ¾ La verificación formal supera la simulación cuando es capaz de demostrar: 9 El cumplimiento de ciertas propiedades en un circuito 9 Que dos circuitos son equivalentes ¾ ....... sin utilizar estímulos. ¾ En la actualidad complementa pero no reemplaza a la simulación. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 23 Verificación formal Introducción ¾ Concepto: 9 Se puede demostrar con ecuaciones y sin estímulos que los dos circuitos son equivalentes. 9 Cobertura completa:equivalente a una simulación exhaustiva f = ab(c+d) = abc + abd = g a b c f = ab(c+d) d a b c a b d Pedro Martín Sánchez g = abc+abd Departamento de Electrónica. Universidad de Alcalá 24 Verificación formal Tipos ¾ Tipos de verificación formal: Verificación formal Chequeo de propiedades Chequeo de equivalencias Secuencial Pedro Martín Sánchez Combinacional Departamento de Electrónica. Universidad de Alcalá 25 Verificación formal Tipos ¾ Otro criterio: especificación o implementación: 9 Verificación de la especificación: • Chequeo de propiedades a niveles de abstracción altos.P.e. Chequear bloqueos en protocolos. 9 Verificación de la implementación: • Chequear modelos a bajo nivel para comprobar si implementa el modelo de alto nivel correctamente o satisface algunas propiedades relativas a la implementación.P.e. Chequear si un algoritmo DSP procesa completamente todas las muestras. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 26 Verificación formal Chequeo de equivalencias ¾ Tipos: Behavioral desc. RTL netlist Gate level netlist Trans. netlist Layout Behavioral desc. RTL netlist Gate level netlist Trans. netlist Layout ¾ Los mejores resultados se obtienen si: 9 Los modelos son similares. 9 Se comparan modelos más detallados. Pedro Martín Sánchez Departamento de Electrónica. Universidad de Alcalá 27