- Ninguna Categoria

design, implementation and evaluation of an auxiliary energy

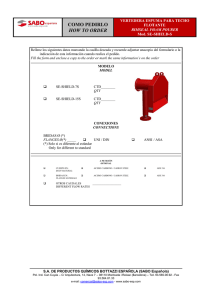

Anuncio