Sistemas en un Chip (SoC)

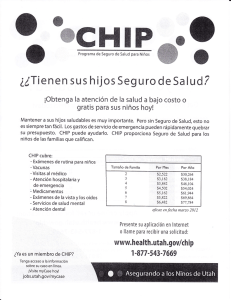

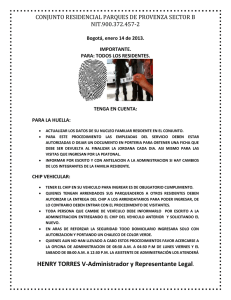

Anuncio

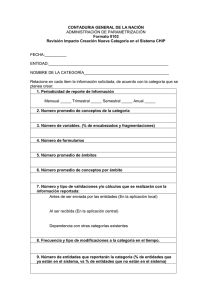

E.T.S. de Ingenieros de Telecomunicación Diseño de Sistemas en Chip (SoC) Sistemas en un Chip (SoC) Tema 1: Migrando hacia SoCs 9Evolución de las tecnologías 9Evolución de las metodologías 9Reutilización de diseños ETSIT Diseño de sistemas en chip (SoC), 4º - Roberto Sarmiento Reutilizar- la clave en el diseño de SoC Reutilizar diseños es la manera más conveniente de aumentar la productividad El uso de VCs (IPs) facilita la reutilización de los diseños, pero tiene que existir una metodología de reutilización para aprovechar todas sus ventajas Cuando un ingeniero realiza una misma (o similar) tarea la productividad aumenta en el segundo paso No sucede si otro ingeniero realiza la tarea realizada anteriormente por un compañero ¿por qué? – – – – So Falta de motivación al no tener que inventar nada Falta de una documentación y de procesos estándares Acceso limitado a lo que se ha hecho previamente Adaptar un diseño es más difícil que empezar de nuevo C Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento ®«Roberto Sarmiento Rodríguez» 1 E.T.S. de Ingenieros de Telecomunicación Diseño de Sistemas en Chip (SoC) Guía general para reutilizar diseños Deben seguirse ciertas consideraciones para hacer un diseño reutilizable: Diseño síncrono: – Debe usarse únicamente una metodología de diseño síncrono – Todos los VCs (IPs) deben tener un interfaz síncrono – Solo las memorias, FIFOs, etc. pueden incluir lógica asíncrona, pero todo el interfaz debe ser síncrono – ... Memorias y diseños de señales mixtas So C – Hasta 60% del área son memorias y menos del 5% son circuitos analógicos – Las memorias deben incluir filas y columnas redundantes. Deben estar colocadas en los extremos del chip. – Los circuitos analógicos típicos son PLL, DACs, ADCs, sensores de temperatura, etc. También deben estar colocados en los extremos del chip ya que son sensibles al ruido Buses en el chip – Son muy importantes para la metodología SoC Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento Guía general para reutilizar diseños (y 2) Distribución del reloj – La metodología de distribución del reloj debe ser muy robusta – Controlar el clock skew es fundamental – Si existen varios dominios de reloj evitar metaestabilidad y usar métodos de sincronización en las interfaces Señales de clear y reset – Hay que documentar extensivamente todas las formas posibles de reset – Todos los resets deben ser síncronos Diseño físico – – – – Floor plan Síntesis Timing Inputs/outputs Desarrollar modelos – – – – Modelo de comportamiento Modelo funcional que permita verificación a nivel de sistema Modelo funcional para timing Modelo de diseño físico So C Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento ®«Roberto Sarmiento Rodríguez» 2 E.T.S. de Ingenieros de Telecomunicación Diseño de Sistemas en Chip (SoC) Reutilización: La clave en el diseño SoC Modelos de reutilización ic Specif Virtual Component Hard / Reuse ive Adapt Soft / s rdnes IP Ha Core Reuse So Predictable, Preverified Core Functions Source Reuse Personal Reuse Functional Starting Points for Block Design Designer-Specific Reuse Practices Documented Spec. Feedback for Update Adequate testbench: Executable Spec. Qualification : RTL Linting, Coverage Analyzer Block Design : Spec and Constraint Who's original designer ? ADD TDD Socketized Functions for Plug & Play Integration Decision-Making: Qualified IP ? Standard Compliant ? (VSI, etc.,) Core Protocol (OCP, Washbone, etc.,) Interface-Based TestBench C PBD BBD Opportunistic IP Reuse Planned IP Reuse Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento Integration-Centric Approach Issue IP-Centric Create IP Can be modified in all Apps Apps. What IP do I have ? Integration-Centric Can be reused /wo change What IP do I need ? Market View IP for any market Key market to serve Design Flow Make IP like ASIC Cell Lib Create system for target market Design Usage Flexible and Re-verifiable Product To product requirement Adaptation Time-To-Market Flexible IP Can be Change easily So C Plug into integration platform To product domain Solid IP NO need to Change, PnP ! Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento ®«Roberto Sarmiento Rodríguez» 3 E.T.S. de Ingenieros de Telecomunicación Diseño de Sistemas en Chip (SoC) Integración de sistemas 1. Centrar el diseño en una familia concreta de aplicaciones Decisión de negocio, análisis de un mercado concreto, productos derivados y posible convergencia de líneas de productos. 2. Identificar los IP que se requieran en cada aplicación IPs internos Adquiridos o disponibles en el mercado 3. Desarrollar un entorno virtual de diseño So Adaptado a la aplicación y que permita identificar los IPs necesarios, … Extender las guías de diseño a la autoría e integración de IPs 4. Generar los IPs correspondientes 5. 6. 7. Determinar las múltiples implementaciones requeridas Preverificar, identificar las interfaces: estándares y propias Hacer la caracterización en silicio Prueba en FPGAs C Demostrar y documentar el nuevo entorno de aplicación Optimizar las guías y los procesos de realización e integración Diseminar la documentación en la empresa Diseño de Sistemas en Chip (SoC), 5º - Roberto Sarmiento ®«Roberto Sarmiento Rodríguez» 4