Primer Parcial 2013

Anuncio

Página 1 de 2

Primer Examen Parcial

Sistemas con Microprocesadores

octubre de 2013

Instrucciones

•

En este exámen parcial, que consta de 3 ejercicios, podrá emplear todo material de consulta que

considere necesario.

•

En cada ejercicio se indica el tiempo estimado para resolverlo y el puntaje que otorga el mismo.

•

Las hojas que no estén caratuladas en la forma indicada por la cátedra no serán tenidas en cuenta.

•

No se permitirá intercambiar ni prestar ningún tipo de elemento entre los estudiantes.

•

La buena presentación, ortografía y redacción serán tenidas en cuenta para la calificación final.

•

El tiempo de duración del parcial es de 1 hora y 50 minutos.

Ejercicios

1) Multiplicación BCD x 2 (50%, 35’). Se desea multiplicar un número BCD por dos. El resultado debe

expresarse como un número BCD. La cifra más significativa del número a multiplicar por dos es siempre 0

El número se almacena a partir de la dirección “NUM” y el resultado también.

La cantidad de bytes que contiene el número se almacena a partir de la dirección LONG.

Ejemplo:

Antes de la ejecución del programa:

LONG:

NUM:

Después de la ejecución:

$05

$03 $24 $55 $98 $92

NUM:

$06 $49 $11 $97 $84

Se pide:

a) (5%) ¿Por qué el problema exige que la cifra más significativa del número a multiplicar por dos es

siempre 0?

b) (5%) ¿Cómo escribiría, para cumplir con la especificación de este problema, un número cuya

cantidad de cifras sea par y su última cifra difiera de cero? Por ejemplo el número BCD $35 $41 $01.

c) (10%) Diseñe el algoritmo para resolver el problema, dibujándolo como un diagrama de flujo de

mediano detalle.

d) (15%) Escriba el programa para resolver el problema, acompañado de un diagrama de flujo

detallado. No se permite emplear subrutinas.

e) (15%) Escriba una rutina para multiplicar por dos, un número BCD de dos cifras al que apunta HX.

Tenga en cuenta de que esta rutina podría haber sido empleada para resolver el problema más general

de múltiples cifras. La rutina no debe modificar el acumulador A.

•

Elija a su juicio la manera más conveniente de pasar los parámetros entre el programa convocante y

la subrutina. Justifique su decisión (no olvide que debe considerar cómo pasará la rutina sus

resultados al programa convocante).

o

o

o

o

Por registros (ya sea dirección y/o datos).

Por lugar fijo en memoria.

Datos en el stack.

Direcciones en el stack.

f) (10%) Escriba nuevamente su solución al punto anterior empleando la rutina que ha diseñado.

2) SRC-1: nueva instrucción (20%, 20’). Se decide cambiar la instrucción ADD – vista en clase – para

que incluya la posibilidad de realizar una operación de desplazamiento al segundo operando antes de realizar la suma. A continuación se describe la modificación en RTL abstracta:

add (:= op= 12) R[ra] R[rb] + shift{R[rc]}

donde

(c3<0> = 0) shift := shift left

(c3<0> = 1) shift := no shift

El ALU no posee la capacidad de realizar desplazamientos. Se pide:

Primer Examen Parcial

•

Página 2 de 2

Describir las RTL concretas para esta instrucción en el SRC-1.

3) SRC-1: camino de datos (30%, 30’). Para lograr una ejecución más rápida se decide modificar el

camino de datos, agregando un shift register (SR) como se muestra en la figura 3.1 (este SR es

combinacional, por lo cual no requiere un pulso de reloj).

a) (8%) Incorpore el SR en el lugar que más convenga (desde el punto de vista de la rapidez) en el

circuito del RSC-1. Para este fin no hace falta dibujarlo sino solo ponerlo como una caja negra a la que

ingresan 0, 32 bits y salen 32 bits y Q.

b) (3%) Elija y justifique una de las siguientes dos opciones de conexión para la salida “horizontal” Q del

SR.

i)

Conectarlo al Carry, C (suponga C como un Flip Flop Preexistente).

ii) No realizar ninguna conexión con esta salida.

c) (8%) Describa las RTL concretas para esta instrucción en la máquina modificada.

d) (3%) Cuánto más rápida es esta instrucción con respecto a la instrucción que desarrolló en la

pregunta anterior (punto 2).

e) (8%) Escriba la/s instrucción/es necesarias para realizar la operación Shift left de un operando fuente,

guardando el resultado en un operando destino. Presente dos alternativas de solución.

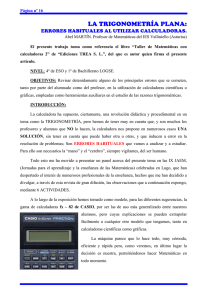

b1

Q

b0

0

…

1

0

1

c3<0>

SEL1

S1

0

c3<0>

SEL0

S0

Fig. 3.1: Shift register combinacional formado por 32 selectores, de los que se muestran solo dos.

¡Éxito!

E. D. Cohen