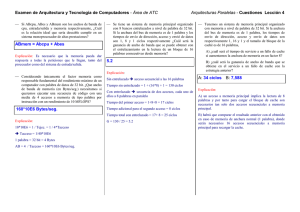

Planificación de tareas considerando la contención en la jerarquía

Anuncio