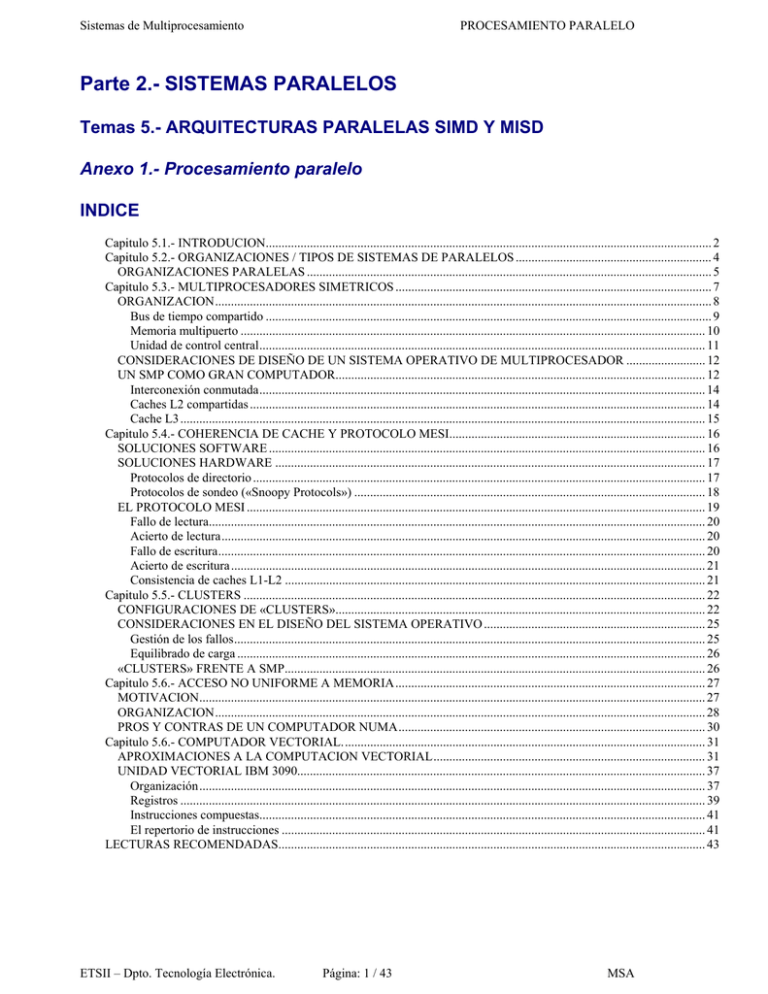

Anexo 1. - Departamento de Tecnología Electrónica

Anuncio