TEMA 1 EL MICROPROCESADOR MC68000

Anuncio

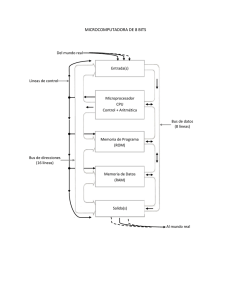

TEMA 1 EL MICROPROCESADOR MC68000 1 Indice 1. INTRODUCCIÓN..................................................................................................................3 2. DESCRIPCIÓN INTERNA Y ORGANIZACIÓN DE DATOS........................................... 4 2.1 Tamaño de los operandos................................................................................................ 4 2.2 Descripción interna..........................................................................................................4 2.2.1 Registros de datos D0-D7.............................................................................................4 2.2.2 Registros de direcciones. A0-A6............................................................................. 5 2.2.3 Registro de pila (SP)................................................................................................ 6 2.2.4 Contador de programa (PC)..................................................................................... 6 2.2.5 Registro de estado.................................................................................................... 6 2.2.6 Registro de códigos de condición. CCR.................................................................. 7 2.3 Organización de datos en memoria..................................................................................8 3. FORMATO DE LAS INSTRUCCIONES............................................................................. 9 4. MODOS DE DIRECCIONAMIENTO................................................................................ 13 4.1 Direccionamiento implícito........................................................................................... 14 4.2 Direccionamiento inmediato..........................................................................................14 4.3 Modos de registro directo.............................................................................................. 15 4.3.1 Registro de datos directo........................................................................................15 4.3.2 Registro de direcciones directo.............................................................................. 15 4.4 Modos de direccionamiento de memoria.......................................................................16 4.4.1 Registro de direcciones indirecto...........................................................................16 4.4.2 Registro de direcciones indirecto con postincremento.......................................... 17 4.4.3 Registro de direcciones indirecto con predecremento........................................... 17 4.4.4 Registro de direcciones indirecto con desplazamiento.......................................... 18 4.4.5 Registro de direcciones indirecto con índice......................................................... 19 4.4.6 Direccionamiento absoluto.................................................................................... 20 4.4.6.1 Dirección absoluta corta.................................................................................20 4.4.6.2 Dirección absoluta larga.................................................................................21 4.5 Modos de direccionamiento relativos............................................................................22 4.5.1 Contador de programa con desplazamiento........................................................... 22 4.5.2 Contador de programa con índice.......................................................................... 23 4.6 Las instrucciones y sus modos de direccionamiento..................................................... 24 5. EL CONJUNTO DE INSTRUCCIONES DEL MC68000.................................................. 26 ................................................................................................................................................. 26 6. DESCRIPCIÓN FUNCIONAL EXTERNA........................................................................ 27 6.1 Bus de datos (D0-D15).................................................................................................. 27 6.2 Bus de direcciones (A1-A23)........................................................................................ 27 6.3 Control del bus asíncrono(/AS, R/#W,/UDS,/LDS,/DTACK)...................................... 28 6.3.1 Ciclo de lectura...................................................................................................... 29 6.3.2 Ciclo de escritura................................................................................................... 31 6.3.3 Conexión de chips de memoria al MC68000 ........................................................34 6.4 Control de arbitraje del bus........................................................................................... 35 6.5 Control de interrupciones.............................................................................................. 35 6.6 Control del sistema........................................................................................................ 36 6.6.1 Reintento del ciclo de bus...................................................................................... 37 6.6.2 Doble error de bus..................................................................................................38 6.7 Control de periféricos síncronos....................................................................................39 6.7.1 Operación de transferencia de datos...................................................................... 39 2 6.8 Estado del procesador.................................................................................................... 40 7. PROCESOS DE EXCEPCIÓN............................................................................................ 40 7.1 Vectores de Interrupción................................................................................................41 7.3 Tipos de excepción........................................................................................................ 44 7.3.1 Excepciones internas..............................................................................................44 7.3.2 Excepciones externas ............................................................................................ 46 1. INTRODUCCIÓN El microprocesador MC68000 de Motorola dispone de un bus de direcciones de 23 líneas (constituyen la dirección física), A23-1, y un bus de datos de 16 bits, D15-0, con los que se pueden direccionar o seleccionar 8 Megapalabras de memoria. Aunque externamente sólo se disponen de 23 líneas, internamente, las direcciones utilizan 24 bits (dirección lógica), existiendo el bit A0 que no aparece en las líneas del bus de direcciones como tal. El bit A0, externamente, se desdobla en dos líneas denominadas /UDS y /LDS. Estas líneas activas en bajo, permiten seleccionar el byte alto y el byte bajo de la palabra escogida por las líneas de direcciones A23-1. De esta forma cuando /UDS=0 y /LDS=1, se selecciona el byte alto (el de mayor peso de la palabra indicada por A23-1), si /UDS=1 y /LDS=0, se selecciona el byte bajo de la palabra y si /UDS=/LDS=0, se selecciona la palabra completa. Por todo esto se puede decir que, el conjunto A23-0, identifica la dirección de uno de los dos bytes contenidos en la palabra identificada por A23-1 . En modo byte, si se accede a una dirección par, se accede al byte más significativo (/UDS activo), y si la dirección es impar, se accede al byte menos significativo (/LDS activo). En modo palabra, (/UDS y /LDS activos) se acceden a la palabra completa, y la dirección debe ser un número par. Según desde el punto de vista desde el que se mire, este microprocesador puede direccionar 8 Mega palabras o 16 Megabytes. A31 A23-A1 A23 A1 A0 & /UDS & /LDS palabra DB15-DB0 MC68000 3 2. DESCRIPCIÓN INTERNA Y ORGANIZACIÓN DE DATOS 2.1 Tamaño de los operandos Los tamaños de los operandos se definen de la forma siguiente: un byte es igual a 8 bits, una palabra es igual a 16 bits, y una palabra larga es igual a 32 bits. El tamaño del operando usado por cada instrucción se encuentra explícitamente codificado en el código de operación de la instrucción o implícitamente codificado por el tipo de instrucción. Todas las instrucciones explícitas manejan byte, palabra o palabra larga. Las instrucciones implícitas solo soportan un subconjunto de estos tres tamaños. COD_OPERACION.N donde N es B para byte,W para word y L para long word 2.2 Descripción interna En la siguiente figura se observa la estructura interna del MC68000 desde el punto de vista del programador. Estase compone de 8 registros de datos (32 bits), 8 registros de direcciones( 32 bits), el contador de programa( 32 bits) y el registro de estado (16 bits). El MC68000 puede trabajar en uno de los modos siguientes: modo supervisor y modo usuario. En el modo supervisor el programador tiene control total sobre los registros e instrucciones del microprocesador. En el modo usuario existen ciertas restricciones de funcionamiento que se irán detallando progresivamente. D0 31 D1 D2 D3 D4 D5 D6 D7 A0 A1 A2 A3 A4 A5 A6 16 15 8 7 0 PALABRA LARGA PALABRA REGISTROS DE DATOS BYTE PALABRA LARGA PALABRA REGISTROS DE DIRECCIONES A7 PUNTERO DE PILA DE SUPERVISOR PUNTERO DE PILA DEL USUARIO CONTADOR DE PROGRAMA BYTE SISTEMA CCR REG. ESTADO 2.2.1 Registros de datos D0-D7 Existen 8 registros de datos de 32 bits cada uno, cuyo fin es el de contener datos u operandos y que funcionan como si fueran 8 acumuladores. La información que se almacena en dichos 4 registros puede ser manejada como byte, palabra o palabra larga. D0 31 D1 D2 D3 D4 D5 D6 D7 16 15 8 7 0 PALABRA LARGA PALABRA REGISTROS DE DATOS BYTE Esto es, cada registro de datos puede considerarse como: - Una palabra larga de 32 bits - Dos palabras de 16 bits cada una denominadas palabra alta y baja. Cuando se trabaja en modo palabra, sólo se accede a la palabra baja, siendo en este caso, el bit 15, el bit de signo de la palabra. Alguna instrucción que tenga como destino la palabra baja de un registro de datos, deja intacta la palabra alta del mismo. - Cuatro bytes. En modo byte, se accede al byte bajo de la palabra baja, dejando intactos los restantes bits. En este caso el bit de signo es el bit 7 del registro de datos. Las operaciones sobre los registros de datos, por tanto, sólo afectan a los bits correspondientes al tamaño de la instrucción. 2.2.2 Registros de direcciones. A0-A6 Con estos 7 registros de 32 bits, el microprocesador puede acceder a diferentes posiciones de memoria. A diferencia de los registros de datos, estos no pueden trabajar en modo byte, sólo admiten el modo palabra o el de palabra larga. Si el contenido de alguno de estos registros actúa como operando fuente de una instrucción, esta puede manejar el tamaño palabra o palabra larga. Si una instrucción utiliza, como operando destino, uno de estos registros, puede manejar, también, los tamaños palabra y palabra larga, pero, en cualquier caso, siempre se modificarían los 32 bits del registro destino. Si una instrucción introduce un operando de tamaño palabra en un registro de dirección, este se depositaría en la palabra baja del mismo pero, la palabra alta, se modificaría por el efecto de la extensión de signo que produce el copiado del bit de signo de la palabra baja (bit 15), en todos los bits de la palabra alta. A0 A1 A2 A3 A4 A5 A6 PALABRA LARGA PALABRA REGISTROS DE DIRECCIONES Los registros de direcciones se utilizan para acceder a las diferentes posiciones de memoria, por tanto su valor debe estar de acuerdo con las diferentes longitudes de los datos. Si, por ejemplo, se accede a una posición de memoria en busca de un dato de tamaño byte, el registro de direcciones puede contener cualquier valor (par o impar), pero si se accede a 5 posiciones de memoria en busca de operandos de tamaño palabra o de palabra larga, el contenido de estos registros debe ser par. Las operaciones con los registros de direcciones no afectan al Registro de Códigos de Condición (CCR) del Registro de Estado (SR). 2.2.3 Registro de pila (SP) El registro de direcciones A7 actúa como puntero de pila y, en realidad, está formado por dos registros denominados: - USP : Puntero de Pila del Usuario – SSP : Puntero de Pila del Supervisor A7 PUNTERO DE PILA DE SUPERVISOR PUNTERO DE PILA DEL USUARIO Como se mencionó con anterioridad, el MC68000 puede trabajar en modo usuario (forma habitual), y en modo supervisor si se dan ciertas condiciones internas. Cada modo de funcionamiento dispone de su propia pila y los registros USP o SSP, son sus punteros de pila. Es decir, en modo usuario, cualquier referencia a memoria que se realice con el registro A7 accede a aquella zona de la memoria en la que se encuentra la pila de usuario, mientras que, cualquier referencia de A7 con el microprocesador en modo supervisor, accederá a la zona donde está la pila del supervisor. En cualquier caso, los punteros siempren direccionan el último dato almacenado en la pila, se decrementan cuando se guardan datos en ella (escritura) y se incrementan cuando se sacan (lectura). 2.2.4 Contador de programa (PC) Es un registro de 32 bits de los cuales sólo se usan los 24 bits menos significativos y contiene la dirección de memoria donde se encuentra la siguiente instrucción a ejecutar. 2.2.5 Registro de estado Consta de 2 bytes: byte de sistema y byte de usuario (también llamado registro de códigos de condición o, simplemente, CCR). 6 2.2.6 Registro de códigos de condición. CCR Está formado por 8 bits, de los cuales los tres bits más significativos son siempre ceros. Los cinco restantes reflejan el resultado de las operaciones realizadas. X: Extensión. Se trata de un bit de acarreo para operaciones de múltiple precisión y rotación. Por lo general toma el mismo valor que C pero hay instrucciones que modifican C y no afectan a X. N: Signo. Se pone a 1 cuando el resultado de una operación es negativo y a 0 cuando el resultado es positivo o, dicho de otra forma, este bit es igual que el bit más significativo del resultado. Z: Cero. Se pone a 1 cuando el resultado de una operación es cero y, a 0, si el resultado es distinto de cero. V: Desbordamiento. Se pone a 1 cuando hay un desbordamiento en las operaciones de números con signo. C: Acarreo. Se pone a 1 cuando se genera acarreo en las operaciones aritméticas de suma y resta y las operaciones de desplazamiento. Byte del Sistema. Es el byte más significativo del registro de estado SR. Su contenido se puede leer y modificarse cuando se trabaja en modo supervisor. Sólo se emplean 5 de sus 8 bits. T: Modo traza. Cuando este bit vale 1, el MC68000 ejecuta el programa paso a paso. Sólo se puede poner a 1 en modo supervisor 7 S: Supervisor. Indica el modo de funcionamiento del microprocesador. Si S vale 1, indica que se está en modo supervisor y, si vale 0, en modo usuario. I2-I0: Máscara de interrupciones. Con estos 3 bits se puede fijar el nivel de prioridad de una interrupción. Los dispositivos externos pueden solicitar una interrupción del programa con un nivel de prioridad comprendido desde el 7 (máxima prioridad) hasta el 1 (mínima prioridad). Por norma general, la máscara fija el nivel mínimo de la interrupción que será atendida. Si el nivel solicitado es mayor que el fijado en la máscara, la interrupción se atiende, en caso contrario, no, a excepción del nivel 7, que se corresponde con una interrupción no enmascarable. Si la máscara I2-I0 fija el nivel 7 y se produce una transición en las entradas de interrupción que genere una petición final de nivel 7, el MC68000 aceptará dicha petición. 2.3 Organización de datos en memoria Los bytes son direccionados individualmente, siendo el byte de mayor peso de la palabra el que tiene la dirección par, mientras que el byte menos significativo es el que tiene la dirección impar (big-endian). Los datos de tipo palabra se encuentran ocupando las direcciones pares, por lo que si una palabra tiene la dirección n, la siguiente tiene la dirección n+2. Las palabras largas ocupan dos palabras en memoria. Si una palabra larga tiene la dirección base n, la siguiente palabra tiene la n+4. De la palabra larga la palabra más significativa es la que ocupa la posición n, mientras que le menos, ocupa la posición n+1. MODOS DE DIRECCIONAMIENTO 8 3. FORMATO DE LAS INSTRUCCIONES Una instrucción máquina del MC68000 puede contener entre una y cinco palabras. La primera palabra se denomina PALABRA DE OPERACIÓN (OW), que siempre contiene un campo que especifica el código de operación (OPCODE), un campo que especifica el tamaño del operando, si este es necesario, y un campo denominado DIRECCIÓN EFECTIVA (EA) que indica la localización de los operandos. El resto de las palabras que componen la instrucción se denominan palabras de extensión (EW) y contienen información complementaria de los modos de direccionamiento de la instrucción. El campo EA (6 bits) de la OW, en caso de que aparezca, está formado por dos subcampos de tres bits cada uno, llamados modo y registro, que codifican el modo de direccionamiento que se emplea para localizar el operando. 9 MODO DE DIRECCIONAMIENTO Directo de registro de datos Directo de registro de direcciones Indirecto de registro Indirecto de registro con postincremento Indirecto de registro con predecremento Indirecto de registro con desplazamiento Indirecto de registro indexado con desplazamiento Absoluto corto Absoluto largo Relativo a PC con desplazamiento Relativo a PC indexado con desplazamiento Inmediato MODO 000 001 010 011 100 101 110 111 111 111 111 111 EA REGISTRO Número de registro (Dn) Número de registro (An) Número de registro (An) Número de registro (An) Número de registro (An) Número de registro (An) Número de registro (An) 000 001 010 011 100 El formato de la OW varía según el número de operandos de la instrucción y se tienen: A) B) C) D) Instrucciones sin operandos Instrucciones con un operando Instrucciones con dos operandos Instrucciones de bifurcación A) INSTRUCCIONES SIN OPERANDOS Son las menos comunes y su sintaxis en ensamblador es: Codigo_op Donde Codigo_op representa el Mnemónico del código de operación en ensamblador. Ejemplos: RTS, NOP, RTE El formato de la palabra de operación (OW) consta sólo del campo código de operación. 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OW codigo de operacion 10 B) INSTRUCCIONES CON UN OPERANDO Su sintaxis en ensamblador es: Codigo_op.tam op_destino Donde Codigo_op representa el mnemónico del código de operación en ensamblador, tam el tamaño del operando (que puede ser B para byte, W para word o palabra, o L para long word o palabra larga) y op_destino representa el único operando de la instrucción. Existen dos formatos de OW para este tipo de instrucciones: 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EA destino OW codigo_op tamaño modo registro a) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OW codigo de operacion registro b) El tipo (a) consta de tres campos: - código de operación( 8 bits) - tamaño ( 2 bits ) - EA del operando destino. Ejemplos del tipo (a) CLR.L D0, NOT.B D1, NEG.W D2 El tipo (b) es usado por instrucciones que sólo emplean un registro de datos como operando, por lo que sólo consta de dos campos: - código de operación (13 bits) registro (3 bits) Ejemplos del tipo (b) SWAP D3, EXT D1 C) INSTRUCCIONES CON DOS OPERANDOS Son las más comunes. Su sintaxis es Codigo_op.tam op_fuente , op_destino 11 Donde codigo_op representa el mnemotécnico del código de operanción en ensamblador, tam el tamaño de los operandos (B,W,L) op_fuente representa el operando fuente, y op_destino, representa el operando destino. Existen tres formato de OW para este tipo de instrucciones Tipo (a) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 EA destino EA fuente OW cod_op tamaño registro modo modo registro La instrucción usa dos campos de dirección efectiva para especificar la posición del operando fuente y el destino. Sólo la instrucción MOVE utiliza este formato Tipo (b) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 cod_op registro modo_op EA fuente/destino OW modo registro Este es el formato más común para instrucciones de dos operandos en las que, uno de ellos, está especificado por un registro y, el otro, por una dirección efectiva. Existe un campo modo_op que codifica el tamaño de los operandos y el destino de los mismos Campo MODO_OP Byte 000 100 Palabra 001 101 Doble pal. 010 110 Operación <registro>OP<EA>registro <EA>OP<registro> EA Ejemplos: ADD.B (A1),D0 ; CMP.W 8(A3),D0 ; ... Tipo (c) 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OW cod_op registro modo_op registro Este formato lo emplean aquellas instrucciones en las que los operandos se encuentran en los registros internos. El campo modo_op especifica el tamaño de la operación y el tipo de registros que intervienen (datos o direcciones) Dentro de las instrucciones de dos operandos existen unos formatos especiales, llamados formatos CORTOS como son los asociados a las instrucciones ADDQ (suma rápida), SUBQ (resta rápida) y MOVEQ( movimiento rápido). En estas instrucciones, uno de los operandos 12 es una pequeña constante que se codifica en la propia OW. Existen dos formatos cortos. 15 14 13 12 11 10 OW cod_op cod_op 8 registro 15 14 13 12 11 10 OW 9 dato 7 6 5 4 1 0 4 3 2 1 EA destino 0 0 9 3 2 dato 8 7 6 modo_op 5 modo registro El primero corresponde a la instrucción MOVEQ (8 bits para codificar el dato) y el segundo para ADDQ y SUBQ (tres bits, del 1 al 8) D) INSTRUCCIONES DE BIFURCACIÓN CONDICIONAL Las instrucciones de bifurcación condicional, Bcc, tienen un formato especial, ya que la OW incluye un campo de desplazamiento y un campo de códigos de condición 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OW cod_op condicion desplazamiento 4. MODOS DE DIRECCIONAMIENTO El 68000 dispone de 14 modos de direccionamiento, siendo uno de los más potentes entre los microprocesadores de 16 bits y que dan lugar a una mayor simplicidad en la realización de los programas. Los modos de direccionamiento pueden clasificarse en: - Direccionamiento implícito - Direccinamiento inmediato - Modos de registro directo - Modos de direccionamiento de memoria - Direccionamiento absoluto - Modos de direccionamiento relativos Como veremos a continuación, alguno de estos grupos se subdividen en varios modos. Los modos de direccionamiento asociados a las diferentes instrucciones vienen codificados en el propio código de instrucción en el campo dirección efectiva (EA). La siguiente figura representa el formato general de una palabra de instrucción con una única dirección efectiva. Esta se encuentra constituida por dos campos de tres bits. Un campo se denomina modo y, el otro, registro. Los valores del campo modo especifican los diferentes tipos de direccionamiento, mientras que los valores del campo registro, seleccionan un 13 registro en concreto. La dirección efectiva requiere, en muchas ocasiones, de información adicional que se suministra en las palabras de extensión o EW que siguen al código de operación. 4.1 Direccionamiento implícito Este modo de direccionamiento está reservado para un determinado número de instrucciones que no necesitan operandos para su ejecución. Para ellas sólo basta el código de operación. Un ejemplo lo constituye la instrucción de STOP que pone, al microprocesador, en estado de parada. En general, las instrucciones que tienen este tipo de direccionamiento pueden hacer uso de los registros del sistema (PC, punteros de pila y registro de estado) sin mencionarlos en el campo operando. 4.2 Direccionamiento inmediato Es el modo de direccionamiento más sencillo y en el que, el dato referenciado por la instrucción, se encuentra en una de las palabras de extensión que siguen a la OW de la propia instrucción, es decir, el operando forma parte de la instrucción. Este modo de direccionamiento se utiliza, principalmente, para inicializar los contenidos de los registros (datos o direcciones) a un valor determinado o para incrementar su valor. El formato general de una instrucción que use este modo es: CODOPER.N #DATO,OPERANDO_DESTINO Ejemplo: MOVE.W #$1234,D0 Esta instrucción carga la constante hexadecimal $1234 en los 16 bits menos significativos del registro D0. Como ya se ha mencionado, este modo de direccionamiento requiere de una o dos palabras de extensión, dependiendo del tamaño del dato. Si el tamaño especificado para el dato es de un byte, este se encuentra en el byte bajo de la palabra de extensión. Si el tamaño es de una palabra, el operando ocupa una palabra de extensión completa y si el tamaño es de palabra larga, el operando tiene dos palabras de extensión asociadas. Algunas instrucciones utilizan ciertas variantes del modo inmediato: variante rápida y variante inmediata. 14 4.3 Modos de registro directo En este modo de direccionamiento el operando se encuentra en uno de los 16 registros internos del microprocesador, por tanto, existen dos posibilidades según se trate de un registro de datos Dn, o de un registro de direcciones An. 4.3.1 Registro de datos directo El operando está en el registro de datos especificado por la dirección efectiva. El formato general de la instrucción es: CODOPER.N Dn,OPERANDO_DESTINO Ejemplo: MOVE.L D1,D0 4.3.2 Registro de direcciones directo En este caso el operando puede estar contenido en cualquier registro de direcciones An especificado por la dirección efectiva. El formato general de la instrucción es CODOPER.N An,OPERANDO_DESTINO Ejemplo: MOVE.L A0,D0 En este modo de operación sólo se pueden trabajar con operandos de tipo palabra y palabra larga. Si un registro de direcciones actúa como operando destino, se modifican los 32 bits del mismo siempre. Por tanto, en el caso de que se produzca una transferencia de 16 bits, se produce una extensión del bit de signo hacia los 16 bits más significativos del registro de direcciones. 15 4.4 Modos de direccionamiento de memoria En la mayoría de las aplicaciones, los datos que se van a utilizar en el programa se encuentra en la memoria RAM. Cualquier dato u operando almacenado en la memoria está perfectamente identificado a través de su dirección efectiva. 4.4.1 Registro de direcciones indirecto Los registros de dirección sirven para contener las direcciones de memoria de los operandos pero, estos, a su vez, pueden contener el propio operando (un puntero, por ejemplo). Si el registro A5 tiene el valor 26000h se podrá decir que este contiene el operando 26000h (que es una dirección) o que 26000h es la dirección de memoria donde está el dato al que se desea acceder. Para distinguir entre ambas situaciones se utilizará la nomenclatura de Motorola: si se escribe A5 se hace referencia al contenido del registro, es decir, la dirección 26000h, pero si se escribre (A5), se hace referencia al operando que ocupa la posición de memoria 26000h. El primer caso utiliza el modo de registro directo y el último caso el modo registro de direcciones indirecto. El formato general de la instrucción es CODOPER.N (An),OPERANDO_DESTINO Ejemplo: MOVE.W (A5),D1 Esta instrucción lleva el dato almacenado en la posición de memoria especificada por el registro A5 hacia el registro D1. 16 4.4.2 Registro de direcciones indirecto con postincremento En este modo, el operando se encuentra en la posición de memoria especificada por el registro de direcciones. Una vez que se ha accedido al operando, el contenido del registro de direcciones, automáticamente, se incrementa en 1,2 o 4 unidades en función de si el tamaño del operando al que se accede es de 1, 2 o 4 bytes. El formato general de la instrucción es CODOPER.N (An)+,OPERANDO_DESTINO Ejemplo: MOVE.W (A0)+,D1 Esta instrucción carga en el registro D1 el contenido de la posición de memoria apuntada por el registro A0. Al finalizar la operación se incrementa el registro A0 en dos unidades. Este modo de direccionamiento es muy útil para trasladar los datos de una posición de memoria a otra. 4.4.3 Registro de direcciones indirecto con predecremento El modo -(An) tanto en origen, en destino, o ambos, es el método más eficaz de acceder a posiciones de memoria consecutivas, barriendo la tabla desde el final hasta el principio. El formato general de la instrucción es CODOPER.N -(An),OPERANDO_DESTINO Ejemplo: 17 MOVE.B -(A0),D1 Esta instrucción primero decrementa el contenido del registro A0, y después carga en el registro D1 el contenido de la posición de memoria de tamaño byte que es apuntada por A0. 4.4.4 Registro de direcciones indirecto con desplazamiento Este modo requiere de una palabra de extensión detrás del código de operación. La dirección del dato es la suma de la dirección contenida en el registro An y la constante de 16 bits, extendida en signo, contenida en la palabra de extensión. En este modo el valor de An no cambia. El desplazamiento puede ser cualquier número con signo (-32768 a +32767), por tanto se puede acceder a la memoria en un intervalo de 32 K bytes por encima o por debajo de la dirección especificada por An. El formato general de la instrucción es CODOPER.N d16(An),OPERANDO_DESTINO Ejemplo: MOVE.L 12(A0),D0 18 4.4.5 Registro de direcciones indirecto con índice Este modo de direccionamiento requiere de una palabra de extensión con el siguiente formato: D/A Registro 15 14 13 12 W/L 11 0 10 0 9 0 8 Desplazamiento 7 0 BIT 15.- Indicador del registro índice: 0->Datos y 1-> Direcciones BITS 14-12.- Número del registro índice BIT 11.- Tamaño del registro índice: 0-> Palabra baja del registro índice extendido en signo; 1-> Palabra larga del registro índice BITS 7-0.- Desplazamiento. La dirección del operando se obtiene tras sumar el contenido del registro de direcciones con la constante de 8 bits dada en la palabra de extensión y el contenido del registro índice: EA = An + Xn + d8. El formato general de la instrucción sería: CODOPER.N d8 (An,Xn.N), OPERANDO_DESTINO Ejemplo: MOVE.L $10(A0,A3.W),D0 19 SCALE=1 en la figura anterior. 4.4.6 Direccionamiento absoluto Este es uno de los direccionamientos más simples y usados en cualquier programa. En la mayoría de los casos, los operandos se encuentran en posiciones de memoria cuya dirección absoluta es conocida y, en este modo de direccionamiento, precisamente, las palabras de extensión contienen eso, las direcciones absolutas del operando. Existen dos tipos: 4.4.6.1 Dirección absoluta corta Este modo requiere de una palabra de extensión que contiene la dirección del operando. Obsérvese que, para identificar la posición de memoria del dato, sólo se usa una palabra de extensión, es decir, 16 bits. A todas luces, se necesitan 24 bits para acceder a cualquier posición de memoria. Para ello, el microprocesador extiende el bit de signo de la palabra de extensión, el número de veces necesarios para construir una dirección verdadera. Así, en este modo, se puede acceder a las direcciones de memoria que van desde la dirección 000000h hasta la 007FFFh ( 32K bajos) si el bit de signo de la palabra de extensión es 0, y las direcciones comprendidas entre la FF8000 hasta la FFFFFFh (32K altos) si el bit de signo es un 1. El formato general de la instrucción será: CODOPER.N xxxx,OPERANDO_DESTINO Ejemplo: MOVE.W $10F8,D0 20 La palabra contenida en la posición de memoria $0010f8 y siguiente se almacena en la palabra baja del registro D0 4.4.6.2 Dirección absoluta larga En este caso el operando precisa de dos palabras de extensión, pudiéndose acceder a todo el mapa de memoria, es decir, a los 16 Mbytes El formato general de la instrucción será: CODOPER.N xxxxxx.W,OPERANDO_DESTINO Ejemplo: MOVE.L $0010F8,D0 La palabra larga contenida en la posición de memoria $0010F8 y siguientes tres, se almacena en el registro D0. 21 4.5 Modos de direccionamiento relativos En los modos indirectos o absolutos, los datos u operandos están almacenados en posiciones concretas de la memoria. En determinadas aplicaciones se requiere que un programa funcione correctamente con independencia de la zona de memoria en la que éste se cargue, lo que implica que, tanto el código, como los operandos, pueden estar, en zonas de memoria diferentes dependiendo de cuándo y cómo se han cargado estos en la memoria. A este tipo de programa se le denomina reubicable. En un programa reubicable, las referencias a los operandos que están en memoria se deben realizar de forma “relativa“ al contador de programa y no a direcciones absolutas o estáticas. 4.5.1 Contador de programa con desplazamiento Este modo de direccionamiento requiere una palabra de extensión. La dirección del operando es la suma del contenido del contador de programa y la palabra de extensión extendida en signo. Simbólicamente, se expresa como: d16(PC) La dirección efectiva del operando se calcula como EL=P+de. Evidentemente, de representa un número de 16 bits con signo, lo que nos ofrece un rango de 32Kbyrtes por encima o por debajo de la dirección en curso del contador de programa (P). El formato general de la instrucción es: CODOPER.N xxx.W,OPERANDO_DESTINO Ejemplo: 22 MOVE.W $18(P),D0 Este modo de dirección sólo es válido para operandos fuente. 4.5.2 Contador de programa con índice Este modo de direccionamiento requiere de una palabra de extensión con el siguiente formato: D/A Registro 15 14 12 W/L 0 11 10 0 9 0 8 Desplazamiento 7 0 BIT 15.- Indicador del registro índice: 0->Datos y 1-> Direcciones BITS 14-12.- Número del registro índice BIT 11.- Tamaño del registro índice: 0-> Palabra baja del registro índice extendido en signo; 1-> Palabra larga del registro índice BITS 7-0.- Desplazamiento. La dirección del operando es la suma del contenido del registro de direcciones, el entero de 8 bits dado en la palabra de extensión y el contenido del registro índice, que se puede expresar como: EL = P + Xi.N + d8. El formato general de la instrucción sería: ODOPER.N d8 (PC,Xn.N), OPERANDO_DESTINO Ejemplo: MOVE.L $10(PC,A0.W),D0 Al igual que en el modo anterior, este modo de direccionamiento sólo es válido para operandos fuente. 23 SCALE=1 en la figura anterior. 4.6 Las instrucciones y sus modos de direccionamiento En todos los modos de direccionamiento vistos, se ha utilizado la instrucción MOVE. Esta elección se debe a que ésta es una instrucción que admite prácticamente todos los modos de direccionamiento existentes para los operandos fuente y destino. No obstante, éste es un caso que no se puede generalizar. Como norma general, cada instrucción del M68000 tan sólo permite un subconjunto particular de modos de direccionamiento para sus operandos. Existen algunas clasificaciones que se basan en la forma en que se usan dichos modos y que son empleadas por diversos manuales del MC68000. La más simple, clasifica los modos de direccionamiento en cuatro categorías: DATOS: Incluye los modos que pueden usarse para referirse a operandos de datos. Todos los modos de direccionamiento están incluidos en esta categoría, a excepción del modo directo a registro de direcciones que es el único que se refiere a operando de direcciones. MEMORIA: Incluye todos los modos que pueden usarse para referirse a operandos de memoria. El modo de direccionamiento de registro directo (direcciones o datos) no pertenece a esta categoría. CONTROL: Incluye todos los modos que pueden usarse para referirse a operandos de memoria sin un tamaño asociado. Los modos de direccionamiento pertenecientes a esta categoría se usan en operaciones de control de programas como son saltos, llamadas a subrutinas, etc. ya que son operaciones sin tamaño de operando asociado. Los modos indirecto de registro con predecremento y postincremento y el inmediato no están incluidos. ALTERABLE: Incluye todos los modos que pueden usarse para referirse a operandos modificables. Un operando destino sólo puede usar los modos de direccionamiento incluidos en esta categoría. Los direccionamientos relativos al contador de programa y el direccionamiento inmediato no pertenecen a este grupo. 24 Estas cuatro categorías representan numerosas excepciones por lo que resultan poco útiles. En el siguiente cuadro se muestra una clasificación más compleja con un total de nueve categorías de direcciones efectivas y la pertenencia o no de los distintos modos de direccionamiento a cada una de ellas. Esta clasificación se deriva de la anterior y las categorías que aparecen son combinaciones de las cuatro anteriores. Las categorías son las siguientes: EL: Dirección efectiva DEA: Dirección efectiva de datos MEA: Dirección efectiva de memoria CEA: Dirección efectiva de control AEA: Dirección efectiva alterable ADEA: Dirección efectiva alterable de datos AMEA: Dirección efectiva alterable de memoria ACEA: Dirección efectiva alterable de control. MODOS DE DIRECCIONAMIENTO CATEGORÍAS DE EL EL DEA AEA ADEA Dn An X X X X X X (An) (An)+ -(An) de(An) d8(An,Ri.X) X X X X X X X X X X X X X X X X X X X X X X X XXXX XXXXXX X X X X X X X X X X de(P) d8(PC,Ri.X) X X X X X X X X #XXXXXXXX X X X 25 MEA CEA AME A ACEA X X X X X X X X X X X X X X X X X X X 5. EL CONJUNTO DE INSTRUCCIONES DEL MC68000 El 68000 tiene sólo 56 instrucciones que, combinadas con los 14 modos de direccionamiento y los cinco formatos de datos, ofrece al programador una herramienta potente para el desarrollo de programas. Nuestro objetivo es mostrar aquellas instrucciones más usuales y de carácter general, para simplificar el aprendizaje del juego. Hemos dividido las instrucciones en los siguientes grupos: – Operaciones de movimiento de datos: MOVE, MOVEA, MOVEM, MOVEQ, EXG, LEA, PEA, SWAP, LINK y UNLNK – Operaciones de aritmética entera: ADD, ADDA, ADDI, ADDQ, ADDX, CLR, CMP, CMPA, CMPI, CMPM, DIVU, DIVS, EXT, MULU, MULS, NEG, NEGX, SUB, SUBA, SUBI, SUBW , SUBX y CMP – Operaciones lógicas: AND, ANDI, EOR, EORI, OR, ORI, NOT y TST – Operaciones en BCD: ABCD, NBCD y SBCD – Operaciones de desplazamiento y rotación: ASL, ASR, LSL, LSR, ROL, ROR, ROXL, ROXR y SWAP – Operaciones de manipulación de bits: BTST, BSET, BCLR, BCHG – Operaciones de control del programa: BRA, BSR, JMP, JSR, RTR, RTS, y NOP. – Operaciones de control del sistema: RESET, RTE, STOP, TRAP, TRAPV, CHK, .. (Ver tabla resumen) 26 6. DESCRIPCIÓN FUNCIONAL EXTERNA En la siguiente figura se ha representado el conjunto de pines del microprocesador MC68000 de Motorola. 6.1 Bus de datos (D0-D15) Es un bus triestado formado por 16 líneas bidireccionales. Se utiliza para transmitir y recibir datos. Los tamaños de los datos definidos por Motorola abarcan 3 tipos: byte ( 8 bits), palabra ( 16 bits) o palabra larga (32 bits). Es evidente que para transmistir o recibir un dato de tipo palabra larga por este bus de datos se precisa de dos ciclos de lectura o escritura. Por otro lado si se transfiere un dato de tamaño byte sólo son necesarias 8 líneas de este bus de datos. 6.2 Bus de direcciones (A1-A23) Es un bus triestado unidireccional de 23 bits más A0, que se desdobla externamente en /UDS y /LDS y, por tanto, con capacidad de direccionar 16 Mbytes. Se puede decir que el registro de direcciones de memoria (MAR) utilizado en este microprocesador tiene 24 bits, (A23-A0). Los 23 bits más significativos de este registro se conectan directamente a las líneas 27 de salida del mismo nombre, mientras que el bit A0, se desdobla en las dos líneas de salida anteriormente citadas. Tanto /UDS como /LDS son activas en bajo. Si A0=0, se activa la línea /UDS habilitando los 8 bits de más peso del bus de datos, indicando que se trata de una dirección par. Si A0 = 1, se activa la línea /LDS, habilitando los 8 bits de menos peso del bus de datos, e indicando que se trata de una dirección impar. Cuando se direcciona una palabra, se activan ambas líneas /UDS y /LDS. 6.3 Control del bus asíncrono(/AS, R/#W,/UDS,/LDS,/DTACK) Este bloque esta constituido por cuatro líneas de salida más una de entrada que sirven para controlar la transferencia de datos por el bus de datos. Habilitación de direcciones (/AS) Es una línea triestado de salida, activa en nivel bajo y mediante la cual la CPU informa que la dirección existente en el bus de direcciones es válida. Normalmente los drivers que controlan las líneas del bus de direcciones tienen unos tiempos de propagación que difieren de una línea a otra, por tanto la utilidad de /AS está en la de asegurar, al exterior, que ha pasado el tiempo suficiente para que se hayan estabilizado los valores lógicos de las líneas del bus de direcciones. Lectura/Escritura (R/#W) Esta línea triestado indica el sentido del flujo de información en el bus de datos. Si el ciclo es de lectura, R/#W = 1, el bus recoge información hacia el microprocesador. Si el ciclo es de escritura, R/#W = 0, por el bus circula información procedente del microprocesador hacia la memoria o periférico. Habilitación de datos parte alta y parta baja (/UDS y /LDS) Son líneas de salida triestado, que junto con R/#W controlan el flujo de información en el bus de datos. Cuando se trabaja con datos de tipo byte, indican por qué parte del bus, parte alta (D15-D8) o parte baja (D7-D0) se realiza la transferencia del dato. Si A0=0, se 28 accede a una dirección par y /UDS está activa(/UDS=0 y /LDS=1). Si A0=1, se accede a una dirección impar y /LDS está activa (/UDS=1 y /LDS=0). Si se accede a datos de tipo palabra, el bit A0 no tiene sentido, ya que en este caso se trabaja con todo el bus de datos, entonces /UDS=/LDS=0. Reconocimiento de transferencia de datos (/DTACK) Es una línea de entrada, activa en nivel bajo, que indica que la transferencia del dato ya ha sido realizada. Durante un ciclo de lectura, cuando /DTACK=0, se captura el dato y termina el ciclo de lectura. Durante un ciclo de escritura, si /DTACK=0, el dato ya ha sido escrito y termina el ciclo de escritura. En definitiva, esta señal permite configurar la velocidad de trabajo de la CPU con la memoria y los periféricos que controla. Podemos definir los siguientes ciclos de bus en el MC68000 Ciclo de lectura Ciclo de escritura 6.3.1 Ciclo de lectura Durante un ciclo de lectura, el procesador recibe 1 o 2 bytes de datos por el bus Si la instrucción especifica un tamaño de operando de palabra o palabra larga, #UDS y #LDS se activan simultáneamente para permitir el uso de las 16 líneas del bus de datos Para operandos de tamaño palabra larga se requieren dos ciclos de lectura Cuando el operando a leer es de tamaño byte, entonces A0 determina por qué parte del bus el procesador recibe dicho byte, activando #UDS (y dato por D15-D8) para las direcciones pares y activando #LDS (y dato por D7-D0) para las impares. 29 Para el ciclo de lectura se definen ocho estados. Cada estado se corresoponde con un nivel logico de la señal de reloj del procesador: ESTADO 0 (S0): En este estado se inicia el ciclo de lectura. El procesador sitúa los valores del código de función en las salidas FC2-0 y pone a 1 la salida R/#W ESTADO 1 (S1): En este estado, el procesador coloca la dirección válida en el bus de direcciones ESTADO 2 (S2): En el flanco ascendente de S2, el procesador activa la salida #AS y los habilitadores de bus #UDS, #LDS en función del tamaño del dato y la dirección donde este se ubique (par o impar) ESTADO 3 (S3): Durante este estado no se alteran ninguna señal ESTADO 4 (S4): Durante este estado el procesador espera la señal de terminación del ciclo mediante la recepción de un 0 por su entrada #DTACK o por la activación de #BERR o de #VPA. (Si se activa esta última comienza un ciclo especial de lectura). Si no se recibe ninguna señal por estas entradas antes del flanco de bajada de S4, el procesador inserta estados de espera(ciclos de reloj completos) hasta que #DTACK,#BERR o #VPA se activen. ESTADO 5 (S5): Durante este estado no cambia ninguna señal del bus ESTADO 6 (S6): En este estado los datos del dispositivo son mantenidos en el bus de datos ESTADO 7 (S7): En el flanco de bajada del estado 7, el procesador captura los datos del bus y desactiva #AS,#UDS y/o #LDS en el flanco de subida de S7, colocando al final de S7 el bus de direcciones en alta impedancia. Por su parte, el dispositivo externo debe haber retirado #DTACK o #BERR durante este tiempo. 30 Dispositivo externo (memoria o perifericos) MC68000 Direccionamiento del dispositivo 1) Pone R/#W a 1(S0) 2) Coloca el codigo de funcion(FC2-0)(S0) 3) Coloca direccione en A23-A1 (S1) 4) Activa #AS(S2) 5) Activa #UDS y/o #LDS(S2) Introduccion de datos 1) Decodificacion de direccion 2) Coloca el dato en D15-D8 y/o D7-D0 (dependiendo de #UDS y #LDS) 3) Activa #DTACK(no SW si en S4) Adquisicion de datos 1) Almacena datos(fin S6) 2) Desactiva #UDS y #LDS(S7) 3) Desactiva #AS(S7) Termina ciclo 1) Retira el dato de D15-D8 y/o D7-D0 2) Desactiva #DTACK 6.3.2 Ciclo de escritura 31 Durante un ciclo de escritura, el procesador manda bytes de datos hacia la memoria o algún dispositivo periférico. Si la instrucción especifica un operando de tamaño palabra, el procesador activa #UDS y #LDS para habilitar las 16 líneas del bus de datos. Si el operando es de tamaño byte, en función de A0 se activará #UDS o #LDS En el ciclo de escritura se definen ocho estados: ESTADO 0 (S0): En este estado se inicia el ciclo de lectura. El procesador sitúa los valores del código de función en las salidas FC2-0 y pone a 1 la salida R/#W ESTADO 1 (S1): En este estado, el procesador coloca la dirección válida en el bus de direcciones ESTADO 2 (S2): En S2, el procesador activa la salida #AS y pone R/#W a 0. ESTADO 3 (S3): Durante este estado el bus de datos sale de su estado de alta impedancia para mostrar el dato que será escrito. ESTADO 4 (S4): En el flanco ascendente de S4, el procesador activa #UDS o/y #LDS. Además, durante este estado el procesador espera la señal de terminación del ciclo mediante la recepción de un 0 por su entrada #DTACK o por la activación de #BERR o de #VPA. (Si se activa esta última comienza un ciclo especial de escritura). Si no se recibe ninguna señal por estas entradas antes del flanco de bajada de S4, el procesador inserta estados de espera (ciclos de reloj completos) hasta que #DTACK,#BERR o #VPA se activen. ESTADO 5 (S5): Durante este estado no cambia ninguna señal del bus ESTADO 6 (S6): Durante este estado no cambia ninguna señal del bus ESTADO 7 (S7): En el flanco de bajada del estado 7, el procesador desactiva #AS,#UDS y/o #LDS y en el flanco de subida de S7, pone el bus de direcciones en alta impedancia y R/#W a 1. Por su parte, el dispositivo externo debe haber retirado #DTACK o #BERR durante este tiempo. 32 Dispositivo externo (memoria o perifericos) MC68000 Direccionamiento del dispositivo 1) Coloca el codigo de funcion(FC2-0)(S0) 2) Coloca la direccion en A23-A1 (S1) 3) Activa #AS(S2) 4) Pone R/#W a 0(S2) 5) Coloca datos en D15-8 o/y D7-0 (S3) 5) Activa #UDS y/o #LDS(S4) Introduccion de datos 1) Decodificacion de direccion 2) Captura el dato de D15-D8 y/o D7-D0 (dependiendo de #UDS y #LDS) 3) Activa #DTACK(no SW si en S4) Adquisicion de datos 1) Desactiva #UDS y #LDS(S7) 2) Desactiva #AS(S7) 3) Retira datos del bus (fin S7) 4) Pone R/#W a 1 (fin S7) Termina ciclo 1) Desactiva #DTACK 33 6.3.4 Conexión de chips de memoria al MC68000 En este apartado analizaremos la estructura de conexión entre el microprocesador MC68000 y la memoria. Supongamos que deseamos obtener un mapa de memoria con 64K de ROM que ocupe las direcciones más altas y 64K de RAM las más bajas. Se dispone de memorias de 32Kx8. Conectamos las 15 líneas menos significativas del bus de direcciones del microprocesador A15-A1 al bus de direcciones de los dispositivos de memoria. Las líneas más significativas me permiten decodificar o seleccionar los distintos elementos de memoria. En concreto, para seleccionar la memoria ROM, A23-A16=1-1, y para seleccionar la RAM, A23-A16=0-0. Por tanto, /CSROM = /A23+...+/A16 y /CSRAM = A23 + ... + A16. (Hemos supuesto que las señales de selección son activas en bajo). En la siguiente figura se ha representado la conexión de la memoria ROM. Utilizamos dos memorias ROM de 32K8, una de las cuales se conecta a los 8 bits más significativos del bus de datos y la otra a los 8 bits menos significativos. Hemos considerado que las memorias tienen líneas de selección /CS y habilitadores de salida /OE. Si /AS=0,R/#W=1,/CSROM=0, los habilitadores de chip /CS=0 están activos. En función de A1-A15 y /LDS, /UDS, se accederá al dato correspondiente. Si es de tipo palabra, /UDS=/LDS=0, y las dos memorias ROM vuelcan su contenido en el bus de datos. Si se accede a un dato de tipo byte, /LDS o /UDS determinan la memoria que vuelva su contenido. Una estructura similar aparecerá en la selección de la memoria RAM, en cuyo caso adquiere sentido la línea de lectura/escritura. Por último, recordamos que es misión de la circuitería externa la activación de la línea de /DTACK, para conseguir la correcta transferencia de información en los ciclos de lectura y escritura. Esta señal dependerá de la rapidez de respuesta de los dispositivos externos. Si por ejemplo tenemos memorias lentas, DTACK debe activarse cuando estas hayan colocado su 34 contenido en el bus o cuando ya se haya escrito la información en las mismas. Un posible esquema de un circuito que permite la generación de esta señal se puede basar en un contador que se incrementa en cada ciclo de reloj CLK del microprocesador. La salida de CY, se utiliza para generar esta señal, de forma que está se activa cuando el contador ha pasado un tiempo igual al módulo del mismo multiplicado por el periodo de la señal de reloj. El módulo del contador deberá escogerse en función de las características temporales de la memoria y periféricos, de forma que la activación del Cy del contador asegure los tiempos de lectura y escritura de estos periféricos externos. Otro posible esquema los da la utilización de circuitos de tiempo o multivibradores, que a partir de la activación de la señal /AS, genera un pulso pasado un determinado tiempo. Este tiempo puede ser programado por un resistencia y un condensador. No obstante, para memorias cuyo ciclo de lectura o escritura sea comparable o menor con los ciclos de lectura o escritura del 68000, la propia lógica combinacional que habilita el acceso a las memorias se puede utilizar como señal /DTACK. 6.4 Control de arbitraje del bus Estas señales permiten el dialogo entre el microprocesador y otros controladores existentes en el sistema para determinar quién será el maestro del bus y por tanto quién tendrá acceso a la memoria del sistema. #BR: Bus Request. Esta línea de entrada indica al microprocesador que existe un controlador externo que solicita ser el controlador del bus para acceder a la memoria. #BG: Bus Grant. Esta línea de salida indica a posibles controladores externos que el microprocesador cede el bus cuando termine el ciclo de bus actual. #BGACK: Bus Acknowledge. Esta entrada indica al micoprocesador que un dispositivo externo controla ahora el bus. Cuando el controlador termine, desactiva esta entrada y el microprocesador se hace cargo nuevamente del bus. 6.5 Control de interrupciones 35 Las entradas #IPLx codifican el nivel de petición de interrupción. El nivel 0, #IPLx(x=0,1,2) =1 indica que no hay interrupción, y el nivel 7, #IPLx(x=0,1,2)=0 indica la interrupción de mayor prioridad y que no es enmascarable. Estas señales deben permanecer sin modificarse hasta que el microprocesador inice el ciclo de recnonocimiento de interrupciones ( o FC0-FC2 pasen a nivel alto), para así asegurar que la interrupción será reconocida. El nivel de interrupción que puede atender el microprocesador viene fijado por los bits I0,I1,e I2 del SR. Si el nivel de petición de interrupción es de mayor prioridad que el fijado por la máscara, se atenderá la petición. Cuando se acepta una interrupción se procede al ciclo de reconocimiento de interrupciones que se estudiará más adelante. 6.6 Control del sistema #BERR. Bus error. En una arquitectura típica, en la que se requiere el intercambio de información con dispositivos externos, existe la posibilidad de que este intercambio no ocurra. Por tanto, es necesario la existencia de una entrada que se active, por medio de una electrónica externa cuando transcurra un tiempo prefijado, sino se realiza el acceso al dispositivo externo. Esta entrada es /BERR y su activación informa al procesador de que existe un problema en el ciclo de bus que actualmente se está ejecutando. Estos problemas pueden ser el resultado de: 1. Dispositivos que no responden 2. Fallo de adquisición del número de vector de interrupción 3. Alguna otra aplicación dependiendo del error. El microprocesador tiene dos opciones cuando ocurre un error de bus: realizar otro ciclo de bus o directamente realizar un proceso de excepción. intentar El circuito externo que permite la activación de esta entrada del microprocesador debe controlar la duración existente entre la activación de la línea /AS y la respuesta /DTACK. Si una vez activa la señal /AS, la señal /DTACK no se ha activado pasado un tiempo máximo, este circuito debe activar la señal /BERR. 36 El circuito de la figura recibe, como señal de reloj, la salida E del microprocesador. Esta salida es una señal periódica de frecuencia 10 veces menor que la frecuencia de funcionamiento del microprocesador. Cuando se inicia un ciclo de bus, la línea /AS se activa, esto provoca que el registro inhabilite el clear y que el primer biestable almacene un uno cuando se reciba un flanco de subida por la línea E. Si /AS se encuentra activa durante cuatro ciclos de E o, de forma equivalente, 40 ciclos del microprocesador, la línea /BERR se activará. Sólo en el caso de que se realice correctamente el ciclo de bus en menos de 40 ciclos, la línea /AS se desactivaría por lo que el registro se borraría. D1 D2 D3 D4 /AS E CLK CLR Q1 Q1 Q2 Q2 Q3 Q3 Q4 Q4 /BERR 6.6.1 Reintento del ciclo de bus Si \BERR =0 durante un ciclo en el cual /HALT =0, se inicia una operación de reintento. El microprocesador termina el ciclo de bus y pone en alta impedancia los buses de datos y direcciones. Esta situación permanece hasta que /HALT pase a 1, entonces el microprocesador reintenta el último ciclo de bus usando los mismos códigos de función, dirección y datos (para una operación de escritura). Para que el microprocesador realice un reintento del ciclo de bus la señal /BERR debe haber pasado a 1 al menos un ciclo de reloj antes de que /HALT lo hiciera. 37 6.6.2 Doble error de bus Cuando ocurre un error de bus, el microprocesador comienza una excepción en la que guarda cierta información en la pila de supervisor. Si ocurre otro error de bus durante el proceso de excepción (antes de la ejecución de otra instrucción) el microprocesador para y coloca la línea de \HALT a 0. Esto se reconoce como doble error de bus. Únicamente mediante un reset externo se puede sacar el microprocesador de este estado de parada. #RESET: Esta es una línea bidireccional que actua a veces como entrada, y a veces como salida. Como entrada, si se activa junto con HALT durante 10 ciclos de reloj o 10ms en power-up, se produce la secuencia de inicialización en la que el microprocesador responde leyendo el vector de reset de la tabla de vectores, que carga en el puntero de pila del supervisor, lee el siguiente vector de la tabla para almacenarlo en el registro PC e inicializa los bits de interrupciones al nivel 7. Si se ejecuta la instrucción RESET esta línea actua como salida poniendo a 0 el pin de RESET durante 124 ciclos de reloj. En este caso el procesador está intentando resetear el resto del sistema, mientras que no existe cambio del estado interno del procesador. 38 #HALT: Una entrada en esta línea bidireccional provoca que el microprocesador pare el ciclo del bus actual. Esta línea actúa como salida cuando el procesador para de ejecutar instrucciones( como por ejemplo cuando sucede un doble error de bus). De esta forma se avisan a los dispostivos externos de que el microprocesador ha parado. 6.7 Control de periféricos síncronos Estas señales sirven para manejar los dispositivos de entrada/salida asociados al microprocesador MC6800. E: Esta señal es la entrada de habilitación estándar de los periféricos del MC6800. En realidad es una señal de reloj cuya frecuencia es diez veces menor que la señal de reloj de entrada CLK del MC68000 (seis ciclos en nivel bajo y cuatro en alto). Esta salida se conecta directamente a la entrada E de los perifericos y siempre está funcionando. #VPA: Valid Peripheral Adress. Esta línea de entrada avisa al MC68000 de que está seleccionando un periférico de la familia del MC6800 y que tiene que sinconizarse con la señal E para poder acceder a él. Asimismo esta entrada también indica que el microprocesador debe utilizar la vectorización automática para atender interrupciones. #VMA: Valid Memory Adress. Esta línea de salida indica al periférico que la dirección de memoria es válida y que el microprocesador está sincronizado con la señal E. 6.7.1 Operación de transferencia de datos 1) El procesador inicia un ciclo normal de escritura o lectura 2) La electrónica externa activa /VPA indicando que se está accediendo a un 39 periférico síncrono 3) El procesador espera hasta que la señal E pase a nivel bajo, entonces activa /VMA 4) El periférico espera hasta que E se active, entoces transfiere los datos. 5) El procesador espera que E vuelva a 0 ( en un ciclo de lectura los dato son cargados), entonces desactiva primero /VMA y después /AS, /UDS y /LDS. 6) 6) Comienza un nuevo ciclo. 6.8 Estado del procesador Estas salidas codifican el estado interno del procesador. La siguiente tabla resume los códigos asociados a los estados internos. Estas salidas son válidas cuando #AS está activa. FC2 0 0 0 0 1 1 1 1 FC1 0 0 1 1 0 0 1 1 FC0 0 1 0 1 0 1 0 1 Tipo de ciclo Indefinido Datos de usuario Programa de usuario Indefinido Indefinido Datos de supervisor Programa de supervisor Reconocimiento de interrupciones 7. PROCESOS DE EXCEPCIÓN Existen un gran número de situaciones en las cuales es necesario disponer de mecanismos que permitan interrumpir la ejecución normal de una secuencia de instrucciones para pasar a atender, de forma inmediata, esa situación particular. Las excepciones pueden deberse a muchas causas diferentes y se clasifican en internas o externas según éstas sean debida a un error interno, una instrucción especial, o una señal procedente del exterior. La siguiente figura recoge una clasificación de las excepciones. 40 Excepciones Internas Error de Ejecucion Traza Externas Instrucción ilegal Reset Error de bus Peticion de interrupcion Division por cero Autovector Violacion de privilegio Usuario (no autovector) Emulador Instruccion ilegal Error en direccion 7.1 Vectores de Interrupción Cada excepción dispone de una posición de memoria que contiene su vector de excepción, que no es más que una dirección, la dirección de memoria donde comienza la rutina de servicio de la excepción. Cuando se produce una situación que provoca la excepción, el MC68000 busca su vector correspondiente y, después de salvar en la pila los registros PC y SR, bifurca a la rutina almacenada a partir de la dirección contenida en dicho vector. Se disponen de 255 vectores de excepción almacenados en la tabla de vectores de excepción que ocupa la porción de la memoria RAM que comienza a partir de la dirección $000000. Todo vector de excepción tiene el tamaño de una doble palabra (4 bytes), a diferencia del vector de RESET que ocupa dos dobles palabras (8 bytes), por lo que la tabla de vectores ocupa un total de 1Kbyte. Cada vector se identifica a través del número de vector (N). Usando este número de vector, el microprocesador determina la dirección donde se encuentra el vector mediante la operación 4*N que equivale a desplazar N dos posiciones a la izquierda insertando dos ceros por la derecha. De estos 255 vectores, los 64 primeros (0 al 63) están preasignados, aunque pueden sobreescribirse. Los demás vectores (192) quedan libres para ser asignados a dispositivos periféricos como vectores de interrupción de usuario. El siguiente cuadro muestra el contenido de la tabla de vectores de excepción. 41 NÚMERO VECTOR DIRECCIÓN DECIMAL HEX. ASIGNACIÓN 0 0 000 Reset: SSP inicial - 4 004 Reset: PC incicial 2 8 008 Error de Bus 3 12 00C Error en dirección 4 16 010 Instrucción ilegal 5 20 014 División por cero 6 24 018 Instrucción CHK 7 28 01C Instrucción TRAP 8 32 020 Violación de privilegio 9 36 024 Traza 10 40 028 Emulador línea 1010 11 44 02C Emulador línea 1111 12 48 030 (No asignado, reservado) 13 52 034 (No asignado,reservado) 14 56 038 (No asignado, reservado) 15 60 03C Vector de interrupción no inicializado 16-23 64-92 040-05C (No asignado, reservado) 24 96 060 Interrupción espúrea 25 100 064 Autovector interrupción nivel 1 26 104 068 Autovector interrupción nivel 2 27 108 06C Autovector interrupción nivel 3 28 112 070 Autovector interrupción nivel 4 29 116 074 Autovector interrupción nivel 5 30 120 078 Autovector interrupción nivel 6 31 124 07C Autovector interrupción nivel 7 32-47 128-188 080-0BC Vectores instrucción TRAP 48-63 192-252 0C0-0FC (No asignado, reservado) 64-255 256-1020 1003FC Vectores de interrupción de usuario) 7.2 Secuencia de procesamiento de una excepción La atención de una excepción debe cubrir los siguientes aspectos: - La atención inmediata a la excepción, con interrupción, incluso, si la prioridad es 42 alta, de la instrucción en curso. - La bifurcación a la dirección correcta de comienzo de la rutina de servicio de la excepción. - El retorno correcto a la secuencia de instrucciones interrumpida, una vez finalizada la rutina de servicio. Para conseguir estos objetivos, el procesamiento de una excepción por el MC68000 transcurre en una secuencia de 4 pasos: 1. El registro SR se copia en un registro interno. Se desactiva el modo traza y se activa el bit S por lo que el microprocesador entra en modo supervisor. Para excepciones asociadas a peticiones de interrupción, o a RESET, se actualiza el valor de la máscara de interrupciones I2-I0. 2. Se determina el número de vector de excepción por lógica interna, si es uno de los preasignados, o a partir de una búsqueda denominada "reconocimiento de interrupción", si se trata de una interrupción de usuario. A partir del número de vector se genera la dirección del vector de excepción. 3. Se salvan, en la pila del supervisor (SSP), los contenidos del contador de programa PC y del registro de estado SR. Primero se guarda PCH, seguido de PCL y SR. 1. Por último, el microprocesador carga en el registro PC el contenido del vector de interrupción. Después de esta secuencia, el procesador reanuda el ciclo normal de ejecución de instrucciones pero, claro, en la dirección de comienzo de la rutina de tratamiento de la excepción. El retorno a la secuencia previa de instrucciones, una vez completada la rutina de excepción, se realiza mediante la instrucción RTE que recupera de la pila el registro SR, después PCL y finalmente PCH. Tras la ejecución de RTE, el microprocesador reanuda el 43 estado y la ejecución de instrucciones por el punto interrumpido. 7.3 Tipos de excepción Los tipos de excepción mostrados en la tabla de excepción pertenecen a diferentes grupos de prioridad y, aunque su procesamiento se realiza de la forma genérica descrita anteriormente, las acciones que toma el MC68000 antes de dar comienzo a dicho procesamiento, y que determinan la urgencia con que es atendida la excepción, son ligeramente diferentes para cada uno de estos grupos. El siguiente cuadro muestra los tres grupos de prioridad existentes desde el grupo 0, correspondiente a las excepciones de prioridad más alta y que deben ser atendidas de inmediato con interrupción, incluso, del ciclo de bus actual, hasta los grupos 1 y 2 de menor prioridad que no obligan a adoptar medidas tan drásticas. GRUPO Y PRIORIDAD TIPO DE EXCEPCIÓN 0 Alta Reset Error de BUS Error en dirección 1 Traza Interrupción Comienza el procesamiento de la excepción cuando termina la instrucción actual Instrucción ilegal Instrucción no implementada Violación de privilegio Comienza el procesamiento de la excepción cuando termina el ciclo de bus actual TRAP, TRAPV,CHK División por cero Comienza el procesamiento de la excepción cuando se ejecuta la instrucción 2 Baja ACCIÓN Se aborta el ciclo de bus actual dentro de 2 ciclos de reloj 7.3.1 Excepciones internas El procesamiento de las excepciones generadas internamente sigue el esquema general descrito en el apartado de secuencia de procesamiento de interrupción, salvo en el caso de error de dirección. A) ERRORES DE EJECUCIÓN -> Error en dirección. Se produce cuando el MC68000 intenta a acceder a una palabra o a una palabra larga con una dirección impar. Una característica de esta excepción es que, además de los registros PC y SR, en la pila se guarda cierta información adicional con el fin de ayudar a la rutina de servicio a identificar la causa del error. Esta información incluye la primera palabra de la instrucción que produjo el error (tomada directamente del contenido del registro de instrucción del procesador), la dirección en cuyo acceso de produjo el error , y una palabra denominada de "super-estado" que indica: - Si la operación era de lectura o de escritura - Si el procesador se encontraba procesando una instrucción o una excepción 44 de los grupos 0 y 1 - Los valores de las líneas de código de función FC2-0 -> Instrucción ilegal El MC68000 detecta una instrucción ilegal si, al buscar la primera palabra de una instrucción, encuentra que no contiene ninguno de los códigos de operación válidos de su repertorio de instrucciones. La excepción se trata como en el caso habitual, con bifurcación al vector número 4. La ejecución de la instrucción ILLEGAL tiene el mismo efecto. -> Instrucción de emulación. Si los códigos de operación encontrados son las combinaciones 1010 o 1111, entonces se bifurca a los vectores 10 u 11, respectivamente. Estos códigos de operación han sido reservados para extender el juego de instrucciones del MC68000 mediante emulación. Pueden usarse instrucciones comenzando por uno de estos códigos que serán emuladas por el software de la rutina de servicio de la excepción correspondiente. -> Violación de privilegio Se produce una violación de privilegio cuando se intenta ejecutar una instrucción reservada al modo supervisor con el bit S=0, es decir, en modo usuario. B) TRAZA El modo traza se activa cuando se pone a 1 el bit T del registro de estado SR. En este modo, denominado también "paso a paso", el procesador genera una excepción, con vector de excepción número 9, después de ejecutar cada instrucción de una secuencia. Como parte del procesamiento de esta excepción, el MC68000 pone a 0 el bit T, con lo cual la rutina de servicio de la exepción se ejecuta en modo normal. Al retornar se recupera el valor de T de la pila. C) INSTRUCCIONES TRAP,TRAPV,CHK 45 Estas tres instrucciones permiten generar una excepción directamente desde una instrucción, es decir, en el punto exacto de la secuencia de código elegido por el programadr: -> TRAP Esta instrucción tiene el formato TRAP #numero_trap. Con numero_trap un entero de 4 bits (0 al 15). El número de TRAP identifica uno de los 16 vectores de excepción asignados a esta instrucción. Esta instrucción proporciona una vía para acceder a rutinas genéricas almacenadas la memoria no volatil (llamadas a la BIOS) o en la implementación de puntos de ruptura. -> TRAPV La instrucción TRAPV, situada inmediatamente después de una instrucción aritmética susceptible de producir desbordamiento (que pueda poner el código de condición V=1), produce una excepción en caso de que se produzca ese hecho, -> CHK Esta instrucción compara el contenido de un registro con un límite superior almacenado en un lugar especificado. Si el contenido del registro supera dicho límite, se produce la excepción. Puede resultar útil para comprobar, por ejemplo, antes del acceso a un elemento de una matriz, si el índice se encuentra dentro del rango apropiado. 7.3.2 Excepciones externas A) RESET Cuando se produce una excepción por RESET se persiguen objetivos algo distintos al resto de las excepciones. En este caso no tiene sentido guardar los valores del PC y el SR en la pila porque no se desea volver a recuperar el estado del procesador.. Además, como se pretende inicializar el procesador, se carga también un valor inicial en el registro SSP además del PC. Este último se carga con el vector de excepción 0 y, el registro SSP, con el vector de excepción 1. En concreto el registro SR se inicializa de la forma siguiente: 1) Se desactiva el modo traza T=0 2) Se activa el modo supervisor: S=1 3) Se enmascaran todos los niveles de prioridad de interrupción: I2-I0=111 Cualquier sistema basado en el MC68000 debe disponer de un circuito capaz de activar la línea RESET cuando se conecta la fuente de alimentación del sistema. El vector de excepción 0 determina, por tanto, la dirección de comienzo del software de arranque del sistema y, tanto los vectores 0 y 1, como la propia rutina (boot), deben encontrarse en memoria no volátil. Si alguno de estos dos vectores no se recupera correctamente, se produce fallo de bus y el procesador se detiene activando la señal HALT. 46 B) ERROR DE BUS Ocurre cuando la electrónica externa activa la entrada #BERR. El procesamiento es idéntico al de error de dirección salvo que se usa el vector de interrupción 2. Si cuando se procesa la excepción de error de bus, la entrada #BERR se activa (doble error de bus), el 68000 para. En tal situación, sólo un RESET permite reanudar la ejecución de instrucciones. C) INTERRUPCIONES La activación de las entradas #IPLn codifica el nivel de petición de interrupción. El nivel 0, #IPLn(n=0,1,2)=1 indica que no hay interrupción, y el nivel 7, #IPLn(n=0,1,2)=0 indica la interrupción de mayor prioridad o interrupción no enmascarable. Estas señales deben permanecer estables hasta que el microprocesador inice el ciclo de reconocimiento de interrupciones. El nivel de interrupción que puede atender el microprocesador viene fijado por los bits I0,I1,e I2 del SR. Si el nivel de petición de interrupción es de mayor prioridad que el fijado por la máscara, se atenderá la petición, en caso contrario, no, a excepción, como ya se ha mencionado, para el nivel 7. Cuando el MC68000 acepta una interrupción, se desencadenan los mismos procesos que los descritos para las excepciones, salvo que el número del vector de excepción se obtiene mediente un ciclo especial de lectura. Se salvan en la pila el contador de programa y el registro de estado, se activa el bit S, se desactiva el bit T, se actualizan los bits I2,I1,I0 al nivel de la interrupción peticionaria y se inicia el ciclo de reconocimiento de interrupción. En el ciclo de reconocimiento de interrupción el MC68000 inicia un ciclo especial de lectura en el que las salidas FC2,FC1,FC0 están todas a 1, y los bits A3,A2,A1 identifican el nivel de petición de interrupción que, el microprocesador, está procesando en ese momento. A partir de aquí pueden ocurrir varias cosas: – – – – Se activa la entrada #VPA que identifica que la interrupción fué solicitada por un periférico síncrono. En tal caso, el microprocesador utiliza el autovector asociado al nivel de interrupción actual. Se activa la entrada #DTACK que identifica el fin de un ciclo de lectura normal. En este caso, el periférico, además de activar esa señal, ha colocado, en el bus de datos un byte que contiene un número de vector de excepción. Este número de vector debe estar comprendido entre 64-255, constituyendo los vectores de excepción de usuario. Se activa la entrada #DTACK pero se recibe, como número de vector, el $F. Esto da lugar a la interrupción no inicializada. Todos los periféricos del 68000 disponen de un registro que contiene el vector de interrupción que se situá en el bus de datos en un ciclo de reconocimiento de interrupción. Dicho registro viene inicializado, por defecto, con el valor $F. Se activa la entrada #BERR. Esto indica que, en el ciclo de interrupción, el 68000 no ha recibido ningún vector de interrupción, es decir, se ha producido un error de bus. Esto provoca la generación de la interrupción espúrea, que tiene, como número de vector de excepción, el 24. 47