ARQUITECTURA DE LAS COMPUTADORAS UNIDAD 7: Unidades

Anuncio

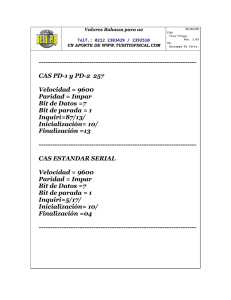

ARQUITECTURA DE LAS COMPUTADORAS UNIDAD 7: Unidades de Entrada-Salida Transferencia de ENTRADA Y SALIDA • Hasta ahora se ha estudiado la interconexión del procesador (CPU) y la unidad de memoria de acceso aleatorio (RAM). donde los bits se transmiten en paralelo (megabit/seg o Mb/s) • Ahora se debe incluir la interconexión con sistemas externos (periféricos) . Las instrucciones y los datos almacenados en la memoria deben provenir de dispositivos de entrada. Asimismo los resultados deben transmitirse al usuario mediante dispositivos de salida. En una operación de entrada la información tiene como destino la memoria principal. En una operación de salida es al revés. • Se trata de la interconexión entre sistemas digitales secuenciales y combinacionales. La operación de los periféricos debe sincronizarse con la operación de la CPU y de la unidad de memoria, estableciendo un control sobre la transferencia de la información. Cualquiera sea la forma de controlar la transferencia de información externa la interconexión física puede ser: paralelo o serie. S1 S1 P1 T BUS DATOS DATO R P2 DATO VÁLIDO S. Envío Señal de envío Paralelo Serie En el PC se tienen puertos (port) de comunicación serie y paralelo. Se trata de un hardware dedicado al control de la transferencia y al almacenamiento temporario de la información. Desde los puertos los datos salen en paralelo ( byte) hacia la memoria a traves de un registro de la CPU. La comunicación se soporta por el bus de datos. Transferencia paralelo Un receptor debe reconocer que un transmisor le envía información, el control puede resolverse de 2 formas: a) Control estroboscópico: Emplea una línea especial por la cual se transmite una señal de control. UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 1 de 9 Datos Sincronismo Señal Sincronismo S1 Fuente S2 . Destino 1 0 0 1 Dato El flanco ascendente indica al receptor que tiene datos están disponibles b) Apretón de manos (HAND SHAKING): Emplea dos líneas de control. DATO - Coloca Datos - Habilita envío DATO VÁLIDO S. Envío - Acepta Datos - Habilita Aceptación S. Aceptación Señal de envío T Deshabilita Envío R DATOS Deshabilita Aceptación Señal de Aceptación -Secuencia de eventos T-R Ahora hay un control tanto en el envio como una confirmacion de la recepción. Transferencia Serie Los datos se envían por un hilo de transmisión (Tx) y se reciben por otro, de recepción (Rx). a) Transmisión sincrónica: La transferencia se controla mediante señales de control por hilos independientes a los de envío de información. n bit de información. S1 S2 Bit de comienzo Bit`s de fin de transmisión • La duración de los bit se controla con los flancos ascendentes, que coinciden con las conmutaciones de los sucesivos bit de información. En los flancos descendentes la información está estable para ser leída por el receptor. • Para indicar el inicio de la transmisión, por el mismo hilo de dato se envían caracteres de sincronismo, previo a los datos. 1 BYTE 1 BYTE 11111111 11111111 DATO 1 DATO 2 Caracteres de Sincronismo b) Transmisión Asincrónica: La transferencia se controla mediante señales que se combinan con las de información y se envía por el mismo hilo. UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 2 de 9 Modos de Transferencia La transferencia de datos desde periféricos puede manejarse en uno de cuatro modos posibles: 1- Transferencia de datos controlada por el programa. 2- Transferencia de datos iniciada por interrupción. 3- Transferencia con acceso directo a memoria (DMA). 4- Transferencia a través de un procesador de E/S (IOP). • Un enlace de comunicación debe resolver las diferencias operativas entre el procesador (CPU) y los periféricos. Estos últimos siempre incluyen un sistema electromecánico, provocando diferencias notables de velocidad. • Se incluyen componentes de hardware que permiten sincronizar el CPU con los periféricos. CPU BUS I/O INTERFAC DISCO INTERFAC CD INTERFAC PRINTER Puerta Paralelo (de propósito general) Se indica un circuito integrado (IC) de puerta paralelo de propósito general. Permiten la conexión con periféricos de impresión, medición, transmisión y control. Son programables y pueden adaptarse a diferentes requerimientos según el tipo de periféricos. Se indica una puerta con capacidad para comunicarse con perifericos de 8 o 16 bit. Tiene dos partes idénticas A y B. Se supone que los datos del CPU llegan en 8 bit en paralelo. La puerta se selecciona mediante las líneas de control selectoras de chips CS0, CS1 y CS2. Mediante las líneas de selección de registros, RS0 y RS1 se accede a los 4 registros internos DRA, DRB, CRA, CRB. Las interrupciones externas llegan por CA o CB y se transfieren al procesador por la línea IRQA e IRQB. Estas interrupciones externas quedan registradas en la misma puerta, en los registros internos de control CRA y CRB respectivamente. Si hay una sola línea IRQ directa al procesador, será necesario reunirlas en una compuerta OR, en este caso mediante la lectura desde el procesador de los CR se puede discriminar que sector de la puerta genero la interrupción. Toda lo operatoria de leer o escribir en los registros internos de datos y de control, como asi tambien los codigos binarios para programar diferentes forma de trabajo de entrada/salida se encuentran en la hoja técnica del fabricante del circuito integrado (IC). UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 3 de 9 CA2 Interrup. CA1 PA0 CS0 CS1 CS2 DRA A PA7 CRA CPU * Para 8 o 16 bit, según el periférico. * CA/CB : líneas de interrupción externas * DR : Registro de datos bidireccional (8bit) RS0 RS1 de RESETpara definir: CRB R/ W IRQA PB0 * CR : Registro de control programación puerta (8bit), mediante b0 a b5 PB7 - entradas - salidas - tipo de flanco para interrupción B DRB CB1 Interrup. CB2 IRQB Interrup. CR IRQA RQB b5 b4 b3 b2 b1 b0 Los bit IRQA/B registran las interrupciones para que el procesador identifique el DR que debe leer. Port 0 CA1 CA2 Periférico 1 0 1 OPERACIÓN HANDSHAKE Modelo de transferencia * El periférico avisa que tiene disponible dato mediante un flanco de 1 a. * La CPU lee el dato y a través de CA2 mediante un flanco de 0 a 1 La línea de aviso al receptor se denomina strobe. La línea del receptor que indica que los datos se han recibido y esta disponible para nuevos datos, se llama acknowledge (admisión). Puede haber una tercera línea denominada busy para indicar dispositivo ocupado Toda la operación de programación y lectura y/o escritura, se realiza bajo control de programas (rutinas de servicio) residentes en memoria (RAM/ ROM/PROM/EPROM) del sistema. La puerta paralelo de un PC esta especialmente preparada para manejar el periférico impresora, (no es de propósito general) no obstante puede adaptarse para realizar la entrada/salida de señales de medición y control, con ciertas limitaciones (Ver Trabajo UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 4 de 9 Práctico). De esta manera la PC puede convertirse en una central de alarmas, donde los datos entran y salen por la puerta, ejecutando un programa fijo en forma cíclica. Puerta Paralelo del PC (tipo CENTRONIC) • Además de puerta paralelo para la impresora (parallel printer port) es un recurso importante para el intercambio de información digital externa a la PC. /STRB D0 D1 D2 D3 D4 D5 D6 D7 /ACK BUSY PAPER END SELECT •1 •2 •3 •4 •5 •6 •7 •8 •9 •10 •11 •12 •13 14• 15• 16• 17• 18• 19• 20• 21• 22• 23• 24• 25• AUTO FEED ERROR INIT SELECT IN GND GND GND GND GND GND GND GND Esta dividido en 3 Reg. Port: DATOS: (D0, D1, ..., D7) Out ESTADO: (ERROR, SELECT, P. END, ACK, BUSY) Input CONTROL: (STROBE, A.FEED, INIT, SELECT IN) I/O Los registros pueden se leidos o escritos mediante la instrucción IN o OUT , respectivamente a traves del registro AX El manejo de las líneas de control y comando para una operación de R/W, la realiza una rutina de la ROM BIOS. Puerta Serie Para comunicación por dos lineas solamente (Modem, instrumentos o equipos a periféricos a distancia. CS0 CS1 CS2 RS0 RS1 RESET R/W IRQ RDR SR CR RD (Received Data) CTS (Clear To Send) DCD (Data Carrier Detect) DSR (Data Set Ready) RTS (Request To Send) DTR (Data Terminal Ready) TD (Transmitted Data) TDR GND (Ground) RDR : Registro recepción de datos. TDR : Registro transmisión de datos. SR : Registro de estado: Para registrar, error paridad, saturación, pérdida de portadora. CR : Registro de control : Para programar, paridad, velocidad, nro. de bit x carácter, bit de stop UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 5 de 9 Para transmisión asincrónica: En condiciones de no-transmisión, la línea de dato se encuentra en un alto. Al comenzar la transmisión de un carácter, se inicia con un flanco decreciente seguido del bit de START, que permite la sincronización del periférico o la puerta. 1 bit START 7 bit DATA 2 bit STOP 1 bit PARITY 7 DATA BIT BIT de STOP BIT de START PARITY (EVEN (PAR) o ODD (IMPAR)) ONE CHARACTER WORD ( 11 Bit´s ) Parámetros típicos: Suponiendo la duracion de un bit (BIT TIME) de: 9.09 ms. Se tienen las siguientes caracteristicas: BAUD RATE = 1/BIT TIME = 1/9.09 ms. = 110 baud Tiempo de palabra = 11 bit x 9.09 x 10-3 s ≅ .1 seg PC 1 DTE 1 DCE 1 RS - 232 C ENLACE MODEM DCE 2 DTE 2 PC 2 RS - 232 C Word rate = 1 / 0.1 seg = 10 word/seg. Velocidad = 10 word/seg x 8 bit/caract = 80 bit/seg. (incluye paridad) Se observa que la velocidad queda determinada por la duración de un bit (BIT TIME). Verifique el Bit Time para un modem de 56.000 Baudios. Para velocidades de 300 y 1200 Baudios se tiene: BAUD RATE BIT TIME (ms) WORD TIME (s) WORD RATE VELOCIDAD 300 3.33 .0366 27.32 218.6 1200 .833 .0092 108.7 870 Puerta Serie (RS-232) NORMA RS-232 C: Está normalizada para la interconexión de equipos que funcionen como DTE (Data Terminal Equipment y DCE (Data Comunications Equipment). El conector tiene 25 líneas especificadas (DB-25), tambien puede utilizarse un conexión reducida con conector DB-9. La comunicación se realiza punto a punto. Es decir un periférico por cada puerta. UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 6 de 9 UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 7 de 9 Puerta Serie USB (Universal Serial Bus) Se trata de un bus formado por 4 cables; 2 de alimentacion y 2 de datos. Sobre este bus se pueden conectar hasta 127 periféricos diferentes (Dispositivos USB), funcionando simultaneamente y operando con una misma PC (Host USB). El puerto y los dispositivos USB es del tipo Plug& Play USB data packets . 1 ms Un puerto serie tradicional es capaz de transmitir hasta 112,5 Kb/s y el puerto paralelo entre 600KB/s y 1,5MB/s, pero un puerto USB es capaz de llegar a alcanzar entre 1,5Mb/s (Baja) y 12Mb/s (Alta). por lo que es la conexión ideal para módem de 56K, scáneres (como alternativa de similar coste a los de puerto paralelo), CD-ROMs externos, dispositivos de copia de seguridad externos, etc. La ampliacion del bus se realiza por medio de “Hub” que son distribuidores de bus con una entrada y cuatro salidas. Con ellos se llega a los 127 perifericos Los dispositivos que se conectan al bus USB son capaces de recibir y transmitir información de dos tipos: Usuario y Control. Esto lo hace en base a 4 tipos de bloques para lo cual se ha definido un protocolo de comunicación. Los datos son enviados en paquetes de 8 a 256 byte. Todo el trafico de datos se realiza en tramas de 1 ms aproximadamente En baja velocidad (1,5 Mb/s) la longitud del bit es 666.7 ns y de 83,3 ns en alta velocidad (15 Mb/s ). La arquitectura de comunicación responde al tipo Maestro-Esclavo; la PC constituye el Maestro y los Esclavos son los perifericos. Siempre la PC solicita informacion y los perisfericos, que estan numerados, responden. UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 8 de 9 El acceso al bus es bajo la modalidad de Token o “testigo”. Para el control de errores utiliza el modelo CRC (Código de Redundancia Cíclica) implementando por hardware. El bus es de + 5 V y puede se cargado con hasta 100 mA. Esto permite alimentar perifericos de bajo consumo. Los de mayor consumo deberan autoalimentarse. En cualquier caso instalar un fusuble sobre la linea + 5V para limitar la corriente. 1 2 3 4 Conector USB - doble Conector USB – Tipo A UTN-FRM Arquitectura de las Computadoras Unidad 7 Página 9 de 9