informática industrial. 3º ingeniería técnica industrial. especialidad

Anuncio

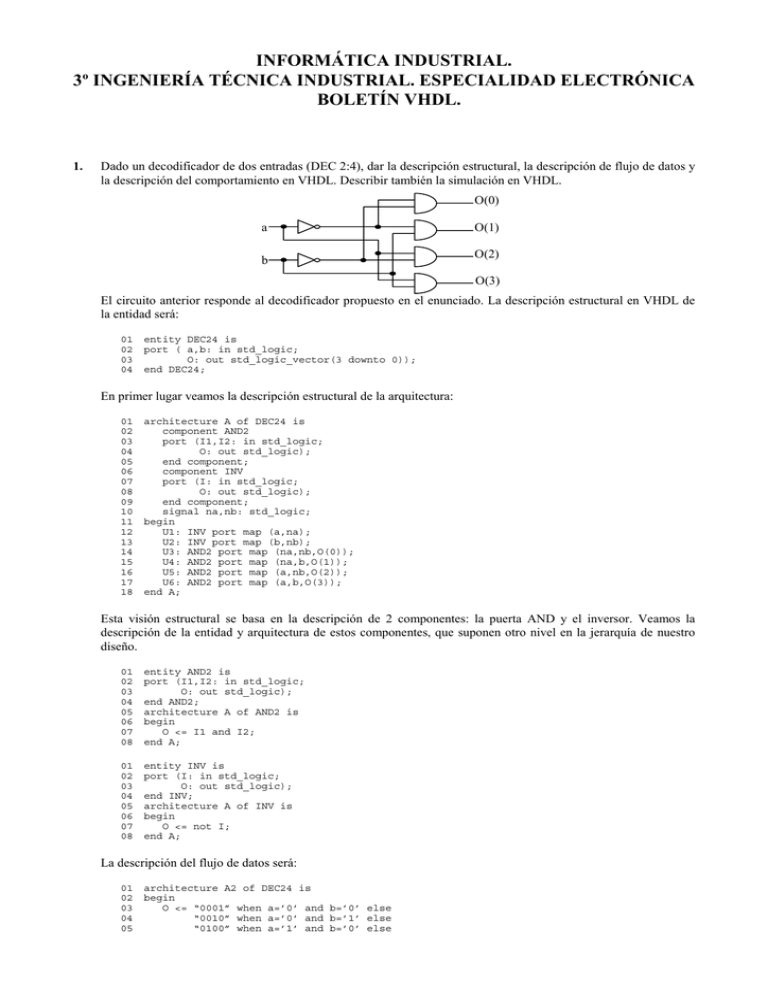

INFORMÁTICA INDUSTRIAL. 3º INGENIERÍA TÉCNICA INDUSTRIAL. ESPECIALIDAD ELECTRÓNICA BOLETÍN VHDL. 1. Dado un decodificador de dos entradas (DEC 2:4), dar la descripción estructural, la descripción de flujo de datos y la descripción del comportamiento en VHDL. Describir también la simulación en VHDL. O(0) a b O(1) O(2) O(3) El circuito anterior responde al decodificador propuesto en el enunciado. La descripción estructural en VHDL de la entidad será: 01 02 03 04 entity DEC24 is port ( a,b: in std_logic; O: out std_logic_vector(3 downto 0)); end DEC24; En primer lugar veamos la descripción estructural de la arquitectura: 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 architecture A of DEC24 is component AND2 port (I1,I2: in std_logic; O: out std_logic); end component; component INV port (I: in std_logic; O: out std_logic); end component; signal na,nb: std_logic; begin U1: INV port map (a,na); U2: INV port map (b,nb); U3: AND2 port map (na,nb,O(0)); U4: AND2 port map (na,b,O(1)); U5: AND2 port map (a,nb,O(2)); U6: AND2 port map (a,b,O(3)); end A; Esta visión estructural se basa en la descripción de 2 componentes: la puerta AND y el inversor. Veamos la descripción de la entidad y arquitectura de estos componentes, que suponen otro nivel en la jerarquía de nuestro diseño. 01 02 03 04 05 06 07 08 entity AND2 is port (I1,I2: in std_logic; O: out std_logic); end AND2; architecture A of AND2 is begin O <= I1 and I2; end A; 01 02 03 04 05 06 07 08 entity INV is port (I: in std_logic; O: out std_logic); end INV; architecture A of INV is begin O <= not I; end A; La descripción del flujo de datos será: 01 02 03 04 05 architecture A2 of DEC24 is begin O <= “0001” when a=’0’ and b=’0’ else “0010” when a=’0’ and b=’1’ else “0100” when a=’1’ and b=’0’ else 06 07 “1000”; end A2; Y la descripción del comportamiento será: 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 architecture A3 of DEC24 is begin process (a,b) variable c: std_logic_vector(1 downto 0); begin c(1):= a; c(0):= b; case c is when “00” => O <= “0001”; when “01” => O <= “0010”; when “10” => O <= “0100”; when others => O <= “1000”; end case; end process; end A3; Por último, la descripción VHDL de la simulación será: 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 2. entity sim_dec24 is end sim_dec24; architecture A of sim_dec24 is component DEC24 port (a,b: in std_logic; O : out std_logic_vector(3 downto 0)); end component; signal a,b: std_logic; signal odec: std_logic_vector (3 downto 0); begin D: DEC24 port map (a,b,odec); S: process begin a<=’0’; b<= ‘0’; wait for 20 ns; a<= ‘0’; b<= ‘1’; wait for 20 ns; a<= ‘1’; b<= ‘0’; wait for 20 ns; a<= ‘1’; b<= ‘1’; wait for 20 ns; end process; end A; Describir en VHDL y por comportamiento, una memoria de 8 posiciones de 8 bits de ancho usando el decodificador del apartado anterior. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 Entity memoria is Port (address: in bit_vector (2 downto 0); Data: inout bit_vector (7 downto 0); WR: in bit; CS: in bit); end memoria; architecture A of memoria is component DEC24 port (a,b: in std_logic; O: out std_logic_vector (3 downto 0)); end component; signal a1,a2,b1,b2: std_logic; signal sel: std_logic_vector (7 downto 0); type mem is array (integer range <>) of std_logic_vector (7 downto 0); signal r: mem (0 to 7); begin a1 <= not address(2) and address(1); b1 <= not address(2) and address(0); D1: DEC24 port map (a1,b1,sel(3 downto 0)); a2 <= address(2) and address(1); b2 <= address(2) and address(0); D2: DEC24 port map (a2,b2,sel(7 downto 4)); UC: process (sel,WR,CS,Data) begin if CS=’1’ then if WR=’1’ then –- Escribir en RAM case sel is when “00000001” => r(0) <= Data; when “00000010” => r(1) <= Data; when “00000100” => r(2) <= Data; when “00001000” => r(3) <= Data; when “00010000” => r(4) <= Data; when “00100000” => r(5) <= Data; 3. 4. 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 when “01000000” => r(6) <= Data; when others => r(7) <= Data; end case; else case sel is when “00000001” => Data <= r(0); when “00000010” => Data <= r(1); when “00000100” => Data <= r(2); when “00001000” => Data <= r(3); when “00010000” => Data <= r(4); when “00100000” => Data <= r(5); when “01000000” => Data <= r(6); when others => Data <= r(7); end case; end if; end if; end process; end A; 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 architecture A2 of B1P2_memoria is type mem is array(integer range <>) of std_logic_vector (7 downto 0); signal r: mem (0 to 7); begin mem: process (address,WR,CS,Data) begin if CS='1' then if WR='1' then r(conv_integer(address)) <= Data; else Data <= r(conv_integer(address)); end if; end if; end process; end A2; Un elemento C es un circuito secuencial que se aplica en el diseño de sistemas autotemporizados y que cumple la siguiente función: - Si las entradas toman todas el mismo valor, en la salida aparece el valor de las entradas. - En caso contrario la salida mantiene el valor anterior. Dar el código VHDL de dicho elemento y de su simulación. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 Entity elemento_C is Port (a,b: in std_logic; O: out std_logic); end elemento_C; 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 entity sim_C is end sim_C; architecture A of elemento_C is begin process (a,b) variable tmp: std_logic; begin if a=b then tmp := a; end if; O <= tmp; end process; end A; architecture A of sim_C is component elemento_C port (a,b: in std_logic; O: out std_logic); end component; signal I: std_logic_vector (1 downto 0); signal o: std_logic; begin C: elemento_C port map (I(1),I(0),o); B:process begin for j in 0 to 4 loop I <= conv_std_logic_vector (j,2); wait for 20 ns; end loop; end process; end A; Describir en VHDL por comportamiento un biestable tipo D con señal de Enable y de Reset. 01 Entity Dflipflop is 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 5. architecture A of Dflipflop is begin process (CLK,RST) begin if RST=’1’ then Q <= ‘0’; elsif CLK’event and CLK=’1’ then if EN=’1’ then Q <= D; end if; end if; end process; end A; Describir en VHDL por comportamiento un contador de 8 bits, con cuenta ascendente y descendente, enable y reset. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 6. Port (CLK: in std_logic; RST: in std_logic; D: in std_logic; EN: in std_logic; Q: out std_logic); end Dflipflop; Entity cont8 is Port (CLK: in std_logic; RST: in std_logic; EN: in std_logic; UD: in std_logic; O: out std_logic_vector (7 downto 0)); end cont8; architecture A of cont8 is begin process (CLK,RST) variable cnt: integer range 0 to 255; begin if RST=’0’ then cnt := 0; elsif CLK’event and CLK=’1’ then if EN=’1’ then if UD=’1’ then if cnt < 255 then cnt := cnt +1; else cnt := 0; end if; else if cnt >0 then cnt := cnt –1; else cnt := 255; end if; end if; end if; end if; O <= conv_std_logic_vector (cnt,8); end process; end A; Describir en VHDL por comportamiento un registro de desplazamiento a la derecha y a la izquierda no circular, con enable y reset. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 Entity reg is Port (CLK: in std_logic; RST: in std_logic; EN: in std_logic; LR: in std_logic; L,R: in std_logic; O: out std_logic_vector (7 downto 0)); end reg; architecture A of reg is begin process (CLK,RST) variable tmp: std_logic_vector (7 downto 0); begin if RST=’0’ then tmp := (others => ‘0’); elsif CLK’event and CLK=’1’ then if EN=’1’ then if LR=’1’ then -- Left for j in 7 downto 1 loop tmp(j) := tmp (j-1); end loop; tmp(0):= L; else for j in 0 to 6 loop tmp(j) := tmp (j+1); end loop; 28 29 30 31 32 33 34 7. tmp(7):= R; end if; end if; end if; O <= tmp; end process; end A; Supongamos un sistema que convierta una entrada paralela de 8 bits a formato serie con bit de Stara y Stop cada vez que le llega un pulso por una señal LD que indica un nuevo dato en la entrada paralela. Cuando la conversión concluya el sistema activará durante un ciclo de reloj la salida FIN. Se pide: - Dibujar el diagrama de bolas de la máquina de estados que controle la salida serie. - Describir en VHDL el sistema usando como componente el diseño del ejercicio 6. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 Entity B1P7_paralelo_serie is Port (CLK: in std_logic; RST: in std_logic; EN: in std_logic; LD: in std_logic; I: in std_logic_vector (7 downto 0); FIN: out std_logic; O: out std_logic); end B1P7_paralelo_serie; architecture A of B1P7_paralelo_serie is component B1P6_reg Port (CLK: in std_logic; RST: in std_logic; EN: in std_logic; LR: in std_logic; L,R: in std_logic; LD: in std_logic; I: in std_logic_vector (7 downto 0); O: out std_logic_vector (7 downto 0)); end component; type estados is (esperar_LD,bit_start,serializando,pulso_fin); signal estado_actual, proximo_estado: estados; signal LR,L,R,enreg: std_logic; signal rego: std_logic_vector (7 downto 0); signal contador : integer range 0 to 7; begin BREG: B1P6_reg port map (CLK,RST,enreg,LR,L,R,LD,I,rego); BS:process (CLK,RST) begin if RST='0' then estado_actual <= esperar_LD; contador <= 0; elsif CLK'event and CLK='1' then if EN='1' then estado_actual <= proximo_estado; if estado_actual = serializando then contador <= contador +1; else contador <= 0; end if; end if; end if; end process; BC:process (estado_actual,LD,contador) begin LR <= '0'; -- Desplaza a la derecha L <= '0'; 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 8. Describir en VHDL un coprocesador que realice operaciones aritméticas (sumas, restas y multiplicaciones) en punto flotante con palabras de 32 bits. Dar el código de la simulación (no se incluye). 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 9. R <= '0'; FIN <= '0'; case estado_actual is when esperar_LD => if LD='1' then proximo_estado <= bit_start; else proximo_estado <= esperar_LD; end if; enreg <= '0'; O <= '1'; when bit_start => proximo_estado <= serializando; enreg <= '1'; O <= '0'; -- bit de start; when serializando => if contador <7 then proximo_estado <= serializando; else proximo_estado <= pulso_fin; end if; enreg <= '1'; O <= rego (0); when others => proximo_estado <= esperar_LD; enreg <= '1'; O <= '1'; -- bit de stop FIN <= '1'; end case; end process; end A; Entity copro Port (i1,i2: O: out op: in end copro; is in std_logic_vector (31 downto 0); std_logic_vector (31 downto 0); std_logic_vector (1 downto 0)); architecture A of copro is signal a,b,c: integer; begin a <= conv_integer(i1); b <= conv_integer(i2); BP: process (a,b,op) begin case op is when "00" => c <= a+b; when "01" => c <= a-b; when "10" => c <= a*b; when others => c <= a/b; end case; end process; O <= conv_std_logic_vector (c,32); end A; Examen Febrero 2004. (sin diagrama) 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 entity b1p9_FPGA is port( RST: in std_logic; CLK1M: in std_logic; Tec: in std_logic_vector(62 downto 0); CLK: out std_logic; Bot: out std_logic_vector(5 downto 0)); End b1p9_FPGA; architecture A of b1p9_FPGA is Component div_clk20 Port( CLK1M: in std_logic; RST: in std_logic; CLK20: out std_logic); End component; Signal clk20: std_logic; begin U1: div_clk20 port map (CLK1M,RST,clk20); U2: process (CLK1M,RST) variable cnt: integer range 0 to 50; variable ck: std_logic; begin if RST='1' then Cnt:=0; Ck:='0'; elsif CLK1M'event and CLK1M='1' then if cnt = 50 then ck := not ck; 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 cnt := 0; else cnt := cnt +1; end if; end if; CLK <= ck; end process; U3: process (CLK20,RST) variable ntec,n: integer range 0 to 62; begin if RST='1' then bot<=(others =>'0'); n:=0; elsif CLK20'event and CLK20='1' then for i in 0 to 62 loop if tec(i)='1' then ntec:=i; n:=n+1; end if; end loop; if n=1 then bot <= conv_std_logic_vector(ntec+1,6); else bot <= (others => '0'); end if; n:=0; end if; end process; end A; 10. Examen Julio 2004. (sin diagrama) 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 entity b1p10_exjul04 is port (SER : in std_logic; CLK : in std_logic; RST : in std_logic; DONE: out std_logic); end b1p10_exjul04; architecture A of b1p10_exjul04 is type estados is (wait_0,received_0,received_01,received_011); signal estado_actual, proximo_estado: estados; signal contador: integer range 0 to 15; begin BS: process (CLK,RST) Begin if RST='1' then estado_actual <= wait_0; contador <= 0; elsif CLK'event and CLK='1' then estado_actual <= proximo_estado; if estado_actual=received_011 and SER='0' then if contador = 15 then contador <= 0; else contador <= contador +1; end if; end if; end if; end process; BC: process (estado_actual,SER,contador) Begin case estado_actual is when wait_0 => if SER='0' then proximo_estado <= received_0; else proximo_estado <= wait_0; end if; DONE <= '0'; when received_0 => if SER='1' then proximo_estado <= received_01; else proximo_estado <= received_0; end if; DONE <= '0'; when received_01 => if SER='1' then proximo_estado <= received_011; else proximo_estado <= received_0; end if; DONE <= '0'; when received_011 => if SER='0' then if contador=15 then DONE <= '1'; else DONE <= '0'; end if; else DONE <= '0'; end if; proximo_estado <= wait_0; end case; end process; end A; 11. Examen Septiembre 2004. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 entity b1p11_exsep04 is port (SER1 : in std_logic; SER2 : in std_logic; CLK : in std_logic; RST : in std_logic; DONE: out std_logic); end b1p11_exsep04; architecture A of b1p11_exsep04 is type estados is (waits1_0,receiveds1_0,waits2_1,receiveds2_1); signal estado_actual, proximo_estado: estados; signal contador: integer range 0 to 7; begin BS: process (CLK,RST) Begin if RST='1' then estado_actual <= waits1_0; contador <= 0; elsif CLK'event and CLK='1' then estado_actual <= proximo_estado; if estado_actual=receiveds2_0 and SER2='0' then if contador = 7 then contador <= 0; else contador <= contador +1; end if; end if; end if; end process; BC: process (estado_actual,SER1,SER2,contador) Begin case estado_actual is when waits1_0 => if SER1='0' then proximo_estado <= receiveds1_0; else proximo_estado <= waits1_0; end if; DONE <= '0'; when receiveds1_0 => if SER1='1' then proximo_estado <= waits2_1; else proximo_estado <= receiveds1_0; end if; DONE <= '0'; when waits2_1 => if SER2='1' then proximo_estado <= receiveds2_1; else proximo_estado <= waits2_1; end if; DONE <= '0'; when receiveds2_1 => if SER2='0' then if contador=7 then DONE <= '1'; else DONE <= '0'; end if; proximo_estado <= waits1_0; else DONE <= '0'; proximo_estado <= receiveds2_1; end if; end case; end process; end A; 12. Examen Diciembre 2004. 01 02 03 04 05 06 07 08 09 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_logic_unsigned."+"; -- Esta operación se usa para sumar -- un std_logic_vector y un inmediato entity b1p12_exdic04 is port (SER : in std_logic; CLK : in std_logic; RST : in std_logic; DONE: out std_logic; DATA: out std_logic_vector(6 downto 0)); end b1p12_exdic04; architecture A of b1p12_exdic04 is type estados is (wait_0,received_0,received_01,received_011); signal estado_actual, proximo_estado: estados; signal contador: std_logic_vector (6 downto 0); begin BS: process (CLK,RST) Begin if RST='1' then estado_actual <= wait_0; contador <= (others => '0'); elsif CLK'event and CLK='1' then estado_actual <= proximo_estado; 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 if estado_actual=received_011 and SER='1' then contador <= contador + 1; end if; end if; end process; DATA <= contador; BC: process (estado_actual,SER,contador) Begin case estado_actual is when wait_0 => if SER='0' then proximo_estado <= received_0; else proximo_estado <= wait_0; end if; DONE <= '0'; when received_0 => if SER='1' then proximo_estado <= received_01; else proximo_estado <= received_0; end if; DONE <= '0'; when received_01 => if SER='1' then proximo_estado <= received_011; else proximo_estado <= received_0; end if; DONE <= '0'; when received_011 => if SER='0' then DONE <= '0'; proximo_estado <= received_0; else DONE <= '1'; proximo_estado <= wait_0; end if; end case; end process; end A;