procesadores avanzados - Departamento de Tecnología Electrónica

Anuncio

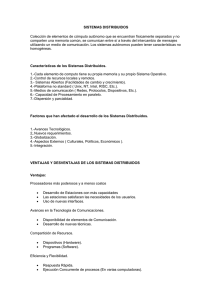

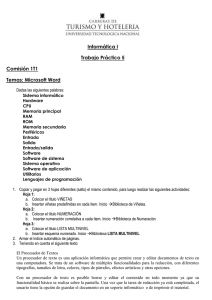

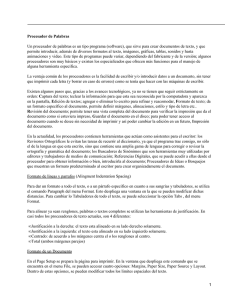

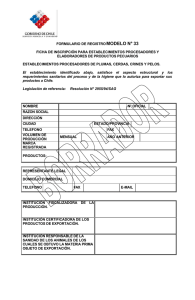

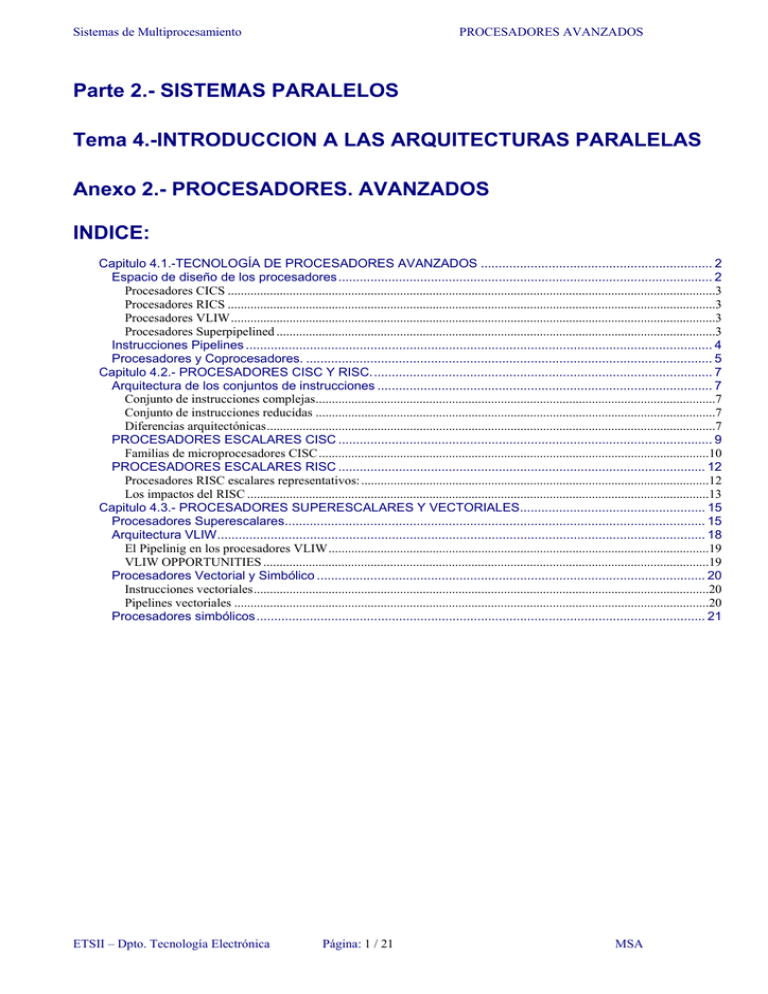

Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Parte 2.- SISTEMAS PARALELOS Tema 4.-INTRODUCCION A LAS ARQUITECTURAS PARALELAS Anexo 2.- PROCESADORES. AVANZADOS INDICE: Capitulo 4.1.-TECNOLOGÍA DE PROCESADORES AVANZADOS ................................................................. 2 Espacio de diseño de los procesadores......................................................................................................... 2 Procesadores CICS ......................................................................................................................................................3 Procesadores RICS ......................................................................................................................................................3 Procesadores VLIW.....................................................................................................................................................3 Procesadores Superpipelined .......................................................................................................................................3 Instrucciones Pipelines ................................................................................................................................... 4 Procesadores y Coprocesadores. .................................................................................................................. 5 Capitulo 4.2.- PROCESADORES CISC Y RISC................................................................................................ 7 Arquitectura de los conjuntos de instrucciones .............................................................................................. 7 Conjunto de instrucciones complejas...........................................................................................................................7 Conjunto de instrucciones reducidas ...........................................................................................................................7 Diferencias arquitectónicas..........................................................................................................................................7 PROCESADORES ESCALARES CISC ......................................................................................................... 9 Familias de microprocesadores CISC........................................................................................................................10 PROCESADORES ESCALARES RISC ....................................................................................................... 12 Procesadores RISC escalares representativos: ...........................................................................................................12 Los impactos del RISC ..............................................................................................................................................13 Capitulo 4.3.- PROCESADORES SUPERESCALARES Y VECTORIALES.................................................... 15 Procesadores Superescalares...................................................................................................................... 15 Arquitectura VLIW......................................................................................................................................... 18 El Pipelinig en los procesadores VLIW.....................................................................................................................19 VLIW OPPORTUNITIES .........................................................................................................................................19 Procesadores Vectorial y Simbólico ............................................................................................................. 20 Instrucciones vectoriales............................................................................................................................................20 Pipelines vectoriales ..................................................................................................................................................20 Procesadores simbólicos.............................................................................................................................. 21 ETSII – Dpto. Tecnología Electrónica Página: 1 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Capitulo 4.1.-TECNOLOGÍA DE PROCESADORES AVANZADOS Vamos a estudiar la arquitectura de los modernos procesadores: • CISC, • RISC, • Superescalares, • VLIW, • Super-pipelined, • Vectoriales y • Simbólicos. Los procesadores escalares y vectoriales se emplean en cálculo numérico y los simbólicos en aplicaciones de IA. Espacio de diseño de los procesadores Representamos en una grafica la frecuencia de señal de reloj y los ciclos por instrucción (CPI) para varios modelos de mismas familias y para familias diferentes. CPI Ciclos por instrucción 20 10 Escalar CISC 5 Espacio de diseño de la mayoría de los futuros procesadores Superpipelined Escalar RISC 2 1 0,5 VLIW 0,2 Superescalar RISC Superordenador Vectorial 0,1 Ciclos de reloj MHz 5 10 20 50 100 200 500 1000 Como la tecnología de implementación en los procesadores varia muy rápidamente, la señal del reloj varia gradualmente desde valores mas pequeños a valores mayores. Otra cuestión a observar es que los fabricantes de procesadores están tratando de reducir el numero de CPI (Ciclos por Instrucción) usando HW y SW adecuado. Esta grafica representa la década hasta los 95, según vaya avanzando la tecnología, algunas de las zonas se desplazaran hacia la zona derecha inferior. ETSII – Dpto. Tecnología Electrónica Página: 2 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Procesadores CICS Los procesadores convencionales como, Intel 486, Motorota 68040, VAX 8600, IBM 390,... se clasifican en la familia de arquitecturas denominada como de computación de conjuntos de instrucciones complejas CISC (Complex-Instruction-Set Computing). Trabajan con frecuencias de reloj de 33 a 50 MHz. Actualmente estas velocidades de reloj están por encima del GHz. Con control programado, cada instrucción maquina es interpretada por un microprograma localizado en una memoria del CI del procesador. Las instrucciones compuestas son decodificadas internamente y ejecutadas con las microinstrucciones que están almacenadas en la ROM interna. Estos procesadores tienen un valor de CPI entre 1 y 20. Procesadores RICS Otra familia a describir será la RISC, computación de conjuntos de instrucciones reducidas (Reduced-InstructionSet Computing), por ejemplo, los Intel i860, SPARC, MIPS R3000, IBM RS-6000, ..... Estos poseen una frecuencia de reloj mas elevada entre 20 y 120 MHz por su tecnología de implementación y consiguen con el uso de un control por HW reducir el numero de CPI de 1 o 2. Una clase especial de procesadores RISC son los procesadores superescalares, que permiten la ejecución de múltiples instrucciones en el mismo ciclo. El valor de CPI de estos procesadores lógicamente, debe de ser menor que en un procesador RISC genérico. Su frecuencia de reloj, eso si, se encuentra en el mismo rango que la de los procesadores RISC. Procesadores VLIW Los procesadores de arquitectura VLIW (Very Long Instruction Word) utilizan unidades aun mas funcionales que en el caso de los procesadores superescalar. Con esto, el valor de CPI en estos procesadores puede ser aun mas reducido. Debido al uso de instrucciones muy largas (256 a 1024 bits) la mayoría de los procesadores VLIW se han implementado con control microprogramador. La frecuencia de reloj es mas lenta por el empleo de memoria de solo lectura (ROM) Un gran numero de ciclos de micro código de acceso puede ser necesitado para algunas instrucciones. Procesadores Superpipelined Los procesadores Superpipelined poseen relojes multifase con una mucho mas elevada frecuencia de reloj, que puede ir de 100 a 500 MHz. Lo que ocurre es que el rango de CPI es también muy grande a pesar de que se este tipo de procesadores se usa paralelamente con multi-instrucciones. Las supercomputadoras vectoriales usan este tipo de procesador superpipelined y usan múltiples unidades funcionales para realizar operaciones con escalares y vectores. El numero efectivo de CPI usado en una supercomputadora debe de ser muy bajo, lo ideal, es que este posicionado en la esquina inferior derecha de la grafica. Pero al intentar alcanzar esta posición, el coste se incrementa considerablemente. ETSII – Dpto. Tecnología Electrónica Página: 3 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Instrucciones Pipelines El ciclo de ejecución de una instrucción incluye cuatro fases: lectura, descodificación, ejecución y escritura. Estas fases se suelen realizar por una instrucción pipeline como se ve en la figura. Instrucciones sucesivas Ejecución pipeline en un procesador escalar Ciclos de reloj Así podemos modelar un procesador de instrucciones con esta estructura simple compuesta por pipelines. Usaremos esta estructura pipeline para la explicación de los siguientes tipos de procesadores. La pipeline, como una cadena de ensamblaje, recibe instrucciones sucesivas de sus entradas y las ejecuta secuencialmente, con solapamiento según las instrucciones fluyan a través de ella. Un ciclo de pipeline se define como el tiempo necesario para cada fase para completar su operación, asumiendo igual retraso en cada fase. Las características básicas de esta estructura pipeline son las siguientes: 1. Ciclo de instrucción simple pipeline: El periodo de reloj para una fase de la instrucción pipeline. Se considera que todas las fases tiene el mismo tiempo. 2. Latencia de ejecución de instrucciones: es el tiempo en ciclos requerido entre la gestión de 2 instrucciones. 3. Relación de instrucciones: es el número de instrucciones procesadas por ciclo. Este parámetro también se denomina grado de una computadora superescalar. 4. Latencia de operación, según las operaciones sean simples, como por ejemplo sumas, cargas, almacenamientos, movimientos..... o complejas, requiriendo una latencia mayor, operaciones complejas pueden se la división, perdidas de cache. Las latencias, en ambos casos se miden en número de ciclos. 5. Conflicto de recursos, esto se refiere a la situación en la que 2 o mas instrucciones necesitan usar la misma unidas funcional al mismo tiempo. Un procesador escalar básico se define como una maquina con una instrucción gestionada por ciclo, con latencia 1 para una operación simple. La instrucción pipeline puede ser totalmente utilizada si instrucciones sucesivas pueden entrar continuamente en un ratio de una por ciclo, como se ve en la figura anterior. La latencia puede ser mayor de un ciclo por varias razones. Si por ejemplo esta latencia es 2 ciclos por instrucción, la tubería puede estar infrautilizada. Instrucciones sucesivas Ejecución pipeline en 2 ciclos por instrucción ETSII – Dpto. Tecnología Electrónica Página: 4 / 21 Ciclos de reloj MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Otra situación de infrautilización de pipeline es cuando el ciclo de pipeline es doblado combinado fases. Las fases de lectura y descodificación se combinan en una única fase de pipeline y las operaciones de ejecución y escritura se combinan en otra fase. Instrucciones sucesivas Ejecución pipeline en 2 ciclos por instrucción Ciclos de reloj Procesadores y Coprocesadores. El procesador central de un ordenador se denomina CPU - Unidad Central de Procesamiento. DMA ( Acceso Directo a Memoria) Memoria principal Bus Memoria Procesador Enteros ALU Subsistema de I/O Cache Unidad Coma Flotante Almacenamiento Masivo ( Discos, Cintas,......) CU Usuarios CPU CPU con unidad de coma flotante Esta CPU es esencialmente un procesador escalar, el cual esta compuesto por múltiples unidades funcionales, como puedan ser, principalmente, un acelerador de coma flotante y la unidad aritmético lógica (ALU), entre otros. La unidad de coma flotante puede ser construida en un coprocesador que estará conectado a la CPU. ETSII – Dpto. Tecnología Electrónica Página: 5 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS DMA ( Acceso Directo a Memoria) Memoria principal Instrucciones y Datos Datos Subsistema de I/O CPU Coprocesador Almacenamiento Masivo ( Discos, Cintas,......) Instrucciones Usuarios CPU con un coprocesador Este coprocesador ejecuta operaciones según se lo ordene la CPU. El coprocesador puede ser un acelerador de coma flotante que ejecute instrucciones escalares, un procesador vectorial que ejecute operaciones vectoriales o un procesador de señales digitales (DSP), o un procesador LISP ejecutando programas AI. Los coprocesadores no pueden llevar a cabo operaciones de I/O. Coprocesador Intel 8087 Intel 80287 Intel 387 DX Intel i486 Motorota MC68882 Weitek 3167 Weitek 4167 Procesador Intel 8086 / 8088 Intel 80286 Intel 386 DX Intel i486 ( incluido en el chip) Motorota MC68020 / 68030 Intel 386 DX Intel i486 Características del coprocesador 5 MHz -- 70 ciclos para la suma y 700 ciclos para lógica 12,5 MHz -- 30 ciclos para la suma y 264 ciclos para lógica 33 MHz -- 12 ciclos para la suma y 210 ciclos para lógica 33 MHz -- 8 ciclos para la suma y 171 ciclos para lógica 40 MHz -- 56 ciclos para la suma y 574 ciclos para lógica 33 MHz -- 6 ciclos para la suma y 365 ciclos para lógica 33 MHz -- 2 ciclos para la suma. La tabla nos muestra una lista de algunos pares procesador/coprocesador que se han desarrollado para aumentar la velocidad de las operaciones numéricas. Comentar finalmente que los coprocesadores no pueden ser usados de manera individual. El procesador y el coprocesador operan en relación y de manera compatible, se puede decir que trabajan de manera que tenemos un procesador “amo” y el resto son procesadores “esclavos”. Eso si, por ciertas razones, un procesador esclavo, puede ser mas potente que su “host”. ETSII – Dpto. Tecnología Electrónica Página: 6 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Capitulo 4.2.- PROCESADORES CISC Y RISC. Arquitectura de los conjuntos de instrucciones El conjunto de instrucciones en una computadora especifica son los comandos primitivos y las instrucciones de maquina que el programador puede usar a la hora de programar la máquina. La complejidad de estos conjuntos de instrucciones puede venir determinada por los formatos de datos, de instrucciones, métodos de direccionamiento y mecanismos de flujo de control, entre otros. Por la experiencia en diseño de procesos, 2 arquitecturas han predominado: CISC y RISC. Conjunto de instrucciones complejas En las primeras épocas de la computación, la mayoría de las computadoras trabajaban con conjuntos de instrucciones que eran relativamente sencillas. La razón de esto era que el HW era muy caro. A lo largo de la evolución de las computadoras en las ultimas 3 décadas, el precio del HW ha bajado muchísimo, y el coste del SW ha ido subiendo gradualmente. El resultado de esto es que una o mas funciones han sido implementadas en el HW, haciendo así el conjunto de instrucciones mucho mas grande y complejo. Un conjunto de instrucciones normal para una arquitectura CISC contiene aproximadamente de 125 a 350 instrucciones, usando formatos variables de instrucción y formatos de datos y un conjunto de 8 a 24 registros de propósito general (GPRs). Conjunto de instrucciones reducidas Después de 2 décadas de uso de procesadores CISC, los usuarios de computadoras se dieron cuenta de que solamente el 25% de las instrucciones de un conjunto complejo de instrucciones son usados frecuentemente mas de un 95% del tiempo. Esto implica que el 75% de las instrucciones que soporta el HW no son usadas mas que rara vez. ¿Por que entonces debemos de gastar valiosa área de Chip para funciones que se ejecutan muy raramente?. Con instrucciones elaboradas de baja frecuencia, que demanda grandes micro-códigos necesarios para ejecutarlos, puede ser mas ventajoso el eliminarlas totalmente del HW y crear una SW que se ocupe de implementarlas. Aun cuando este SW va a ser mas lento, el resultado va a ser positivo debido a la escasa frecuencia de aparición y uso. El incluir instrucciones que se usan raramente en este SW, va a liberara área de Chip, lo que hará que podamos construir procesadores RISC mas potentes. Un conjunto de instrucciones normal RISC contiene menos de 100 instrucciones con un formato de 32 bits. Solamente se usan de 3 a 5 modos de direccionamiento, la mayoría de las instrucciones son basadas en registro, el acceso a memoria se hace solamente por lectura/almacenamiento. Diferencias arquitectónicas Describimos las diferencias en la arquitectura de los procesadores CISC y RISC. En la figura se representa gráficamente la diferencia entre un procesador CISC y uno RISC. Dirección de datos e instrucciones. CU Memoria de control microprogramado Cache Memoria principal Arquitectura CICS con control micro-programado y cache unificado ETSII – Dpto. Tecnología Electrónica Página: 7 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS CU de control por HW Dirección de datos Cache de Datos Cache de Instrucciones Memoria principal Arquitectura RICS con control por HW y cache para Instrucciones y Datos Estas diferencias no se van a mantener en el futuro, porque los procesadores que aparezcan van a contener elementos y características de ambos tipos. La arquitectura CISC convencional usa un cache unificado para gestionar datos e instrucciones. Con esto, deben de compartir el mismo camino datos/instrucciones. En un procesador RISC, se usan caches separados para datos e instrucciones, con diferentes modelos de acceso. Como siempre, existen excepciones y por poner un ejemplo, existen procesadores CISC que usan códigos split El uso de control micro-programado se encuentra el los CISC tradicionales, y el control por HW puede ser encontrado en la mayoría de los RISC. En los primeros CISC, se necesitaba memoria de control ROM, lo que hacia mas lenta la ejecución. Los CISC modernos usan también control por HW. Esto quiere decir que los split caches y controles HW no se usan solamente en las maquinas RISC. El uso del control por HW reducirá efectivamente el numero de CPIs a una instrucción por ciclo si el pipelining se mantiene en estado optimo. Algunos CISC usan caches split y control por HW. Arquitectura característica Tamaño del set de instrucciones y formato de las instrucciones Modos de direccionamiento Registros de propósito general y modelos de cache Velocidad de reloj y CPI Control de CPU CICS RISC Gran conjunto de instrucciones con varios formatos. 16 – 64 bits por instrucción. Pequeño conjunto de instrucciones con formato fijo de 32 bits. La mayor parte de las instrucciones basadas en registros. Limitado a 3 – 5 12 – 24 8 – 24 GPRs Cache unificada de instrucciones y datos 1992 : 33 – 50 MHz con CPI entre 2 y 15 Micro-programado usando ROM, actualmente por HW 32 – 192 GPRs Cache individuales para instrucciones y datos 1993 : 50 – 150 MHz con CPI < 1,5 Control por HW El gran numero de instrucciones usados en un procesador CISC es el resultado del uso de instrucciones de formato variable y del uso de mas de una docena de modos de direccionamiento. Con pocos GPRs, muchas mas instrucciones acceden a la memoria para realizar operaciones. El numero de CPI entonces es bastante elevado, como resultado de los grandes micro-códigos usados para controlar la ejecución de algunas de las instrucciones complejas. En el caso de los RISC se usan instrucciones de 32 bits que son, predominantemente, basadas en registros. Con unos pocos y simples modos de direccionamiento, el ciclo de acceso a memoria se divide en operaciones de acceso pipelined que incluirán el uso de caches y registro de trabajo. Usando un registro de archivos grande, y caches separados para datos e instrucciones se nos beneficiara el direccionamiento interno de datos y se elimina el almacenamiento innecesario de datos intermedios. Con control por HW, el numero de CPI se reduce a 1 para la mayoría de las operaciones RISC. ETSII – Dpto. Tecnología Electrónica Página: 8 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS PROCESADORES ESCALARES CISC El procesador escalar, en los procesadores mas simples, ejecuta instrucciones usando operandos de punto fijo. Procesadores escalares mas potentes ejecutan operaciones de alta integración y operaciones en coma flotante. Un procesador escalar moderno posee ambas unidades de enteros y de coma flotante el la misma CPU. DMA ( Acceso Directo a Memoria) Memoria principal Bus Memoria Procesador Enteros ALU Subsistema de I/O Cache Unidad Coma Flotante Almacenamiento Masivo ( Discos, Cintas,......) CU Usuarios CPU CPU con unidad de coma flotante En el caso ideal, un procesador CISC debe de tener las mismas prestaciones a las que tendría un procesador escalar de las mismas características. Instrucciones sucesivas Ejecución pipeline en un procesador escalar Ciclos de reloj Lo que ocurre es que normalmente el procesador suele estar underpipelined. Las causas de esto pueden ser la dependencia de datos entre instrucciones, penalizaciones en la ramificación y otros conflictos, como se vera mas adelante. Instrucciones sucesivas Ejecución pipeline en 2 ciclos por instrucción ETSII – Dpto. Tecnología Electrónica Página: 9 / 21 Ciclos de reloj MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Otro caso que puede darse es causado por usar un ciclo de reloj que es mayor que la latencia de operación.. Instrucciones sucesivas Ciclos de reloj Ejecución pipeline en 2 ciclos por instrucción Finalmente decir que el mayor problema para el diseñador va a ser la reducción del ciclo de reloj para conectar este a la latencia de operaciones simples. Esto se resuelve en la arquitectura RISC. Vemos ahora como las técnicas RISC, superescalar y superpipelining pueden ser aplicadas para mejorar las prestaciones Consola Bus de consola Subsistema I/O Bus de direcciones Enteros ALU Unidad de Instrucciones ( 16 GRPs) Unidad Coma Flotante Bus de operandos Cache 16 KB Memoria de control Control de Memoria y sistemas de I/O Bus de memoria Almacenamiento Masivo ( Discos, Cintas,......) Memoria principal Bus de escritura CPU del VAX 8600 con arquitectura típica de procesador CICS La CPU de este ejemplo contiene dos unidades funcionales para ejecución e instrucciones de coma flotante. Tenemos un cache que se usa para instrucciones y datos. Tenemos 16 GPRs en la unidad de instrucciones. El pipelinig de instrucciones se ha construido con 6 etapas, como en la mayoría de las maquinas CICS. El CPI de las instrucciones varia entre 2 y 20 ciclos, debido al empleo de largas secuencias de instrucciones y operaciones de control por HW. Familias de microprocesadores CISC Procesadores Intel : • 8 bits : 8008, 8080, 8085 • 16 bits : 8086, 8088,80186,80286 • 32 bits : 80386, 80486, 80586 Procesadores Motorola : • 8 bits :6800 • 16 bits : 68000 • 32 bits : 68020, 68030, 68040. ETSII – Dpto. Tecnología Electrónica Página: 10 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Bus de Instrucciones ATC de Instrucciones Cache de Instrucciones Bus de Direcciones ( 32 bits) D. I. Buscar Inst Controlador de Instrucciones Conversor Decodifica Ejecución Bus de Controladores Unidad de memoria de Instrucciones Calcula DE Bus de Datos e Instrucciones ( 32 bits) Busca DE Unidad de memoria de Datos Escritura Unidad de Punto Flotante Ejecución Controlador de Datos Escritura Unidad de Enteros ATC de Datos Cache de Datos D.D. Bus de Señales de Control Bus de Datos Arquitectura del microprocesador Motorola MC68040 Cache de 4 KB de datos Cache de 4 KB de instrucciones 100 instrucciones con 16 registros multi-propósito Cache de traslación de direcciones ATC. Unidad de integración organizada en una pipeline de 6 etapas : • Buscar Instrucciones. • Decodificación • Calculo de dirección efectiva • Buscar dirección efectiva • Ejecución • Escritura La unidad de punto flotante esta constituida en tres etapas ETSII – Dpto. Tecnología Electrónica Página: 11 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS PROCESADORES ESCALARES RISC El procesador genérico RISC se denomina RISC escalar, porque ha sido diseñado para ejecutar una instrucción por ciclo, como ocurría en el procesador escalar. En teoría, ambos procesadores RISC y CISC deberían de tener prácticamente el mismo rendimiento, si trabajaran con la misma señal/frecuencia de reloj e igual longitud de programa. Esto no siempre ocurre, porque la arquitectura afecta la calidad y densidad del código generado por los compiladores. El diseño RISC aumenta su potencia colocando algunas de las operaciones usadas con menos frecuencia en el interior de un Software. La necesidad de un buen compilador es mucho mayor en un procesador RISC que en uno CISC. El paralelismo en el nivel de instrucciones se explota en ambos tipos de procesadores. Procesadores RISC escalares representativos: • Sun SPARC CY7C601 • Intel i860 • Motorota 88100 • AMD 29000 entre las características a destacar : • Conjunto de instrucciones de 51 a 124 instrucciones básicas • Instrucciones de 32 bits • Numero de registros entre 32 y 192 • Unidad de punto flotante en chip en los modelos i860 y M88100 Dirección FI Registro estático Dato Resultados FPP Buffer direcciones de instrucciones ( 2 x 64) Procesador de Punto Flotante Pipelined de 64 bits Fichero registros de datos en Punto Flotante ( 32 x 32) Cola de Punto Flotante ( 3 x 64) Dirección instrucción Operandos FP Control Fichero Registros Instrucciones FP Unidad de Control Instrucciones en Punto Flotante Control FP Arquitectura del procesador Sun Microsystems Sparc CY7C602 ( Unidad de coma flotante esperada en 2 chips) Este procesador ejecuta con un conjunto de 32 registros enteros de 32 bits, 8 de estos registros son registros globales, compartidos por todos los procesos, los 24 restantes van asociados solamente con un procedimiento. Cada registro esta dividido en 3 partes, Entradas (Ins), salidas (Outs) y Locales. ETSII – Dpto. Tecnología Electrónica Página: 12 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Dirección externa de 32 bits Unidad de Gestión de Memoria Cache Instrucciones 4 KB Cache datos 8 KB Dirección Instrucciones Dirección Datos Datos Cache 128 bits Instrucción FP Datos externos 64 bits 64 Núcleo Instrucción 32 Unidad de Control del Bus 32 32 32 Unidad Entero RISC Unidad de Control de Punto Flotante Registros del Nucleo Registros FP 64 Dest Src1 Src2 64 64 Ki T Unidad Grafica Enlaces de registros Unidad Sumadora Pipelined Kr Unidad Multiplicadora Pipelined Arquitectura del procesador i860 Es un procesador RISC de 64 bits, fabricado en chips con mas de 1 millón de transistores Alcanza hasta los 80 Mflops Dispone de 9 unidades funcionales conectadas Ejecuta 82 instrucciones: • • • • 42 RISC enteros 24 Punto Flotante 10 Graficas 6 Operaciones de pseudo-ensamblador Buses internos y externos de direcciones de 32 bits Bus de datos internos de 64 bits Cache de datos compuesto por una memoria asociativa de 2 vías y 8 KB, transmite 128 bits por ciclo de reloj La Unidad de Gestión de Memoria soporta 4 KB para páginas de memoria virtual. Los impactos del RISC El debate entre los diseñadores de RISC y CICS ha durado más de 1 década. Los procesadores RISC muestran mejores prestaciones que los CICS si la longitud del programa no se incrementa demasiado. Por la experiencia acumulada se puede decir que en la conversión de un programa CICS a un su equivalente en RSIC se incrementa la longitud del código en un 40 %, debido a que un procesador RISC carece de ciertas instrucciones sofisticas de las que posee un procesador CICS, por supuesto depende del comportamiento del programa y no es generalizable. ETSII – Dpto. Tecnología Electrónica Página: 13 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Este incremento de la longitud del código es mucho más pequeño que el incremento en la velocidad de reloj y la reducción de CPIs, pero sin embargo este incremento de la longitud de un programa RICS implica mayor tráfico de instrucciones y mayor demanda de memoria. Otro problema de los RISC es causado por el uso de un archivo de registros grande. A pesar de que de un conjunto de registros más grande puede gestionar más resultados intermedios y reducir el tráfico de datos entre la CPU y la memoria, el sistema de decodificación de registros será mas complicado. El mayor tiempo de acceso a registro nos pide una demanda mayor al compilador para realizar las funciones de registro de ventana. Otra desventaja de los RISC se basa en su control por HW, que es menos flexible. Las desventajas del RISC están directamente relacionadas con algunas de sus ventajas. Las diferencias entre las arquitecturas RISC y CISC se han reducido actualmente porque ahora los 2 están siendo implementados con la misma tecnología HW. Los procesadores VAX 9000, Motorota 88100 y Intel i586 han construidos con prestaciones mixtas de ambas arquitecturas. Realmente son las características de la aplicación las que determinan la mejor elección de una arquitectura de procesador. ETSII – Dpto. Tecnología Electrónica Página: 14 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Capitulo 4.3.- PROCESADORES SUPERESCALARES Y VECTORIALES Los procesadores escalares CISC o RISC pueden ser mejorados con una arquitectura superescalar o vectorial. Recordar que los procesadores escalares son aquellos que ejecutan una instrucción por ciclo de maquina. Solamente una instrucción es gestionada por ciclo, y solo podemos esperar a que se complete una operación en la pipeline por ciclo. En un procesador superescalar, se usan pipelines de múltiples instrucciones. Esto implica que múltiples instrucciones se gestionan por ciclo, y se generan múltiples resultados en ese ciclo. Un procesador vectorial ejecuta instrucciones “vector” en arrays de datos. Procesadores Superescalares Los procesadores superescalares están diseñados para explotar el paralelismo en el nivel de instrucciones en los programas del usuario. Solamente se pueden ejecutar en paralelo las instrucciones independientes sin causar un estado de espera. La cantidad de este paralelismo en el nivel de instrucciones varia ampliamente dependiendo del código ejecutado. Pipeline en los procesadores escalares: Instrucciones sucesivas Procesador superescalar de grado m=3 Ciclos de reloj En esta figura se muestra el uso en paralelo de 3 pipelines en un procesador de grado 3. En este sentido, el procesador escalar base, implementado como RISC o CISC tiene un grado m =1. Un procesador superescalar de grado m puede gestionar m instrucciones por ciclo. Para utilizar enteramente este procesador, m instrucciones deben de ser ejecutados en paralelo. Esta situación no tiene porque ser cierta en todos los ciclos de reloj. En ese caso, alguna de las pipelines estará en estado de espera. En un procesador superescalar, la latencia de operación simple requiere solamente un ciclo, como ocurría en el procesador escalar base. Debido a la necesidad de tener un elevado grado de paralelismo en el nivel de instrucciones en el programa, los procesadores superescalares necesitan de un compilador optimizado para explotar el paralelismo. Los procesadores superescalares fueron desarrollados originalmente como una alternativa a los procesadores vectoriales. En teoría, un procesador superescalar debería dar las mismas prestaciones que una maquina con HW vectorial. Una maquina superescalar que tenga coma fija, coma flotante carga y branch todo ello en un mismo ciclo, dará efectivamente el mismo paralelismo efectivo que una maquina vectorial que ejecuta una carga de vector dirigida a un vector suma, con un elemento cargado y añadido por ciclo. ETSII – Dpto. Tecnología Electrónica Página: 15 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Una arquitectura superescalar típica se muestra en la figura: Memoria Instrucciones Fichero Registros Buffer Re-ordenador Cache Instrucciones Decodificador Branch ALU Shifter Load Store Unidad RISC Enteros Unidad RISC Coma Flotante Fichero Registros Buffer Re-ordenador Decodificador ADD Convert MULTI DIV Load Direc. Memoria Instrucciones Store Data Cache Datos Se utilizan múltiples instrucciones pipelines. El cache de instrucciones proporciona múltiples instrucciones por (fetch, traer o leer). El número de instrucciones enviadas a varias unidades funcionales puede variar en cada ciclo. Este numero esta limitado por las dependencias entre datos y los conflictos entre instrucciones que son decodificadas simultáneamente. La unidad de enteros y de punto flotante, se construyen con múltiples unidades funcionales. ETSII – Dpto. Tecnología Electrónica Página: 16 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Existen múltiples buses de datos entre las distintas unidades funcionales. En teoría, todas las unidades funcionales pueden ser usadas si no existen dependencias o conflictos entre ellas durante un ciclo dado. Debido al bajo número de CPI obtenido y a las altas frecuencias de reloj que se consiguen, la mayor parte de los procesadores superescalares sobrepasan con mucho las prestaciones de los procesadores escalares. El numero máximo de instrucciones ejecutadas por ciclo varia de 2 a 5 en estos procesadores. Cache Instrucciones ( 8 KB) Branch Procesor Procesador Coma Fija 32 Almacenamiento y I/O Procesador Coma Flotante 32 64 64 Cache Datos ( 64 KB) 128 128 Memoria Principal ( 8 a 128 MB) Arquitectura IBM RS/6000 Este procesador superescalar es de 1990, tiene 3 unidades funcionales: Branch, Coma Fija y Coma Flotante que pueden trabajar en paralelo. El procesador Branch puede arrancar hasta 5 instrucciones por ciclo, estas incluyen: • 1 instrucción Branch en el procesador Branch • 1 instrucción de punto fijo en el procesador de enteros • 1 instrucción de condicional en el procesador Branch • 1 instrucción de punto flotante en el procesador de coma flotante que cuenta como 2. El RS-6000 esta implementado con control por HW y dispone de buses de 32 y 64 bits de tamaño de palabra. El diseño de este procesador esta optimizado por aplicaciones científicas y de ingeniería que requieren de cálculo numérico intensivo. Ha demostrado también un bien rendimiento en entornos comerciales multiusuario. Otros procesadores superescalares representativos: • Intel i960CA • DEC 21064 ETSII – Dpto. Tecnología Electrónica Página: 17 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Arquitectura VLIW LA arquitectura VLIW (Very Long Instruction Word) se caracteriza por 2 conceptos bien establecidos: • • Procesamiento superescalar Microcódigo horizontal, diferentes campos en 1 instrucción larga suministran código a varias unidades funcionales. Una maquina VLIW tiene palabras de instrucción de cientos de bits de largo. Como se ve en la figura, múltiples unidades funcionales se usan al mismo tiempo en la maquina VLIW. Memoria Principal Fichero Registro Unidad Load Store Unidad ADD FP Unidad ALU Unidad Branch Procesador típico VLIW Todas las unidades funcionales comparten el uso de un gran archivo de registro común. Las operaciones que van a ser realizadas por las unidades funcionales se coordinan en una instrucción VLIW, con 256 o 1024 bits por palabra de instrucción. Load / Store FP Add FP Multiply Branch ------- IntegerALU El concepto VLIW es copiado del microcódigo horizontal. Los diferentes campos de la larga palabra de instrucción llevan los códigos a ser usados por las diferentes unidades funcionales. Los programas escritos en las tradicionales palabras cortas de instrucción (es decir 32 bits) deben de ser compactadas entre si para formar las instrucciones VLIW. Esta compactación del código debe de ser realizada por un compilador que pueda predecir las salidas usando estadísticas del tiempo o heurísticas. ETSII – Dpto. Tecnología Electrónica Página: 18 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS El Pipelinig en los procesadores VLIW La ejecución de instrucciones en un procesador ideal VLIW se ve en la figura. Buscar Escribir Decode Ejecutar 3 Oper. Ejecución en un procesador VLIW de grado m = 3 Ciclos de reloj Cada instrucción especifica múltiples operaciones. Las maquinas VLIW se comportan de similar manera a las maquinas superescalares con tres diferencias principales: 1. La decodificación de las instrucciones VLIW es mas fácil que en el caso de instrucciones superescalar. 2. La densidad de código de la maquina superescalar es mejor cuando el paralelismo a nivel de instrucciones disponible es menor que el explotable por una maquina VLIW. Esto se debe a que el formato fijado VLIW incluye bits para operaciones no ejecutables, mientras que el procesador superescalar gestiona solamente instrucciones ejecutables 3. Una maquina superescalar puede ser compatible en código y objeto con una gran familia de maquinas no paralelas. Por el contrario, una maquina VLIW que explote diferentes cantidades de paralelismo requerirá diferentes conjuntos de instrucciones El paralelismo de instrucciones y el movimiento de datos en una arquitectura VLIW esta completamente especificado a la hora de la compilación. Run time resource scheduling and synchornization son entonces completamente eliminados. Uno puede considerar el procesador VLIW como un caso extremo del procesador superescalar en el cual todas las operaciones independientes aun no demandadas son empaquetadas de manera sincronizada en previsión El valor de CPI de un procesador VLIW puede ser aun menor que el de un procesador superescalar. Por ejemplo la computadora Multiflow trace permite mas de siete operaciones ejecutadas al mismo tiempo con 256 bits por instrucción VLIW. VLIW OPPORTUNITIES En la arquitectura VLIW, se explota el paralelismo aleatoriamente entre operaciones escalares, sin tenerse en cuenta el paralelismo regular o síncrono como en una supercomputadora vectorizada o una computadora SIMD. El éxito en un procesador VLIW depende en gran medida de la eficiencia en la compactación del código. La arquitectura es totalmente incompatible con cualquiera de los procesadores convencionales de propósito general. El paralelismo de instrucciones embebido en el código compactado puede requerir una latencia diferente para ser ejecutado por diferentes unidades funcionales, a pesar de que las direcciones son gestionadas al mismo tiempo. Diferentes implementaciones de arquitecturas VLIW pueden ser no compatibles binariamente unas con las otras. Codificando explícitamente el paralelismo en las instrucciones, el procesador VLIW puede eliminar el HW y SW necesarios para detectar el paralelismo. La principal desventaja de la arquitectura VLIW es su simplicidad en estructura de HW y conjunto de instrucciones. El procesador VLIW se comporta bien en aplicaciones científicas donde el comportamiento del programa es mas predecible. En aplicaciones de propósito general, puede que la arquitectura no trabaje bien. Debido a ser incompatible con los HW y SW convencionales, la arquitectura VLIW no ha entrado en la corriente principal de las computadoras. La necesidad de una compilación especial y una compactación de código ha impedido su aceptación en el mundo comercial. ETSII – Dpto. Tecnología Electrónica Página: 19 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Procesadores Vectorial y Simbólico Por definición, un procesador vectorial es un coprocesador diseñado específicamente para realizar operaciones de computación con vectores. Una instrucción vectorial contiene un gran array de operandos. Los procesadores vectoriales son usados generalmente en supercomputadoras multipipelined. Los procesadores vectoriales pueden construirse con una arquitectura registro a registro o con una arquitectura memoria a memoria. La primera de estas arquitecturas usa instrucciones y archivos de registro de vector, la segunda utiliza instrucciones basadas en la memoria que son mas largas, incluyendo las direcciones de memoria. Instrucciones vectoriales Las instrucciones vector basadas en registros aparecen en la mayoría de los procesadores vectoriales registro a registro como en los superordenadores CRAY. Las operaciones vectoriales, en todos los casos, son realizadas por pipelines, incluyendo pipelines funcionales y pipelines de acceso-memoria. La longitud de los vectores debe de ser la misma en todos los operandos usados en una instrucción vectorial. Los vectores más largos, que excedan la longitud del registro, n, deben de ser segmentados en el tiempo para ajustarse a la longitud del registro. Las operaciones vectoriales basadas en memoria se pueden encontrar en procesadores memoria a memoria. Aquí la longitud del vector no esta limitada por la longitud del registro. Los vectores largos se tratan en una en forma de corriente usando superpalabras, que se obtienen de muchas otras palabras de memoria más cortas. Pipelines vectoriales Las pipelines vectoriales pueden ser utilizadas en cualquier procesador escalar, ya sea superescalar, superpipelined, o ambos. Utilizan la ventaja del paralelismo a nivel lazo abierto Las pipelines vectoriales eliminaran parte del solapamiento del SW en el control de bucles. Por supuesto, la efectividad de un procesador vectorial se basa en la capacidad y optimización de un compilador que pueda “vectorizar” códigos secuénciales para el pipelining vectorial. Instrucciones sucesivas Ejecución pipeline en un procesador escalar Ciclos de reloj Instrucciones sucesivas Ciclos de reloj Ejecución pipeline en un procesador escalar con vectores ETSII – Dpto. Tecnología Electrónica Página: 20 / 21 MSA Sistemas de Multiprocesamiento PROCESADORES AVANZADOS Procesadores simbólicos El procesamiento simbólico ha sido utilizado en múltiples áreas, como puedan ser las de comprobación de teoremas, reconocimiento de modelos, maquinas inteligentes, etc. En estas aplicaciones, los datos y los resultados, las operaciones primitivas, el comportamiento del algoritmo, memoria, I/O y comunicaciones son elementos especiales, elementos arquitectónicos especiales diferentes de los elementos numéricos usados en las computaciones numéricas. Los procesadores simbólicos han sido denominados procesadores Prolog, Lisp o manipuladores simbólicos. Por ejemplo, un programa Lisp puede interpretarse como un conjunto de funciones entre las cuales los datos pasan de función a función. La ejecución concurrente de estas funciones es la base para el paralelismo. En vez de trabajar con datos numéricos, trabajamos con programas lógicos, objetos, listas simbólicas, redes neuronales, pizarras..., etc. Las operaciones primitivas para la inteligencia artificial incluyen: • • • • • • Buscar Comparar Inferencia lógica Unificación Filtrado Operaciones de razonamiento Este tipo de operaciones van a necesitar un conjunto especial de instrucciones conteniendo comparar, unir y operaciones lógicas y simbólicas. En este tipo de operaciones, normalmente no se usan operaciones de coma flotante. El procesador simbólico Lisp 3600 Bus A Registros Procesador Etiquetas Buffer de la Pila Procesador Punto Fijo Instrucción en curso Bus B Selector Operandos Memoria Principal Procesador Coma Flotante Colector de Basura La maquina esta dividida en varia capas. Esto permite almacenar o agrupar para simplificar el conjunto de instrucciones. Ejecuta la mayoría de las instrucciones Lisp en un solo ciclo. ETSII – Dpto. Tecnología Electrónica Página: 21 / 21 MSA