Interfaz digital/analógico al monitor VGA

Anuncio

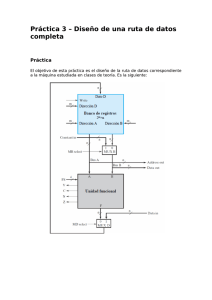

1 Esquema general del módulo de control VGA reloj reset reloj reset Fila(9 bits) VGA RGB Sincr Vert Columna(9 bits) Refresco Interfaz Datos (6 bits) leer Sincr Hor Res1 (4 bits) Reloj: 12.5MHz Teclado Res2 (4 bits) Dato_teclado Clk_teclado Sumador reloj reset 2 Interfaz digital/analógico al monitor VGA Generador VGA digital Conversor D/A Generador VGA analógico 470 ohmios red1 1000 ohmios red red0 75 ohmios 470 ohmios green1 1000 ohmios green green0 470 ohmios 75 ohmios blue1 1000 ohmios blue blue0 75 ohmios 1 3 Temporización VGA horizontal blanking interval 640 muestras (pixels) 0.7 V (máximo brillo) líneas de intensidad analógicas (rojo, verde y azul) 0 V (negro) 31.77 µs 25.17 µs (max) 6.6 µs (min) 0.94 µs (min) 3.77 µs 1.89 µs (min) sincronismo horizontal comienzo de línea final de línea vertical blanking interval 480 líneas 0.7 V (máximo brillo) líneas de intensidad analógicas (rojo, verde y azul) 0 V (negro) 16.784 ms 15.25 ms (max) 1.534 ms (min) 64 µs 0.45 ms (min) 1.02 ms (min) sincronismo vertical 4 Generación de pixels y sincronismo clk = 12.5 MHz tciclo = 80 ns ~ 2 muestras/ciclo líneas de intensidad digitales (rojo, verde y azul) 11 (máximo brillo) 00 (negro) 397 ciclos 314 ciclos (max) 12 ciclos (min) 83 ciclos (min) 47 ciclos 24ciclos (min) sincronismo horizontal líneas de intensidad digitales (rojo, verde y azul) en exceso Memoria de refresco: 2 bits/color · 3 colores/pixel · 314 pixels/linea · 480 líneas/frame = 904320 bits/frame = 113040 bytes/frame = 111 Kb/frame 11 (máximo brillo) 00 (negro) 528 líneas 480 líneas (max) 14 líneas (min) 48 líneas (min) 2 líneas 32 líneas (min) sincronismo vertical 2 5 Pantalla 2 dígitos 7 segmentos 314 puntos 40 40 480 líneas 140 175 275 240 440 6 Esquema refresco Contador columna barrido 0-396 reloj Hsyn 325<Columna<373 Columna Columna=396 Columna Columna>313 o Fila>479 Leer blanking Contador línea barrido 0-527 Vsyn RGB Fila Fila 493<Fila<496 Datos and 3 7 Esquema Interfaz reloj reset 0 Fila(9 bits) 1 5 6 Columna(9 bits) ColorRojo= ((Fila==40) & (39<Columna<141) & Res1(0)) Or Datos (6 bits) ((Fila==240) & (39<Columna<141) & ColorRojo Res1(6)) ........... Datos=Leer&(Rojo lee ............ *ColorRojo+Azul*Not r (ColorRojo)) To 7 seg 2 4 3 To 7 seg Res1 (4 bits) Res2 (4 bits) 8 Memorias Memoria Memoria de refresco 9*3 bytes Memoria de caracter Si hay N caracteres diferentes se necesitan: N*8*8 bytes 3 caracteres por fila 9 caracteres por columna 4 9 Generación de caracteres y sincronismo clk = 6.25 MHz tciclo = 160 ns 3 caracteres 11 (máximo brillo) líneas de intensidad digitales (rojo, verde y azul) 00 (negro) 25 caracteres 3 caracteres 21 caracteres 10 caracteres sincronismo horizontal 2 3 0 3 carac 12 13 24 11 (máximo brillo) líneas de intensidad digitales (rojo, verde y azul) 00 (negro) 528 líneas (66 filas) 9 filas 57 filas 28 filas sincronismo vertical 9 caracteres 15 116 0 8 9 1 fila 36 28 filas 38 65 10 Modificaciones al esquema de generación de caracteres Se accede a memoria todos los ciclos donde se pintan caracteres ⇒Un ciclo se accede a la memoria de refresco ⇒El ciclo seguiente a la de caracteres y se actualiza RGB Cada 2 ciclos se actualiza el contador de columna de carácter. Es decir, la frecuencia de acceso a memoria es de 12.5 MHz, pero la de actualización de los contadores de 6.25MHz cc =13, 14, 15 Hsyn RGB =37 Vsyn AND fc cc Apagado horizontal >=3 fc NOR leer Memoria de caracter Apagado vertical >=9 5 11 Señales de handshake reloj reset W Datos (8 bits) Interfaz memoria leer OE CS reset A memoria Distinto reloj. Hace falta interbloqueo cambio Dato_actualiz. Dir_memoria (15 bits) Datos (8 bits) escribir Datos (8 bits) reloj } Dir_memoria (15 bits) Dir_memoria (15 bits) reconoc escribir Posición (x=2 y=4) dato_actualiz valor (5 bits) Interfaz comunicación y actualización memoria cambio reconoc Mismo reloj. No hace faltainterbloqueo } handshake 6