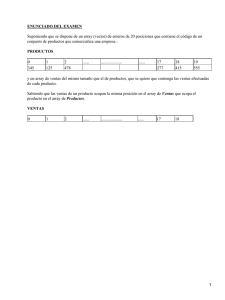

Document

Anuncio

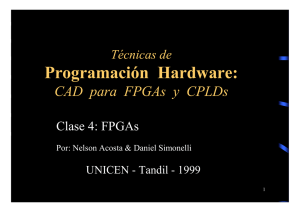

ESTILOS DE IMPLEMENTACIÓN & METODOLOGIAS DE DISEÑO SEMICUSTOM. Diseño basado en Arrays Orientado a reducir costes en el proceso de fabricación disminuyendo el número de pasos de fabricación CONTRAPARTIDA Es atractivo para tiradas pequeñas (donde un proceso dedicado puede ser muy costoso). Las prestaciones son peores. La densidad de integración es más baja. El consumo es más elevado. DOS TIPOS Predifundidos Programables por máscara (MPGAs) (Mask Programmable Gate Arrays) Gate Arrays y Sea of Gates Diseño e Implementación de Sistemas Electrónicos Digitales Precableados (Field-Programmable Gate Arrays, FPGAs) HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGIAS DE DISEÑO Diseño basado en Arrays. predifundidos ó MPGAS (i) P Los diseños se realizan sobre un array de transistores (o celdas básicas) predefinido P La interconexion de estos transistores produce distintas aplicaciones P Solo los últimos pasos del proceso de fabricación son dependientes de la aplicación particular P El tiempo (~ días) y el coste de fabricación de un sistema particular se reducen . las obleas con el array de transistores ya fabricado están disponibles . solo es necesario realizar un número reducido de mascaras . solo es necesario realizar un número reducido de pasos de fabricación. P Perdida de flexibilidad y posibilidad de tener área desocupada P Se diseña a partir de una librería de celdas lógicas precaracterizada P Tipos: con canal (channeled, gate array), sin canal (channeless, sea of gates) Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGIAS DE DISEÑO Diseño basado en Arrays. predifundidos ii Gate array celda base celda pozos difusiones polisilicio alimentaciones canal conexionado se deja espacio para conexionado metales más superficiales definen la interconexión de los transistores celda personalizada: NOR de cuatro entradas Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGIAS DE DISEÑO Diseño basado en Arrays. Predifundidos (iii) Sea of gates LSI Logic LEA 300K (0.6um) Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGIAS DE DISEÑO Diseño basado en Arrays. Precableados ó Programables en Campo P todos los pasos de fabricación son independientes de la aplicación particular P adecuado para aplicaciones con bajo volumen de producción o prototipos P la aplicación particular la programa el diseñador, fuera de la foundry, en campo P disponibles como componentes de catálogo P peores prestaciones y menor densidad de diseño P tiempo de realización física muy reducido (minutos) P distintas tecnologías de programación P consisten en piezas de lógica programables e interconexiones programables Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Tecnólogias de programación q Fusibles/antifusibles no reconfigurable no volatil el elemento de programación ocupa muy poca área fusible: elemento de conexión por defecto corto polisilicio (conductor) dieléctrico (10nm) ejemplo de antifusible difusión n+ (conductor) q Celdas de memoria no volatil (por ej. EEPROM) reconfigurable no volatil el elemento de programación requiere pasos especiales en el proceso de fabricación requere tensiones altas para programación q Celdas de memoria RAM estática reconfigurable volatil: necesidad de reprogramación cada vez que se conecta la alimentación elemento de programación compatible con un proceso CMOS estándard Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Lógica Programable (i) q basada en matrices (arrays) I5 I4 I3 I2 I1 I0 Programmable OR array P implementación de funciones booleanas como suma de productos P variaciones de este esquema * reducir programabilidad PROM: sólo el plano OR programable PAL: sólo el plano AND programable * introducir flip-flops y realimentaciones * particionar el array en macroceldas Programmable AND array O 3O 2O 1O 0 conexión programable Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Lógica Programable (ii) P estas estructuras se suelen denominar Dispositivos Lógicos Programables (PLDs), tambien SPLDs PROM PAL PLA I5 I4 I3 I2 I1 I0 Programmable OR array I3 I2 I1 I0 Programmable OR array O 3O 2O 1O 0 conexión programable Diseño e Implementación de Sistemas Electrónicos Digitales I4 I3 I2 I1 I0 Fixed OR array Programmable AND array Fixed AND array Programmable AND array I5 O 3O2O 1O0 O 3O 2O 1O 0 conexión fija HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Lógica Programable (iii) P PAL más complejo programmable AND array (2i 3X jk ) k macrocells product terms 1 j -wide OR array D j Q OUT j macrocell CLK A B C Diseño e Implementación de Sistemas Electrónicos Digitales i i inputs HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Lógica Programable (iv) q basada en celdas (enfásis multinivel) celda lógica de la familia ACT de ACTEL q usando multiplexores * 10 funciones con un multiplexor de dos entradas A 0 F B 1 S Diseño e Implementación de Sistemas Electrónicos Digitales Configuration A B S F= 0 0 0 0 X Y Y 1 1 1 0 X Y Y 0 0 1 0 0 1 0 1 1 X Y X X X Y 1 0 X Y XY XY XY X1 Y X Y 1 A B 1 SA Y 1 C D 1 SB S0 S1 HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Lógica Programable (v) q basada en celdas (enfásis multinivel) q usando tablas de búsqueda (Look Up Tables o LUTs) A0 Memoria A1 programación para implementar una EXOR dirección 0 0 1 1 2 1 3 0 q usando módulos PAL Diseño e Implementación de Sistemas Electrónicos Digitales HDSE ESTILOS DE IMPLEMENTACIÓN & METODOLOGÍAS DE DISEÑO FPGAs. Interconexiones Programables P distintas opciones para implementar interconexiones programables con celdas de memoria s0 M 0 s1 1 s2 2 s3 3 s MUX M Diseño e Implementación de Sistemas Electrónicos Digitales M HDSE