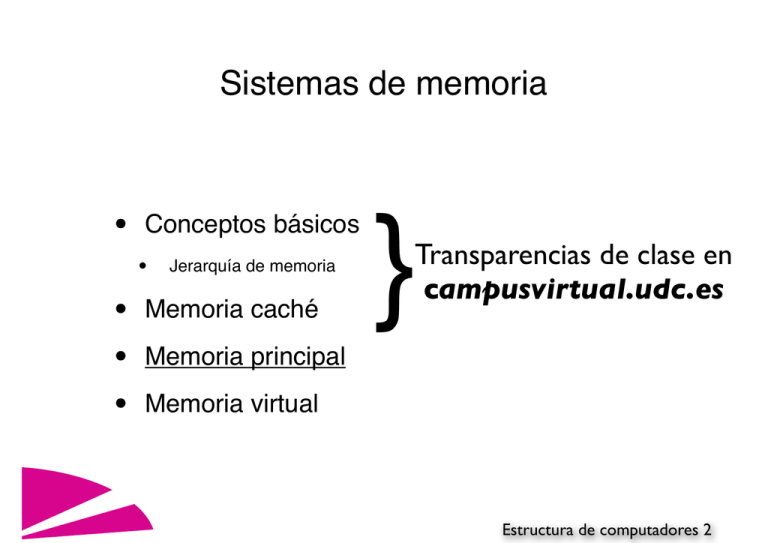

Sistemas de memoria

Anuncio

Sistemas de memoria • Conceptos básicos • • • • Jerarquía de memoria Memoria caché } Transparencias de clase en campusvirtual.udc.es Memoria principal Memoria virtual Estructura de computadores 2 Memoria principal Antiguamente: Matriz de pequeños anillos ferromagnéticos Hoy en día: Tecnología de semiconductores Estructura de computadores 2 Memorias semiconductoras de acceso aleatorio • RAM (Random Access Memory): Lectura y escritura de datos rápida • RAM estática: almacenamiento de los valores binarios mediante biestables • RAM dinámica: almacenamiento a través de celdas que conservan la caga como condensadores: • • • Requieren circuitería de refresco • Más lentas que las estáticas Celda más simple => más densidad y más barata Utilizada para tamaños grandes => coste fijo de circuitería se compensa con el menor coste de las celdas Estructura de computadores 2 Memorias semiconductoras de acceso aleatorio • • ROM (Read Only Memory): • Aplicaciones: Microprogramación, subrutinas de biblioteca para funciones de uso frecuente, programas del sistemas, tablas de funciones • Inconveniente principal: Costes fijos de fabricación, relativamente grande PROM (ROM Programable): Alternativa más barata para aquellos casos en que el número de chips necesario es bajo. • Proceso de escritura: eléctricamente y en un proceso posterior al de fabricación (suministrador o cliente) • Mayor flexibilidad y comodidad Estructura de computadores 2 Memorias semiconductoras de acceso aleatorio • Memorias de sobre todo lectura: Útiles para aplicaciones en las que las lecturas son más frecuentes que las escrituras pero se requiere almacenamiento no volátil • EPROM (Erasable programmable read-only memor): Más caras que una PROM pero podemos actualizar su contenido múltiples veces. Hay que borrar todo su contenido anterior. • (EEPROM (Electrically EPROM): • • Puedes escribirse (un byte) en cualquier momento sin borrar su contenido anterior • • • No volátil y actualizable in situ Más caras y menos densas que las EPROM, Escritura más lenta que la lectura Memoria flash (Alta velocidad de programación) • • Mayor densidad que las EEPROM, del orden de las EPROM Borrado mucho más rápido que las EPROM Estructura de computadores 2 Resumen: tecnologías Tipo de memoria Clase Borrado Mecanismos de escritura Volatilidad Memoria de acceso aleatorio (RAM) Memoria de lectura/ escritura Eléctricamente por bytes Eléctricamente Volátil Memoria de solo lectura (ROM) ROM programable (PROM) Memorias de solo lectura Mediante máscaras No posible PROM borrable (EPROM) Luz ultravioleta, chip completo Memoria FLASH Eléctricamente por bloques PROM borrable eléctricamente (EEPROM) Memorias de sobre todo lectura No-volátil Eléctricamente Eléctricamente por bytes Estructura de computadores 2 Organización • La celda de memoria es el elemento básico de la memoria semiconductora • Normalmente tiene 3 terminales: • Terminal de selección: selecciona la celda para la operacion de lectura o escritura • • Terminal de control: Tipo de operación Tercer terminal: Introducción de la señal que fija el estado a 0 o 1 (en una escritura) o por el que se lee el estado (en una lectura) Control Control Selección Celda Entrada de datos Escritura Selección Celda Detección Lectura Estructura de computadores 2 Lógica del chip de memoria • Un chip contiene una matriz de celdas de memoria • Tamaños típicos encapsulados en un chip: 4M-bits, 16M-bits • Aspecto fundamental del diseño: número de bits de datos que pueden ser leidos/escritos a la vez • Dos vertientes: • Disposición física de las celdas coincide con la disposición lógica (la que percibe el procesador) de las palabras.La matriz se organiza en W palabras de B bits cada una. • Estructura de un-bit-por-chip: Los datos se leen o escriben por bits Estructura de computadores 2 Lógica del chip de memoria • • Se escriben o leen 4 bits a la vez Cuatro líneas (Dʼs) para E/S a/desde un buffer de datos Estructura de computadores 2 Lógica del chip de memoria • Para leer/escribir una palabra de datos en el bus, deben conectarse varias DRAMs como esta al controlador de memoria Estructura de computadores 2 Lógica del chip de memoria • Matriz de memoria estructura en 4 submatrices cuadradas de 2048x2048 elementos Estructura de computadores 2 Lógica del chip de memoria • Matriz de memoria estructura en 4 submatrices cuadradas de 2048x2048 elementos Estructura de computadores 2 Lógica del chip de memoria • Líneas de direcciones (Aʼs): suministran la dirección de la palabra a seleccionar. • Número de líneas requeridas -> log2 W (22 líneas 211=2048) Estructura de computadores 2 Lógica del chip de memoria • Multiplexado de líneas de dirección (A0-A10) => Ahorro de número de pines. Estructura de computadores 2 Lógica del chip de memoria • Primero se proporciona la dirección de la fila y después la dirección de la columna de la matriz Estructura de computadores 2 Lógica del chip de memoria • La selección se realizan mediante 2 señales: • RAS -> Row Address Selection • CAS -> Column Address Selection Estructura de computadores 2 Lógica del chip de memoria • Circuitería de refresco: se inhabilita el chip mientras se refrescan todas las celdas • • El contador de refresco recorre todos los valores de fila La salida del contador se conecta al decodificador de filas y se activa la línea RAS Estructura de computadores 2 Encapsulado de los chips: EPROM DE 8 BITS • Estructura de una palabra-por-chip • • • • • 1M palabras -> 20 pines (210=1M), A0-A19 8 líneas de lectura, D0-D7 Línea de alimentación, Vcc. Terminal de tierra, Vss Pin de habilitación de chip CE (chip enable): ante la posibilidad de varios chips de memoria todos conectados al mismo bus de direcciones, CE indica si la dirección es válida o no para el chip Tensión de programación (operaciones de Escritura), Vpp Estructura de computadores 2 Encapsulado de los chips: DRAM de 16 Mbit • • Terminales de datos de E/S • OE (output enable) -> operación de lectura WE (write enable) -> operación de escritura Estructura de computadores 2 Organización en módulos: memoria de 256 Kbytes • Si un chip de RAM contiene 1 bit por palabra -> se necesitan al menos un número de chips igual al número de bits por palabra • Funciona cuando el tamaño de memoria es igual al número de bits por chip (512*512=256K*8=256KB) • En caso contrario necesitamos un array de chips Estructura de computadores 2 Organización en módulos: memoria de 1Mbyte • Cuatro columnas (grupos) de chips donde cada columna tiene una diposición como la de la figura anterior • 1M palabras -> 20 líneas de direcciones • • 18 bits (menos significativos) -> conectados a los 32 módulos 2 bits (más significativos) -> selección de habilitación de chip a una de las 4 columnas de módulos Estructura de computadores 2 Memorias entrelazadas • Idea: dividir la memoria en módulos independientes • Objetivo: acceso simultáneo a varias palabras en diferentes módulos • • Denominación: ténica de entrelazamiento • Situación ideal: El ancho de banda de acceso a memoria se multiplica por el número de módulos Condición de eficiencia: las referencias a memoria se distribuyen equitativamente entre los módulos. La clave es la distribución Estructura de computadores 2 Esquemas de entrelazamiento • • Entrelazamiento de orden superior Entrelazamiento de orden inferior Memoria total = N = 2n palabras Número de módulos = M = 2m Estructura de computadores 2 Entr. de orden superior (consecutivo) • • Dirección física: n bits • Los m bits más significativos identifican el módulo y el resto un “desplazamiento” dentro del módulo 0 Al i-ésimo módulo le corresponden las direcciones consecutivas i2n-m hasta (i+1)2n-m-1 1 2 3 4 5 6 7 Estructura de computadores 2 Entr. de orden inferior (cíclico) • Al i-ésimo módulo le corresponden las direcciones de la forma k*M+i con k=0,1,2,...2n-m-1 (Espaciamiento M entre ellas • Los m bits menos significativos identifican el módulo y el resto un “desplazamiento” dentro del módulo 0 12 3 4 5 6 7 0 1 2 3 45 6 7 Estructura de computadores 2 Entrelazamiento: Conflicto de memoria • Con cualquier de ambos esquemas se pueden obtener M palabras en paralelo por cada acceso a memoria • Conflicto de memoria: Varias direcciones requieren simultáneamente el acceso a mismo módulo • Los conflictos de memoria son mayores en orden superior debido a la secuencialidad Estructura de computadores 2 Entrelazamiento: Conflicto de memoria • En sistemas multiprocesador es a veces mejor el entrelazamiento de orden superior cuando las tareas con disjuntas o interaccionan poco en tre sí (lo cual no siempre es cierto) • Se suele utilizar el entrelazamiento de orden inferior • Ventajas del superior: • • Expandibilidad Fiabilidad: un fallo se restringe a un área localizada del espacio de direcciones Estructura de computadores 2 Diseño de un esquema de orden inferior • Soluciones: • • Con latches a la salida Con latches a la entrada Estructura de computadores 2 Orden inferior. Latches a la salida • En cada acceso son leidas M palabras consecutivas: k-M+i i=0,1,…,M-1 • • Se almacenan en latches y son transferidas a un MUX • • • • En el mejor caso el tiempo de acceso se reduce en M Las palabras son leidas en el siguiente ciclo. Mecanismo de anticipación Es ideal para accesos a memoria secuenciales Baja su eficiencia en programas no secuenciales (saltos) Para solucionar este problema se pueden diseñar sistemas con latches a la entrada Estructura de computadores 2 Orden inferior. Latches a la salida Estructura de computadores 2 Orden inferior. Latches a la entrada • • • Cada módulo puede usar una dirección relativa particular Necesita un controlador de memoria para procesar las peticiones una a una, secuencialmente Si una petición encuentra el latch ocupado por otra previa, es retardado Estructura de computadores 2 Orden inferior. Latches a la entrada Estructura de computadores 2