Caché

Anuncio

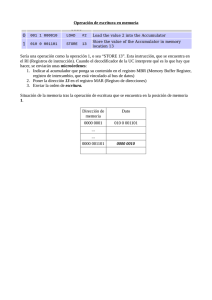

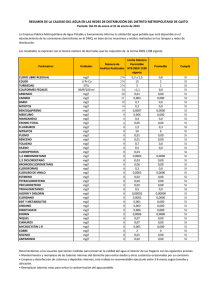

Caché Matías Barbeito Organización del computador 1 2° cuatrimestre 2011 Ciclo de ejecución 1. 2. 3. 4. 5. 6. Busco próxima instrucción Incremento el PC Decodifico Busco operandos Ejecuto Guardo resultados 2 Ciclo de ejecución 1. 2. 3. 4. 5. 6. Busco próxima instrucción Incremento el PC Decodifico Busco operandos Ejecuto Guardo resultados ¡Ac me ceso mo s a ri a ! 3 Conceptos generales 4 Algunos detalles ¿Por qué no usar sólo memoria caché? ¿Cómo ubico las cosas guardadas? ¿Cómo guardo las cosas que no estaban? ¿Cómo hago espacio cuando la caché está llena? 5 Localidad de referencia localidad espacial: si se utiliza un dato en memoria en un instante dado, es muy probable que en los instantes siguientes se utilice algún dato en una dirección cercana. localidad temporal: si se utiliza un dato en memoria en un instante dado, es muy probable que en los instantes siguientes se vuelva a utilizar. 6 Caché de escritura Cuando la posición no está en cache: • Caché write-allocate (asignación en escritura), cuando el CPU desea hacer una escritura a memoria, el controlador de caché carga la línea correspondiente. • Caché write-no-allocate, (¿a que no adivinan?), no. Cuando la posición está en caché: • En una caché write-through (escritura inmediata), el controlador escribe los cambios tanto en la caché como en la memoria inmediatamente. • En una caché write-back (escritura demorada), el controlador escribe los cambios a caché pero no realiza la correspondiente escritura en memoria hasta tanto no se desaloje la línea en cuestión. 7 Yendo de la cama a la caché ¿Cómo almacenamos los datos? CPU PC 0x0002 ADD [0x0000] 0x0AB0 Línea: Agrupación de palabras Memoria caché Memoria principal 0 1 2 3 4 5 6 7 8 9 A B C D E F 10 11 8 Memoria caché línea ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? Memoria principal 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 1 2 3 4 5 6 7 8 9 A 9 Correspondencia directa Memoria caché número de línea 0 1 2 3 4 5 6 7 línea ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? tag Memoria principal 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 1 2 3 4 5 6 7 8 9 A 10 Un poco de jerga Línea: Agrupación de palabras. Bloque: Agrupación de líneas que caben en caché. Índice: Ubicación del dato requerido dentro de la línea. 11 Correspondencia directa Partimos la dirección de memoria principal Dirección de memoria del sistema tag cantidad de bloques en memoria principal línea índice cantidad de cantidad de direcciones líneas en por línea caché 12 Ejercicio Memoria caché: 32 líneas de 16 palabras Memoria principal: 22 0 palabras 1 ¿A cuántas líneas mapeamos la memoria principal? 2 Mostrar el formato de una dirección de memoria. 3 ¿Qué se guarda en la caché? 4 ¿En qué lugar de la caché se guarda la palabra 0x0DB63? Caché asociativa Memoria caché línea ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? tag Memoria principal 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 1 2 3 4 5 6 7 8 9 A 14 Un poco de jerga Línea: Agrupación de palabras. Índice: Ubicación del dato requerido dentro de la línea. 15 Caché asociativa Partimos la dirección de memoria principal Dirección de memoria del sistema tag índice cantidad de líneas en memoria principal cantidad de direcciones por línea 16 Ejercicio Memoria caché: 64 líneas de 32 palabras. Memoria principal: 21 6 palabras. 1 ¿A cuántas líneas mapeamos la memoria principal? 2 Mostrar el formato de una dirección de memoria vista desde la caché. 3 ¿Cuáles de esos campos deben guardarse en la caché? 4 ¿En qué lugar de la caché se guarda la palabra 0xF8C9? 17 Asociativa por conjuntos de 2 vías Memoria caché conjunto 0 1 2 3 4 5 6 7 línea ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? ¿válida? tag línea tag Memoria principal 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 1 2 3 4 5 6 7 8 9 A ¿Qué hacemos si el procesador pide la dirección 0x54? ¿y si pide la 0x95? 18 Un poco de jerga Línea: Agrupación de palabras. Conjunto: Agrupación de líneas. Índice: Ubicación del dato requerido dentro de la línea. 19 Asociativa por conjuntos de n vías Partimos la dirección de memoria principal Dirección de memoria del sistema tag conjunto cantidad de cantidad de bloques en conjuntos en memoria la caché principal índice cantidad de direcciones por línea 20 ¿A quién saco? LRU – Least recently used – Least frequently used LFU Random – bueh... FIFO – epa! 21 Ejercicio Memoria principal: 22 7 palabras. Caché: 21 5 líneas de 64 palabras c/u. 1 Mostrar el formato de una dirección de memoria para una caché asociativa por conjuntos de 2 vías. 2 ¿Cómo queda cargada la caché al leer primero la dirección 0x01178FC, y luego 0x03178FC? 22 Ejercicio 4 Palabras : 64 bits. Direcciones y registros: 32 bits. Instrucciones (tamaño fijo): 64 bits. Producto escalar de dos vectores. MOV R0, 0 R4 tamaño de los vectores (mayor a 0). MOV R1, v1 Etiquetas MOV R2, v2 ciclo: 0x 0000 00F0 v1: 0x F000 00F0 v2: 0x FFFF 00F0 Caché: MOV R3, 0 ciclo: ADD R3, [R1] MUL R3, [R2] 16 KB para almacenar información (líneas) Línea 8 palabras. ADD R0, R3 Calcular tasa de aciertos para: MOV R3, 0 – Correspondencia directa. – Asociativa por conjuntos de 2 vías (LRU). INC R1 INC R2 DEC R4 Palabras : 64 bits. Direcciones y registros: 32 bits. Instrucciones (tamaño fijo): 64 bits. Correspondencia directa MOV R0, 0 • 214/23 da la cantidad de líneas=211 MOV R1, v1 Tag = 18 bits, línea 11, índice 3 • El programa empieza en … 0x0000 00EC (restando de a uno!) • MOV R2, v2 MOV R3, 0 ciclo: ADD R3, [R1] MUL R3, [R2] ADD R0, R3 MOV R3, 0 INC R1 INC R2 DEC R4 Dir. de la instrucción pedido a memoria MOV R0, 0 MOV R1, v1 MOV R2, v2 MOV R3, 0 ciclo: ADD R3, [R1] MUL R3, [R2] ADD R0, R3 MOV R3, 0 INC R1 INC R2 DEC R4 JNZ ciclo ciclo: 0000 00F0 v1: F000 00F0 v2: FFFF 00F0 vista caché Dir. de la instrucción ciclo: ciclo: MOV R0, 0 0000 00EC MOV R1, v1 0000 00ED MOV R2, v2 0000 00EE MOV R3, 0 0000 00EF ADD R3, [R1] 0000 00F0 MUL R3, [R2] 0000 00F1 ADD R0, R3 0000 00F2 MOV R3, 0 0000 00F3 INC R1 0000 00F4 INC R2 0000 00F5 DEC R4 0000 00F6 JNZ ciclo 0000 00F7 0000 00F0 v1: F000 00F0 pedido a memoria v2: FFFF 00F0 vista caché Dir. de la instrucción ciclo: ciclo: pedido a memoria MOV R0, 0 0000 00EC 0000 00EC MOV R1, v1 0000 00ED 0000 00ED MOV R2, v2 0000 00EE 0000 00EE MOV R3, 0 0000 00EF 0000 00EF ADD R3, [R1] 0000 00F0 0000 00F0 MUL R3, [R2] 0000 00F1 0000 00F1 ADD R0, R3 0000 00F2 0000 00F2 MOV R3, 0 0000 00F3 0000 00F3 INC R1 0000 00F4 0000 00F4 INC R2 0000 00F5 0000 00F5 DEC R4 0000 00F6 0000 00F6 JNZ ciclo 0000 00F7 0000 00F7 0000 00F0 v1: F000 00F0 v2: FFFF 00F0 vista caché Dir. de la instrucción ciclo: ciclo: pedido a memoria MOV R0, 0 0000 00EC 0000 00EC MOV R1, v1 0000 00ED 0000 00ED MOV R2, v2 0000 00EE 0000 00EE MOV R3, 0 0000 00EF 0000 00EF ADD R3, [R1] 0000 00F0 0000 00F0 F000 00F0 MUL R3, [R2] 0000 00F1 0000 00F1 FFFF 00F0 ADD R0, R3 0000 00F2 0000 00F2 MOV R3, 0 0000 00F3 0000 00F3 INC R1 0000 00F4 0000 00F4 INC R2 0000 00F5 0000 00F5 DEC R4 0000 00F6 0000 00F6 JNZ ciclo 0000 00F7 0000 00F7 0000 00F0 v1: F000 00F0 v2: FFFF 00F0 vista caché Dir. de la instrucción ciclo: ciclo: pedido a memoria vista caché MOV R0, 0 0000 00EC 0000 00EC 000000 1D 4 MOV R1, v1 0000 00ED 0000 00ED 000000 1D 5 MOV R2, v2 0000 00EE 0000 00EE 000000 1D 6 MOV R3, 0 0000 00EF 0000 00EF 000000 1D 7 ADD R3, [R1] 0000 00F0 0000 00F0 F000 00F0 MUL R3, [R2] 0000 00F1 0000 00F1 FFFF 00F0 000000 1E 0 1E0000 1E 0 000000 1E 1 1FFFE0 1E 0 ADD R0, R3 0000 00F2 0000 00F2 000000 1E 2 MOV R3, 0 0000 00F3 0000 00F3 000000 1E 3 INC R1 0000 00F4 0000 00F4 000000 1E 4 INC R2 0000 00F5 0000 00F5 000000 1E 5 DEC R4 0000 00F6 0000 00F6 000000 1E 6 JNZ ciclo 0000 00F7 0000 00F7 000000 1E 7 0000 00F0 v1: F000 00F0 v2: FFFF 00F0 En resumen ¿Una caché? Una memoria de acceso rápido. ¿Para qué? Para mejorar la perfomance. ¿Por qué no usar sólo memoria caché? Es muy cara. ¿Cómo se guardan las cosas en la caché? Correspondencia directa – Asociativa – Asociativa por conjuntos De cada manera me interesa Cómo ubico las cosas guardadas Cómo guardo las cosas que no estaban Cómo hago espacio cuando la caché está llena Línea – bloque – índice – conjunto – tag. 30