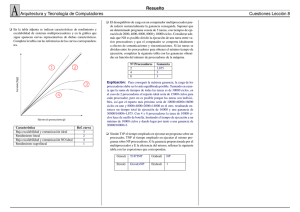

Introducción a la Computación Paralela

Anuncio