pontificia universidad católica madre y maestra facultad

Anuncio

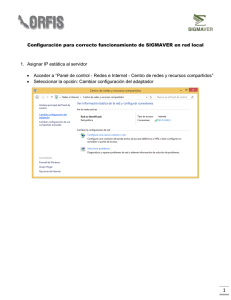

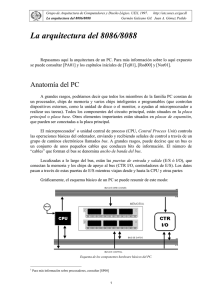

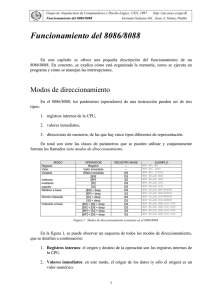

PONTIFICIA UNIVERSIDAD CATÓLICA MADRE Y MAESTRA FACULTAD DE CIENCIA DE LAS INGENIERÍAS DEPARTAMENTO DE INGENIERÍA TELEMATICA PROGRAMA Microprocesadores I Clave ITT – 327 CONTENIDO: Unidad I: • • • Introducción al Microprocesador y el Microcomputador. Arquitectura General de un Sistema de Microcomputador. Evolución de la arquitectura de los Microprocesadores Intel. Sistemas Numéricos. Unidad II: Arquitectura de Software del 8088/8086. • • • • • • • • • • • Arquitectura de los Microprocesadores 8088/8086. Modelo de Software del 8088/8086. Espacio en memoria y Organización de Datos. Tipos de Datos. Registros de Segmento y Segmentación de la Memoria. Memoria de propósitos generales, dedicada y reservada. El Instruction Pointer. Registros de Datos. Registros Punteros y de Índice. Registro de Estatus. El Stack Segment. Espacio en Memoria para Entrada/Salida. Unidad III: Lenguaje de Programación Ensamblador. • • • • • • • • • • • • Set de Instrucciones. Instrucciones de Movimiento de Datos. Modos de Direccionamiento. Instrucciones Aritméticas. Instrucciones Lógicas. Instrucciones de desplazamiento y de Rotación. Instrucciones de Control de Flag. Instrucciones de Comparación. Instrucciones de Salto y de control de Flujo. Subrutinas e Instrucciones de manejo de Subrutinas. Loops e Instrucciones de manejo de Loops. Strings e Instrucciones de manejo de Strings. 1 Unidad IV: Estructura del Hardware del 8088/8086. • • • • • • • • • • Sistema en Modo Mínimo. Señales de Interface. Sistema en Modo Máximo. Señales de Interface. Características Eléctricas. Sistema de Reloj. El 8284. Ciclo de Reloj y Ciclo de Máquina. Organización Física del espacio en Memoria. Bus de Direcciones y Bus de Datos. Señales de Control de Memoria. Ciclos de Lectura y Escritura. Ciclos de Entrada/Salida. Unidad V: Interfaz del 8088/8086 a memoria. • • • • Direccionamiento y Selección de Dispositivos (Chip Select). Memoria RAM y consideraciones de interface. Memoria ROM y consideraciones de interface. Memoria FLASH y consideraciones de interface. Unidad VI: Periféricos de Entrada/Salida. • • • • • Interface de Entrada/Salida de propósitos especiales. Interface de Periféricos Programable, 8255A. Temporizador/Contador Programable, 8254A. Controlador de Acceso directo a Memoria, 8237A. Controlador de Teclado/pantalla Programable, 8279. Unidad VII: Introducción al diseño de sistemas de microprocesadores. • • • • • • • Mecanismo de Interrupción. Tipos y Prioridades. Tabla de Vectores de Interrupción. Instrucciones de Interrupción. Habilitando e Inhabilitando Interrupciones. Interrupciones por Hardware. Controlador de Interrupciones Programable, 8259A. Interrupciones por Software. Interrupción no enmascarable. 2 EVALUACIÓN TEORIA: PRACTICAS 1era PRACTICA 2da PRACTICA 3era PRACTICA 4ta PRACTICA 5ta PRACTICA 6ta PRACTICA 7ma PRACTICA EXAMEN FINAL TEMA Cadena de Caracteres. Suma y Resta de Números. Modo Gráfico. Controlador de Luces por Pto Paralelo. Controlador de Motor Paso a Paso. Piano / Órgano. Terminate and Stay Resident. Diseño completamente funcional de un Sistema. TOTAL CALIFICACION 10% 10% 10% 10% 10% 10% 10% 30% 100% EVALUACIÓN LABORATORIO: PROYECTO DE APLICACION Conceptualización y Alcance Diseño Preliminar Cronograma de Trabajo Poster Entrega Formal + Documentación TOTAL CALIFICACION 10% 10% 10% 10% 60% FECHA DE ENTREGA 25 – 26 Enero 1 – 2 Febrero 8 – 9 Febrero 22 – 23 Febrero 14 Abril 100% CONSULTA BIBLIOGRÁFICA: • Microprocesadores Intel. Barry B. Brey. • Lenguaje Ensamblador para Computadores basados en Intel. Kip R. Irvine. • Microcomputer Systems: The 8086/8088 Family. Yu-Cheng Liu & Glenn A. Gibson. • The 8088 & 8086 Microprocesors. Walter A. Triebel & Avtar Singh. • The 8088 Project Book. Robert Grossblatt. 3