Primera Parte: Cuestiones

Anuncio

S.E.T.I. 1

Examen 16 Feb. 2007

Primera Parte: Cuestiones

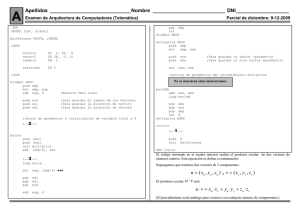

1. Tema corto. Segmento de estado de tarea. Nota: No es necesario dibujarlo.

(1.5/10)

Solución. El TSS almacena el estado (contexto) de las tareas. Tiene campos dinámicos, que son actualizados cuando se cambia de tarea y campos estáticos que se definen al

comenzar una nueva tarea pero que no se modifican dinámicamente.

a) Campos dinámicos

Registros de propósito general.

Registros selectores de segmentos.

Registro EFLAGS.

Puntero de instrucción EIP.

Enlace a la tarea previa que no es otra cosa que el selector de segmento del

TSS anterior. Se actualiza solo cuando se espera retornar de una tarea (llamada

mediante la instrucción CALL, una interrupción o una excepción).

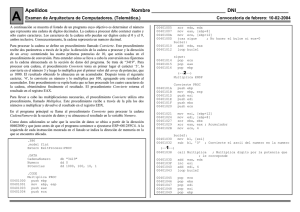

31

0

15

Direccion Base Mapa de Bits E/S

T 100

Selector Segmento LDT

96

GS

92

FS

88

DS

84

SS

80

CS

76

ES

72

EDI

68

ESI

64

EBP

60

ESP

56

EBX

52

EDX

48

ECX

44

EAX

40

EFLAGS

36

EIP

32

CR3 (PDBR)

28

SS2

SS1

SS0

8

4

ESP0

Enlace a Tarea Anterior

Ing. Electrónica (Curso 2006-2007)

16

12

ESP1

Bits Reservados. Poner a 0

24

20

ESP2

0

(la figura

1

S.E.T.I. 1

Examen 16 Feb. 2007

no se pide)

b) Campos estáticos.

Selector que apunta al descriptor de la LDT empleada. Se permite a cada tarea

tener su propia tabla de descriptores local.

CR3. Dirección fı́sica del directorio de páginas. Igualmente se permite a cada

tarea tener su propio directorio de páginas.

Punteros de pila (y selectores de segmento) de nivel 0, 1 y 2.

Bit T. Cuando vale uno provoca una excepción de depuración cuando se cambia

de tarea.

Dirección base del mapa de acceso de entrada/salida.

Es un desplazamiento de 16 bits (<DFFFh) que apunta al mapa de permisos de

entrada salida, que está contenido en el propio TSS. Sirve para limitar el acceso

a E/S. El tamaño es variable. Es un acceso limitado a E/S para las tareas con

grano fino ya que podemos definir a qué puertos se accede y a cuales no.

Segmento de Estado de Tarea (TSS)

El ultimo byte del

mapa de bits debe

tener todos los

bits a uno

31

24 23

0

1 1 1 1 1 1 1 1

Mapa de Bits de Permisos de E/S

Direccion Base del Mapa de E/S

64H

0

Si CPL>EFLAGS.IOPL se comprueba el mapa de permisos de E/S para ver si podemos acceder, si no el acceso está permitido. Cada bit del mapa se corresponde

con el permiso de acceso a un puerto (byte).

; Ejemplo:

;

el bit 1 del sexto byte:

;

indica el puerto 41 = (6-1)*8 + 1

;

si vale 1 esta prohibido el acceso

;

si vale 0 esta permitido el acceso

Si todos los bits del puerto accedido valen 0 podemos acceder (si es de tamaño

dword se representará con 4 bits), sino se producirá una excepción de protección general. Las direcciones E/S no representadas se consideran a 1, es decir

prohibidas.

Ing. Electrónica (Curso 2006-2007)

2

S.E.T.I. 1

Examen 16 Feb. 2007

2. Tema corto. Interrupciones y excepciones: clasificación.

(1.5/10)

Solución.

Interrupciones

Básicamente hablamos de interrupciones cuando es algo externo al microprocesador el

causante de la misma. Estas pueden ser:

Externas. Las produce algún dispositivo periférico conectado al microprocesador a

través de las patillas de interrupciones del mismo.

• Patilla /NMI (Non Maskable Interrupt). Interrupción no enmascarable. Se

activa por flanco y se memoriza un nivel de peticiones. Su atención se realiza

mediante el vector no 2.

• Patilla /INTR. Interrupción enmascarable con EFLAGS.IF = 0. Es activa por

nivel.

Internas. Generadas por software por medio de la instrucción INT n.

Excepciones

Las excepciones son situaciones provocadas por el propio funcionamiento del microprocesador.

Hardware.

• Faults. Se producen antes de ejecutar la instrucción. CS:EIP se guarda en la

pila y apunta a la dirección que produjo el fallo. Se reintentan al retornar de la

excepción

• Traps. Se producen después de la ejecución de la instrucción. CS:EIP apunta

a la instrucción siguiente. Algunos traps permiten continuar la ejecución del

programa, otros no.

• Aborts. Cuando hay errores graves (errores hardware, valores ilegales o no

consistentes en las tablas). No se puede continuar la ejecución del programa.

No siempre se puede precisar la localización exacta.

Software. Excepciones como: INTO, INT3, BOUND, INT n.

Ing. Electrónica (Curso 2006-2007)

3

S.E.T.I. 1

Examen 16 Feb. 2007

3. Cuestión. ¿Qué diferencias hay entre la codificación little endian y la big endian?

Pon un ejemplo.

(0.5/10)

Solución. Orden de los bytes en memoria. Es importante conocer el orden de almacenamiento de los datos en memoria sobretodo cuando pasamos información de un tipo

de arquitectura a otro.

Little endian. Se almacena primero el LSByte (Least Significant Byte: byte menos

significativo) y luego el MSByte (Most Significant Byte: byte más significativo).

Es tı́pico en las arquitecturas de Intel.

Big endian. Se almacena primero el MSByte y luego el LSByte. Es tı́pico de Motorola.

; El dato escrito en base hexadecimal 12345678h

; se almacenara como:

;

Direccion:

0

1

2

3

; Little endian

78h 56h 34h 12h

;

Big endian

12h, 34h, 56h, 78h

4. Cuestión. ¿Qué es el segmento de pila máquina y cómo funciona? Nota: no estoy

preguntando por la pila de registros de la FPU.

(0.5/10)

Solución. Sección de Pila. Es una zona especial que permite almacenar datos de forma dinámica en forma de pila LIFO (Last In, First Out ), que significa que el último dato

en entrar es el primero en salir.. Existe un conjunto de registros que apuntan a la cima de

la pila (notar que en la mayorı́a de los microprocesadores las pilas crecen hacia posiciones

de memoria decrecientes). La operación PUSH introduce un dato en la pila y la operación

POP extrae un dato de la misma.

Memoria

Memoria

PUSH

POP

Dato 1

Dato 2

Dato 3

Puntero de pila

Dato 1

Dato 2

Dato 3

Dato 4

Dato 5

Dato 6

0

Ing. Electrónica (Curso 2006-2007)

4

S.E.T.I. 1

Examen 16 Feb. 2007

5. Cuestión. Enumera los diferentes números reales especiales que puede codificar

la unidad de punto flotante.

(0.5/10)

Solución.

Números reales especiales. Entre estos estarı́an:

Los infinitos, que se obtienen al dividir por cero.

Los ceros que tienen signo.

Los no normalizados, que aumentan la resolución cerca del cero pero con menos

dı́gitos de precisión

Los no números, que pueden ser de señalización (SNaN Signaling Not a Number)

o silenciosos (QNaN:√Quiet Not a Number). Estos se obtienen como resultado de

operaciones del tipo: −1 o log(−1).

NaN

NaN

− Finito No Normalizado

−∞

S

1

E

0

1

0

−Finito Normalizado

+Finito No Normalizado

−0 +0

+Finito Normalizado + ∞

Números Reales y Codificaciones NaN para Punto Flotante de 32-Bit

Sig

E

Sig

S

0.000...

0.000...

−0

+0 0

0

1 1...254

1.XXX...

−Finito

No Normalizado

−Finito

Normalizado

1

255

1.000...

−∞

X

255

1.0XX...

X

255

1.1XX...

0.XXX...

+Finito

No Normalizado 0

0

0.XXX...

+Finito

1...254 1.XXX...

Normalizado 0

+∞ 0

255

1.000...

SNaN

SNaN X

255

1.0XX...

QNaN

QNaN X

255

1.1XX...

(la figura no se pide)

6. Cuestión. Explica el contenido del registro DR6.

31

16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reservado (puesto a 1)

B B B 0 1 1 1 1 1 1 1 1 B B B B

DR6

T S D

3 2 1 0

(0.5/10)

Solución.

En este registro se guarda el estado de la depuración.

B0..B3. Condición de breakpoint detectada. Se activan aún cuando el punto de

ruptura no esté habilitado.

BD. Acceso a registro de depuración detectado. Indica que la siguiente instrucción

accederá a un registro de depuración (DR0..DR7). Esta prestación sólo está activa si

DR7.GD = 1 (General Detection flag).

BS. Indica que la excepción de depuración se produjo por el modo paso a paso de

ejecución (EFLAGS.TF=1) que es la excepción de depuración de mayor prioridad.

Ing. Electrónica (Curso 2006-2007)

5

S.E.T.I. 1

Examen 16 Feb. 2007

BT. Indica que la excepción se produjo por una conmutación de tarea (TSS.T = 1).

Este registro es un registro pegajoso (sticky register), lo que significa que el microprocesador pone a 1 los bits, pero no los borra automáticamente. El Sistema Operativo debe

borrar estos bits.

NOTA: Esta parte constituye el 50 % de la nota del examen. La nota final es la media de la nota de prácticas

y la nota del examen, aunque para ello es imprescindible aprobar el examen y las prácticas cada uno por separado.

Ing. Electrónica (Curso 2006-2007)

6

S.E.T.I. 1

Examen 16 Feb. 2007

Segunda Parte: Problemas

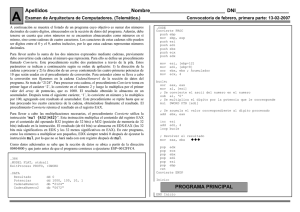

1. Problema. En el laboratorio disponemos de la tarjeta de adquisición de datos

ACL-8112, que permite la salida y entrada de datos digitales y analógicos.

Dispone de 16 canales de entrada digitales y de 16 canales de salida digitales. Se

accede a ellos con direcciones de E/S (instrucciones in y out). La dirección BASE

es la 220h. Las direcciones BASE+6 y BASE+7 son empleadas para los canales

de entrada (byte menos significativo y más significativo respectivamente; solo

lectura) y las direcciones BASE+13 y BASE+14 para los canales de salida (solo

escritura).

El esquema hardware a emplear es el siguiente:

Sistema de Test de Circuitos Integrados Lógicos de 14 patillas de la serie TTL

J3

J1

BASE+13

BASE+14

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

bit 0

bit 0

10k

10k

10k

10k

10k

10k

10k

1

2

3

4

5

6

7

14

13

12

11

10

9

8

10k

10k

Zócalo

10k

10k

10k

Salidas

J2

BASE+6

bit 0

BASE+7

bit 0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Entradas

ACL-8112

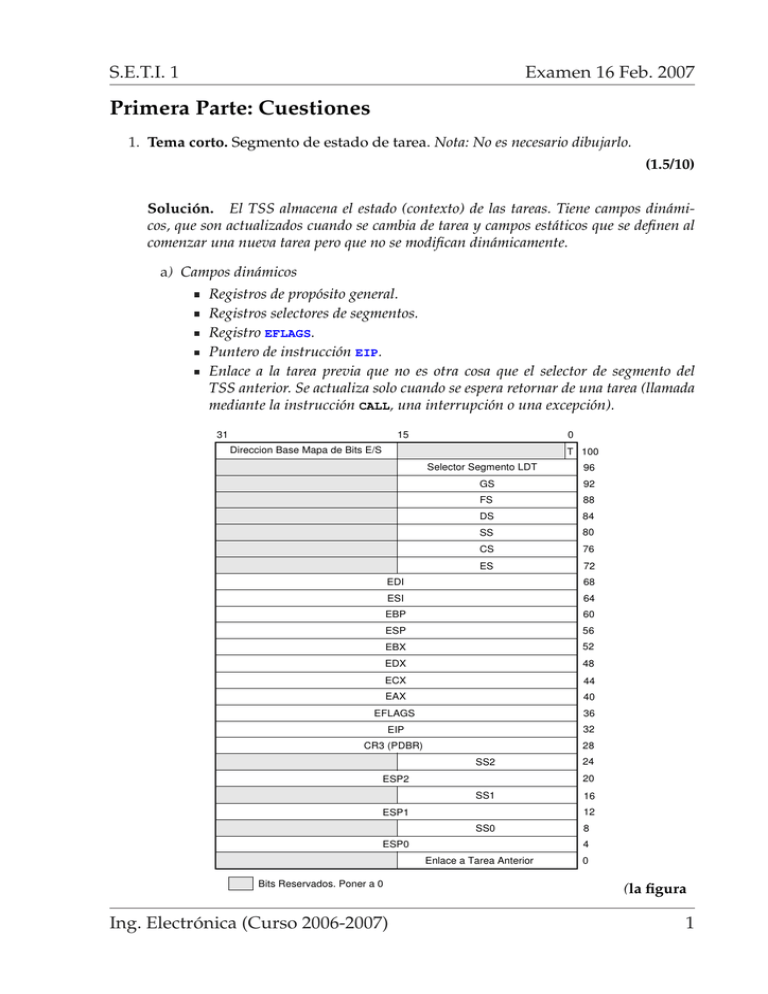

Se pide realizar un programa que sea capaz de comprobar el funcionamiento de

algunos circuitos integrados lógicos de la serie estándar TTL como el 7432 (OR),

el 7400 (NAND), el 7408 (AND), y el 7486 (XOR). El patillaje del integrado 7400

se muestra en la siguiente figura (el resto es similar, en cuanto a qué patillas son

entradas y cuales salidas).

Ing. Electrónica (Curso 2006-2007)

7

S.E.T.I. 1

Examen 16 Feb. 2007

VCC

14

13

12

11

10

9

1

2

3

4

5

6

8

7

GND

El trabajo se puede desglosar en los siguientes apartados:

a) Generación de los vectores de test. Esta rutina toma como dato de entrada (en

AX) un vector inicial, que se forma a partir de la tabla de verdad de la función

lógica a analizar. La rutina de generación de vectores de test deberá devolver los

4 vectores que aparecen ordenando los bits según se ve en el ejemplo de la figura

y devolverlos en AX, BX, CX y DX. (30 %)

Tabla de verdad, ejemplo pana AND (7408)

Vector inicial

000010100111xxxx

"x" : no importa

Salida

0

0

0

1

Salida

Salida

Salida

00

01

10

11

Salida

Entradas

xxxx000000000000

xxxx010010001001

Vectores de test

xxxx100100010010

xxxx111111111111

b) Retardo de N milisegundos. Se nos pide que entre la presentación al integrado de un vector de test y su comprobación transcurra un tiempo mı́nimo de N

milisegundos, que implementaremos mediante esta subrutina. Como parámetro

de entrada en EAX el número de milisegundos de espera. El microprocesador

funciona a 3GHz. (20 %)

c) Comprobación de un vector de test. Esta rutina presentará el vector de test

contenido en AX al circuito integrado a través de la tarjeta ACL-8112 y después

de un retardo de 20 milisegundos comprobará las entradas para ver si lo cumple.

(30 %)

Los bits que en la salida del ACL8112 pongamos en un valor deberán permanecer

con el mismo valor si los hemos conectado a una entrada del circuito integrado a

verificar. Las salidas deberán dar un valor que coincida con el del vector de test

presentado.

c) Rutina principal de identificación. Basándose en una tabla de vectores iniciales (que tenéis que especificar) para la comprobación de los circuitos integrados

lógicos especificados, el programa deberá obtener los vectores de test, para cada

vector inicial, probar cada vector de test con su retardo correspondiente, y averiguar si cumple todos los vectores de test, para devolver en EAX el número del

circuito integrado (que podéis poner al lado de cada vector inicial en la tabla).

Ing. Electrónica (Curso 2006-2007)

8

S.E.T.I. 1

Examen 16 Feb. 2007

Si no cumple un vector de test se pasa al siguiente vector inicial hasta terminar

con todos. Devolverá el número del integrado identificado o cero en caso de no

identificar ninguno. (20 %)

(2.5/10)

Solución.

Una posible solución es:

[BITS 32]

[SECTION .text]

[GLOBAL _TestIC]

5

10

BASE equ

220h

; Direccion de E/S de la ACL-8112

; Apartado d) del examen (20 %)

_TestIC:

;Prototipo de la funcion en C

;

; extern int TestIC();

;

; ebp+0

Direccion de retorno

; ebp+4

Antiguo ebp

15

push

mov

pushad

20

25

35

40

45

50

; Prologo C

mov

ecx,0

@otro_integrado:

push

ecx

xor

edi,edi

mov

di,[Vectores+ecx*4]

mov

[Integrado],edi

mov

ax,[Vectores+ecx*4+2]

call

30

ebp

ebp,esp

GeneraVectoresTest

pushad

call

PruebaVector

popad

jnz

@sigue_otro

mov

ax,bx

pushad

call

PruebaVector

popad

jnz

@sigue_otro

mov

ax,cx

pushad

call

PruebaVector

popad

jnz

@sigue_otro

mov

ax,dx

pushad

call

PruebaVector

popad

jz

@salir

@sigue_otro:

pop

ecx

inc

ecx

cmp

ecx,[NVectores]

Ing. Electrónica (Curso 2006-2007)

; N o circuito integrado

; Vector inicial

; ax,bx,cx,dx contienen

; los vectores de test

; Prueba 1er vector

; Prueba 2 o vector

; Prueba 3er vector

; Prueba 4 o vector

9

S.E.T.I. 1

55

Examen 16 Feb. 2007

jnz

@otro_integrado

popad

pop

xor

ret

ebp

eax,eax

; Epilogo C

; No encontrado en tabla

ecx

; Recupero de la pila

ebp

eax,[Integrado]

; Epilogo C

65

@salir:

pop

popad

pop

mov

ret

70

; Apartado a) del examen (30 %)

GeneraVectoresTest:

; Entrada: EAX = vector inicial

mov

ecx,4

60

75

80

85

@repite:

mov

bt

jnc

bts

@s1:

bt

jnc

bts

@s2:

bt

jnc

bts

@s3:

mov

shl

or

dx,0

ax,15

@s1

dx,1

; Comprueba el bit 15

; Remapea en bit 1

ax,14

@s2

dx,0

; Comprueba el bit 14

ax,13

@s3

dx,2

; Comprueba el bit 13

bx,dx

bx,3

dx,bx

;

;

;

;

Salida

; Remapea en bit 2

bx = .... .... .... .SAB

bx = .... .... ..SA B...

Desplaza y copia

dx = .... .... ..SA BSAB

95

ax,1

bx,1

ax,1

bx,1

ax,1

bx,1

100

shl

or

shl

or

bx,6

dx,bx

bx,3

dx,bx

mov

loop

[V1+ecx*2],dx

@repite

mov

mov

mov

mov

ret

ax,[V1]

bx,[V2]

cx,[V3]

dx,[V4]

105

Entrada B

; Remapea en bit 0

shl

shl

shl

shl

shl

shl

90

Entrada A

; bx = .... .... .... ...A

; bx = .... .... .... ..AB

; bx = .... .... .... .ABS

;

;

;

;

bx

dx

bx

dx

=

=

=

=

....

....

....

....

...A

...A

ABS.

ABSA

BS..

BSSA

....

BSSA

....

BSAB

....

BSAB

110

; Apartado b) del examen (20 %)

Retardo:

; Entrada EAX los milisegundos de espera

; La cuenta será 1ms*F_CPU * EAX = 3e6 * EAX ciclos

Ing. Electrónica (Curso 2006-2007)

10

S.E.T.I. 1

115

120

125

130

135

140

145

150

155

160

165

Examen 16 Feb. 2007

mov

ecx,eax

@repite_retardo:

rdtsc

; Memorizo instante EDX EAX

mov

edi,eax

mov

esi,edx

add

edi,3000000

adc

esi,0

@espera:

rdtsc

cmp

jl

cmp

jl

loop

ret

edx,edi ; Comprueba que la parte alta llegó

@espera

eax,esi ; Comprueba que la parte baja llegó

@espera

@repite_retardo

; Apartado c) del examen (30 %)

PruebaVector:

; Entrada AX el vector de test

mov

dx,BASE+6

; Apunto a dir. E/S para las salidas (ACL-8112)

out

dx,ax

; Saco los datos

push

eax

; Guardo el vector de test

mov

call

eax,20

Retardo

; Espero lo que me indican

pop

mov

in

ebx

dx,BASE+13

ax,dx

; Recupero el vector de test en ebx

; Apunto a dir. E/S para las entradas (ACL-8112)

; Leo los datos

cmp

ret

ax,bx

; ZF=1 si son iguales, ZF=0 si son distintos

[SECTION .data]

; Sección de datos inicializados

NVectores

dw 4

Vectores

dw 7408, 0000101001110000b ; Puerta AND

dw 7400, 0010111011100000b ; Puerta NAND

dw 7432, 0000111011110000b ; Puerta OR

dw 7486, 0000101011100000b ; Puerta XOR

[SECTION .bss]

V1 resw

1

V2 resw

1

V3 resw

1

V4 resw

1

Integrado

resd

; Seccion de datos no inicializados

1

Un ejemplo de programa principal (no se pide):

#include <stdio.h>

#include <stdlib.h>

4

extern int TestIC();

int main()

{

Ing. Electrónica (Curso 2006-2007)

11

S.E.T.I. 1

Examen 16 Feb. 2007

int ic;

9

ic=TestIC();

if(ic) printf("Identificado el circuito integrado %d\n", ic);

else

printf("No se ha identificado ningún"

" circuito de los memorizados\n");

14

}

Y un ejemplo de fichero makefile (no se pide):

testic.exe: testic.c rutinas.o

gcc testic.c rutinas.o -o testic.exe -g

5

rutinas.o: rutinas.asm

nasm -g -f win32 rutinas.asm -o rutinas.o

Ing. Electrónica (Curso 2006-2007)

12

S.E.T.I. 1

Examen 16 Feb. 2007

2. Problema. Se pide implementar una subrutina escrita en ensamblador que realize el producto de dos matrices cuyos elementos están expresados en formato real

largo. La subrutina se llamará desde un programa en C y el prototipo de la función será:

void ProductoMatrices(double * A, int m, int n, // Matriz m x n

double * B, int r,

// Matriz n x r

double * C);

// Matriz m x r

donde la matriz A tiene dimensiones m × n, la matriz B tiene dimensiones n × r

y la matriz resultado del producto C tiene dimensiones m × r.

La fórmula para el producto de matrices es la siguiente:

ci,j =

Pn−1

k=0

ak,j ∗ bi,k

Cuando se pasa un puntero a una función en C lo que aparece es la dirección en la

que se encuentra la variable. Ası́, para facilitar la legibilidad pondremos después

del prólogo C:

%define

%define

%define

%define

%define

%define

DirA

M

N

DirB

R

DirC

ebp+8

ebp+12

ebp+16

ebp+20

ebp+24

ebp+28

;

;

;

;

;

;

Direccion

Dimension

Dimension

Direccion

Dimension

Direccion

de la matriz A

m

n

de la matriz B

r

de la matriz C

El ejemplo de llamada a la función será:

extern void ProductoMatrices(double * A, int m, int n,

double * B, int r, double *C );

// ...

// Asigno matrices

double A[3*4]={2,1,0, -1,1,0, 0,0,1, 0,0,0};

double B[4*3]={1,1,1,0, 1,1,1,0, 1,1,1,0};

// Reservo espacio

double C[4*4]={0,0,0,0,

0,0,0,0,

0,0,0,0,

0,0,0,0};

// ...

ProductoMatrices(A,3,4,B,3,C);

(2.5/10)

Solución.

3

Una posible solución es:

[BITS 32]

[SECTION .text]

[GLOBAL _ProductoMatrices]

; La subrutina en C tiene el siguiente prototipo:

;

; void ProductoMatrices(double * A, int m, int n,

Ing. Electrónica (Curso 2006-2007)

13

S.E.T.I. 1

8

13

18

23

28

Examen 16 Feb. 2007

;

;

; ebp+0

; ebp+4

%define

%define

%define

%define

%define

%define

double * B, int r, double *C );

Direccion de retorno

Antiguo ebp

DirA

ebp+8

; A es tamaño M x N

M

ebp+12

N

ebp+16

DirB

ebp+20

; B es tamaño N x R

R

ebp+24

DirC

ebp+28

; C es tamaño M x R

_ProductoMatrices:

push

ebp

mov ebp,esp

pushad

; Prologo de C

; Programa

finit

mov eax,0

mov [var_j],eax

@bucle_vertical:

; var_i=0

mov eax,0

mov [var_i],eax

@bucle_horizontal:

; var_j=0

33

FLDZ

mov eax,0

mov [var_k],eax

@bucle_interior:

; Suma=0.0

-

; var_k=0

38

; c(i,j) = SUM_k {b(i,k)*a(k,j)}

43

48

; Para obtener a(i,k) la cuenta es

; DirB + (i+k*M)*8

mov

eax,[var_k]

mov

edx,[M]

imul

edx

add

eax,[var_i]

shl

eax,3

add

eax,[DirB]

FLD

53

58

qword [eax]

; b(i,k)

Suma

; Para obtener a(k,j) la cuenta es

; DirA + (k+j*N)*8

mov

eax,[var_j]

mov

edx,[N]

imul

edx

add

eax,[var_k]

shl

eax,3

add

eax,[DirA]

63

FLD

FMULP

FADDP

qword [eax]

ST1

ST1

68

mov

inc

mov

cmp

eax,[var_k]

eax

[var_k],eax

eax,[N]

Ing. Electrónica (Curso 2006-2007)

; a(k,j)

; a()*b()

; Suma

b(i,k)

Suma

Suma

14

S.E.T.I. 1

Examen 16 Feb. 2007

jl

@bucle_interior

; Si var_k<n sigue

; Para obtener c(i,j) la cuenta es

; DirC + (i+j*M)*8

mov

eax,[var_j]

mov

edx,[M]

imul

edx

add

eax,[var_i]

shl

eax,3

add

eax,[DirC]

73

78

83

88

FSTP

qword [eax]

; -

mov

inc

mov

cmp

jl

eax,[var_i]

eax

[var_i],eax

eax,[M]

@bucle_horizontal

; Si var_i<m sigue

mov

inc

mov

cmp

jl

eax,[var_j]

eax

[var_j],eax

eax,[R]

@bucle_vertical

; Si var_j<r sigue

93

popad

pop ebp

ret

; Epilogo en C

98

[SECTION .bss]

var_i

resd 1

var_j

resd 1

var_k

resd 1

; Segmento de datos no inicializados

Un ejemplo de programa principal (no se pide):

3

8

#include <stdio.h>

#include <stdlib.h>

extern void ProductoMatrices(double * A, int m, int n,

double * B, int r, double *C );

void PintaMatriz(double *M, int x, int y)

{

int i,j;

printf("Matriz\n");

for(j=0;j<y;j++)

{

for(i=0;i<x;i++)

printf(" %5.2lf ",M[j*x+i]);

printf("\n");

}

13

}

18

23

int main()

{

int i,j;

double A[3*4]={2,1,0, -1,1,0, 0,0,1, 0,0,0};

double B[4*3]={1,1,1,0, 1,1,1,0, 1,1,1,0};

double C[4*4]={0,0,0,0, 0,0,0,0, 0,0,0,0, 0,0,0,0};

Ing. Electrónica (Curso 2006-2007)

15

S.E.T.I. 1

Examen 16 Feb. 2007

printf("PRODUCTO DE MATRICES\n");

PintaMatriz(A,3,4);

printf("*\n");

PintaMatriz(B,4,3);

printf("=\n");

28

ProductoMatrices(A,3,4,B,3,C);

33

PintaMatriz(C,4,4);

return 0;

}

Y un ejemplo de fichero makefile (no se pide):

test: producto.o test.c

gcc -g -o test test.c producto.o

4

producto.o: producto.asm

nasm -g -f win32 producto.asm -o producto.o

NOTA: Esta parte constituye el 50 % de la nota del examen. La nota final es la media de la nota de prácticas

y la nota del examen, aunque para ello es imprescindible aprobar el examen y las prácticas cada uno por separado.

Ing. Electrónica (Curso 2006-2007)

16