Multiplexores Digitales

Anuncio

3/$1,78'RF6

0XOWLSOH[RUHV'LJLWDOHV

Sr. H. Leijon, UIT

81,21,17(51$7,21$/('(67(/(&20081,&$7,216

,17(51$7,21$/7(/(&20081,&$7,2181,21

81,21,17(51$&,21$/'(7(/(&2081,&$&,21(6

-1-

1.

0XOWLSOH[RUHV'LJLWDOHV

1.1

Introducción

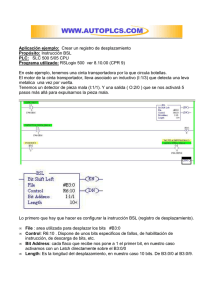

Los sistemas primarios de Modulación por Impulsos Codificados (MIC; Pulse Code Modulation, PCM) sirven

para aplicaciones de corta distancia. En la red de media y larga distancia, donde se requiere alta capacidad de canal, es

más económico y práctico agrupar un gran número de sistemas de MIC en una sola línea de transmisión común, en vez

de usar varios sistemas primarios MIC. Estos sistemas de mayor orden son también llamados multiplexores digitales.

La tarea básica de un multiplexor digital es combinar un número de flujos de impulsos de entrada, tributarios, en

un solo flujo de impulsos de salida, con una velocidad digital bruta que es algo mayor que la suma de las velocidades de

los tributarios y viceversa. En un sistema de segundo orden se combinan cuatro señales primarias MIC, en una señal

digital común. Los dos sistemas primarios MIC estandarizados se originan en dos multiplexores digitales con diferentes

velocidades de bit (Ver Figura 1). Un múltiplex digital basado en el sistema MIC de 30 canales tiene una velocidad de

bit de 8448 Kb/s, mientras el sistema MIC de 24 canales alcanza una velocidad de bit de 6312 kb/s.

N

1

Múltiplex

Primario

MIC

2

3

Múltiplex

Digital

de

Segundo

Orden

Múltiplex

Digital

de

Segundo

Orden

4

N=30

N=24

1

Múltiplex

Primario

MIC

2

N

3

4

2048 kbit/s

1544 kbit/s

8448 kbit/s

6312 kbit/s

2048 kbit/s

1544 kbit/s

N=30

N=24

)LJXUD

Los sistemas de transmisión digital pueden agruparse jerárquicamente, del mismo modo que los sistemas de

Multiplexación por División de Frecuencia (MDF; Frequency Division Multiplexing, FDM). La Figura 2 muestra una

jerarquía de múltiplex digital, basada en el sistema MIC de 30 canales. Obsérvese que las facilidades de transmisión

pueden usarse no sólo para voz modulada por impulsos codificados, sino también para datos, video-teléfono, grupos

MDF y televisión

F

30

Datos

F

120

1er orden

2.048 Mbit/s

Multiplexor

Primario

MIC

Multiplexor

de

Datos

Multiplexor MIC

de

Segundo Orden

Codificador de

Video-teléfono

2do orden

8.448

3er orden

34.368 Mbit/s

4to orden

139.264 Mbit/s

1

2

3

4

Multiplexor

Digital

de

Segundo

Orden

1

2

Multiplexor

Digital

de

Tercer

Orden

3

4

1

1

2

3

4

MDF de Grupo

Maestro

Multiplexor

Digital

de

Cuarto

Orden

2

3

4

Codificador de

TV

)LJXUD

Multiplexor

Digital

de

Quinto

Orden

5to orden

~565 Mbit/s

-2-

1.2

(O0~OWLSOH['LJLWDOGH6HJXQGR2UGHQ

Los principios básicos para la multiplexión digital son los mismos en todas las etapas jerárquicas. La

multiplexión en el multiplexor de segundo orden puede, por tanto, servir como un modelo general. El principio más

importante para la multiplexación digital es el proceso de entrelazamiento de bits, en el cual los tributarios son

combinados bit por bit en un solo flujo de bits de salida común. (Ver Figura 3).

Entrelazamiento de Bit

1234

1234

1234

1234

)LJXUD

Cuando entran al entrelazador de bits, los cuatro tributarios tienen que estar sincronizados. Todos los multiplexores

primarios tienen relojes trabajando independientemente y dan por consiguiente, flujos de bits con ligeras diferencias de

velocidades de bits y por lo tanto, fases diferentes.

Para lograr la sincronización entre los tributarios, se colocan almacenadores o memorias intermedias (buffert memories)

entre los tributarios y el entrelazador de bits. Esto se muestra en el diagrama de bloque, en la Figura 4. La

sincronización se logra ahora por la lectura de bits de la memoria intermedia con una velocidad de bit más alta que

cuando se escriben los bit en ella. La velocidad de lectura es de 2112 Kb/s, dando por consiguiente, una velocidad de

bit de segundo orden de 4 x 2112 = a 8448 Kb/s. Una unidad de control ordena la lectura de las cuatro memorias

intermedias al mismo tiempo. La lectura tiene que hacerse en cascada (formando subtramas) a causa de la mayor

velocidad de bit.

Tributario 1

Memoria

Intermedia

2112 kb/s

2

Entrelazador

de Bits

3

4

Unidad de

Control

)LJXUD

8448 kb/s

-3-

La estructura de trama de segundo orden es determinada por la unidad de control donde la palabra de alineación

de trama de servicio secundario (1111010000), dos bits de servicio y bits de control de justificación, se insertan dentro

del tiempo disponible entre las cascadas (subtramas) - ver Figura 5.

212

Palabra de alineación

de Trama

1111010000

I

1234

1

N

1234

50

Bit para uso nacional

Bits

Contr.

Justif. 1

1234

Bit para transmisión de alarma

1234

51

1234

102

Bits

Contr.

Justif. 2

1234

636

1234

103

1234

154

Bits

Contr.

Justif. 3

1234

424

848

1234

155

1234

156

1234

206

Bits disponibles

para justificación

)LJXUD

Aquí los bits de control de justificación y la palabra de cuatro bits No. 155, requieren una explicación

más detallada. Ya que a las velocidades de bit de los tributarios se les permite variar algo de su valor nominal de 2084

Kb/s mientras la velocidad de lectura de la memoria intermedia es siempre constante, existe un riesgo de agotar algunas

memorias intermedias. El riesgo se elimina deteniendo la lectura de esa memoria durante el período de un bit. La

palabra de cuatro bits No. 155 (un bit/tributario) se reserva para este propósito. Las posiciones del bit contienen ya sea

información de los tributarios o de los bits redundantes, dependiendo de la carga de las memorias intermedias.

Si una de las posiciones del bit en la palabra de bit No. 155 lleva información de tributarios, los tres bits de

control de justificación correspondientes se fijan a UNO, de otro modo, se fijan a CERO. El multiplexor receptor puede

entonces tomar una decisión mayoritaria por medio de los tres bits de control de justificación. Consecuentemente, un

error de un bit aislado no alterará el resultado.

En la dirección receptora, la palabra de alineación de trama se usa como referencia cuando se divide la señal

digital de entrada en sus componentes. El estado de los bits de control de justificación se anota, y las palabras de bits

No. 155 no deseados se remueven.. Los bits se escriben en memorias intermedias a fin de suavizar variaciones en la

transmisión. La lectura de las memorias intermedias toma lugar a la misma velocidad de bit que el promedio de la señal

original del tributario.