Solución problemas examen 98.fm

Anuncio

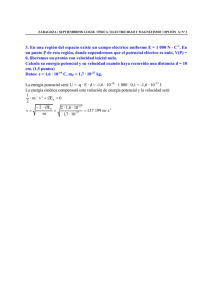

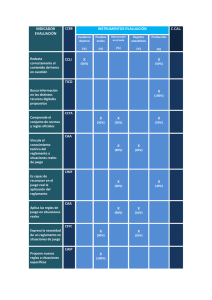

3UR E OP D H Se desea construir un sumador binario con aceleración de arrastres (SBAA) para 2 números binarios X e Y de 3 bits cada uno. Para ello, el diseño se realizará siguiendo los siguientes pasos: A) (1.5 puntos) La figura de la izquierda muestra un sumador binario completo modificado (SBC modificado) con dos entradas de datos xi e yi y un acarreo de entrada ci-1. Exprese la función lógica de sus cuatro salidas: si (suma), ci (acarreo de salida), gi (generación de acarreo) y pi (propagación de acarreo). A partir de estas funciones lógicas, y empleando únicamente puertas lógicas, diseñe este SBC modificado. B) (1.5 puntos) La figura central muestra un circuito de aceleración de arrastres (CAA) de 3 bits con tres entradas de generación de acarreo gi, tres entradas de propagación de acarreo pi y un acarreo de entrada c-1. Exprese las funciones lógicas de los acarreos c2, c1 y c0 generados por este módulo. A partir de estas funciones lógicas, y empleando únicamente puertas lógicas, diseñe este CAA. C) (1 punto) Utilizando únicamente 3 SBC modificados como los diseñados en A) y el CAA diseñado en B), construya razonadamente el sumador binario con aceleración de arrastre de 3 bits (SBAA) solicitado en el enunciado y mostrado en la figura de la derecha. xi ci SBC modificado si g2 yi gi p2 ci-1 pi g1 p1 g0 p0 c-1 CAA c2 c1 x2 y2 c2 c0 s2 6RO X F y QL A) Las expresiones que vamos a utilizar para implementar el SBC modificado son: g i = xi y i Si = xi ⊕ yi ⊕ ci-1 = pi ⊕ ci-1 ci = xi yi + (xi ⊕ yi) ci-1 = gi + pi ci-1 y el circuito correspondiente es el mostrado en la Figura 98-3-2. y1 x0 y0 c-1 SBAA de 3 bits Figura 98-3-1: Módulos del problema p i = xi ⊕ y i x1 s1 s0 ci-1 yi xi • yi • xi • ci • • SBC modificado ci-1 • si gi pi gi ci si pi Figura 98-3-2: SBC modificado B) Para construir las expresiones de c2, c1 y c0 generados por este módulo a partir de las entradas de generación de acarreo gi (i=1,2,3), las entradas de propagación de acarreo pi (i=1,2,3) y el acarreo de entrada c-1, se comienza por la expresión de c0 y luego se va sustituyendo su valor en las siguientes. c0 = g0 + p0 c-1 c1 = g1 + p1 c0= g1 + p1 (g0 + p0 c-1) = g1 + p1 g0 + p1 p0 c-1 c2 = g2 + p2 c1= g2 + p2 (g1 + p1 g0 + p1 p0 c-1)=g2 + p2 g1 + p2 p1 g0 +p2 p1 p0 c-1 El circuito resultante se muestra en la Figura 98-3-3. C) Los tres SBC modificados y el CAA los podemos conectar según se muestra en la Figura 98-3-4. En este diseño se puede observar cómo los arrastres que se introducen en los SBC modificados son los generados directamente por el módulo CAA y que, sin embargo, los arrastres generados por estos SBC modificados se quedan sin utilizar. Esta es la idea fundamental de esta técnica. p2 • g2 • • p1 • g1 • • p0 g0 p2 g2 • • • • • p1 g1 p0 g0 c-1 • c-1 CAA c2 c2 c1 c1 c0 c0 Figura 98-3-3: Circuito de aceleración de arrastres (CAA) x2 c2 y2 x1 c1 SBC x0 c0 SBC Modificado Modificado g2 p2 y0 SBC Modificado s1 c2 • g0 p0 g1 p1 c1 s2 y1 c0 s0 CAA y2 x2 c2 y1 x1 y0 x0 c-1 SBAA s2 s1 s0 Figura 98-3-4: Sumador binario de 3 bits con aceleración de arrastre c-1