circuitos de muestreo y retención - U. T. F. S. M.

Anuncio

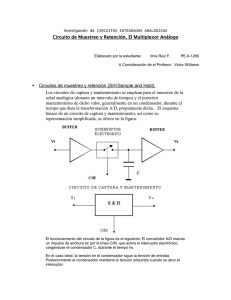

CIRCUITOS DE MUESTREO Y RETENCIÓN (SAMPLE & HOLD) INTRODUCCIÓN Los circuitos de muestreo y retención se utilizan para muestrear una señal analógica en un instante dado y mantener el valor de la muestra durante tanto tiempo como sea necesario. Los instantes de muestreo y el tiempo de retención están determinados por una señal lógica de control, y el intervalo de retención depende de la aplicación a la que se destine el circuito. Por ejemplo, en los filtros digitales las muestras deben ser mantenidas durante el tiempo suficiente para que tenga lugar la conversión de analógica a digital. CIRCUITOS DE MUESTREO Y RETENCIÓN La mayoría de los circuitos de muestreo y retención utilizan un condensador para mantener la tensión de muestra. El interruptor controlado electrónicamente es el medio para cargar rápidamente el condensador hasta la tensión de muestra y luego suprimir la entrada de manera que el condensador pueda retener la tensión deseada. Tal circuito está representado en la Figura 1-1a, en la que VA es la fuente analógica y Rg su impedancia interna. Las formas de onda ideales están representadas en la Figura 1b. El interruptor está cerrado mientras la forma de onda lógica de control vc está en nivel alto y, en el supuesto de que la constante de tiempo RgC sea muy pequeña, la tensión de salida seguirá muy estrechamente a la tensión de entrada y será igual a ella en el instante en que el circuito lógico de control esté a nivel bajo, abriendo el interruptor. Durante el intervalo de retención, mientras la señal de control está en nivel bajo, el interruptor está abierto y el condensador C mantendrá el último valor de la entrada. Idealmente la salida se mantendrá constante en ese valor durante todo el intervalo de retención. Figura 1. Circuitos de muestreo y retención: (a) circuito simple con interruptor, (b) formas de onda. 1 En la práctica, los interruptores electrónicos y los condensadores no son perfectos y presentan discrepancias respecto a los valores o estados ideales. Entre las especificaciones más importantes están las de tiempo de apertura y tiempo de adquisición. Se puede explicar lo que es el tiempo de apertura haciendo referencia a la Figura 2 en la cual vemos que dicho tiempo es el máximo retardo entre el instante en que la lógica de control ordena al interruptor que se abra y el instante en que realmente ocurre la apertura. El tiempo de apertura de un sistema determina esencialmente el tipo de interruptor que se debe utilizar. Si este tiempo es del orden de milisegundos, S puede ser un relé. Con interruptores FET los tiempos de apertura son normalmente de 50 a 100 ns, mientras que con interruptores con diodo muy rápidos el tiempo de apertura es mucho menor de 1 ns. A consecuencia del tiempo de apertura hay una incertidumbre en el ritmo o cadencia de muestreo que puede degradar las prestaciones del sistema. Se suele seleccionar un interruptor cuyo tiempo de apertura sea mucho menor que la inversa del ritmo de muestreo. Como el circuito de salida es capacitivo, tarda un cierto tiempo antes de que la tensión del condensador (salida) sea idéntica a la entrada. El tiempo de adquisición (Figura 1-3) es el intervalo más corto transcurrido desde que se da la orden de muestra hasta que se puede dar la orden de retención y se obtenga como resultado una tensión de salida que sea aproximadamente la tensión de entrada con la exactitud necesaria. El caso más desfavorable ocurre cuando la entrada es una función escalón cuya amplitud es igual a la máxima excursión de tensión cresta a cresta del circuito. En el circuito de la Figura 1a, la velocidad con que la salida puede seguir a tal entrada depende de las características de la fuente de señal vA. Considerando el efecto de la impedancia de fuente Rg, vo será una función exponencial con constante de tiempo RgC, y para que vo no difiera más de 0,01 por 100 de la entrada en el instante requerido el tiempo necesario es, aproximadamente, 9 RgC. Además, la fuente de señal debe ser capaz de suministrar la corriente de carga requerida por el condensador C. Usualmente, entre la entrada analógica y el interruptor se intercala un operacional seguidor de tensión para conseguir que Rg sea muy pequeña. 2 Figura 2. Tiempo de apertura y su efecto. Figura 3. Tiempo de adquisición El fabricante suele especificar el tiempo de establecimiento. Este es el tiempo que transcurre desde la apertura del interruptor (retención) hasta que la salida ha alcanzado su valor final, dentro de un porcentaje especificado (generalmente, el 0,01 por 100 del valor a fondo de escala). Si el circuito de muestreo y retención está seguido de un convertidor A(D, la conversión no comienza hasta que la señal sea estable o de lo contrario la tensión convertida puede ser errónea. También se especifica algunas veces la velocidad de caída de la salida. Esta representa la variación de tensión entre las placas del condensador durante el tiempo de retención y es inversamente proporcional a la capacidad ya que dvo / dt = I/C, donde I es la corriente de fugas del condensador. La corriente de fugas puede ser consecuencia de la de polarización del operacional, la de fugas en el interruptor o las fugas internas en el condensador. Circuito práctico Los circuitos prácticos de muestreo y retención usan operacionales para obtener una baja impedancia en el circuito de excitación y una alta impedancia de carga en el condensador de retención. Estos circuitos utilizan conmutadores FET en vez de BJT a causa de la linealidad y carencia de offset en sus características de transferencia en la proximidad del origen, donde tiene lugar la acción de conmutación. Si se requiere una velocidad extremadamente alta se utilizan puentes de diodos para la conmutación. La Figura 4a, representa un circuito inversor de muestreo y retención. Opera tal como sigue. Cuando S está cerrado (muestreo), el circuito actúa como un filtro RC convencional realizado con un operacional. Si se aplica un escalón de amplitud VA a la entrada, la salida será: − t / R2C R2 (1 − ε v o (t ) = − V A R1 ) 3 Evidentemente, la constante de tiempo R2C debe ser mucho más corta que el intervalo de muestreo para que la salida pueda seguir a la entrada. Cuando se abre el interruptor se mantiene la tensión VA en el condensador. Como antes dijimos, el condensador no puede mantener esta tensión indefinidamente debido a la corriente de polarización de entrada requerida por el operacional y a la corriente interna de fugas del condensador y del interruptor. Para minimizar este efecto de caída se debe utilizar el mayor valor de C consistente con los requisitos de tiempo de adquisición. El operacional debe tener la menor corriente de polarización posible por lo que es adecuado un operacional con etapa de entrada FET. Además, el condensador debe ser del tipo de alta calidad y bajas fugas. Figura 4. Circuito inversor de muestreo y retención: (a) circuito con interruptor, (b) uso del interruptor FET. La Figura 4b representa el circuito inversor de muestreo y retención con FET, T1 es el conmutador, que es un FET de empobrecimiento de canal p. En este tipo de transistor la corriente circula cuando la tensión fuente-puerta es cero y disminuye a medida que se hace más negativa. Una tensión umbral típica es VT = VSG = -4 V. Veamos cómo funciona este conmutador en el circuito de la Figura 4b Primero consideramos que la tensión de control Vc sea + 5V, es decir, que estamos en el intervalo de retención, en el que el interruptor está abierto, y que la tensión de entrada analógica VA es positiva. En este caso, toda corriente que pase por T1 debe circular desde a hasta b, de modo que a actuará realmente como fuente y b será el drenaje. La presencia del diodo D hace que la tensión en a sea fijada en el nivel de 0,7 V, por lo que VSG nunca superará los 0,7 - 5 = 4,3 V, independientemente de VA. Así, T1 se mantendrá en corte (interruptor abierto) y si la tensión umbral VT es -4 V, la tensión fuente-puerta será 0,3 V más negativa que la necesaria para poner a T1, en corte. Entonces, tendremos un margen de seguridad de 0,3 V. 4 Si la tensión analógica VA tiende a ser negativa, las misiones de los terminales a y b se invertirán, convirtiéndose b en la fuente. Con el terminal de entrada del operacional a la tensión virtual de masa, T1 se mantiene en corte a causa de que los 5 V aplicados en la puerta dan un margen de 1 V por encima de la tensión umbral de -4 V. En el intervalo de muestreo, VC tiende a cero, y T1 está en conducción (el interruptor está cerrado). Entonces el circuito actúa esencialmente como el circuito simplificado de la Figura 4a. Cuando T1 conduce, el diodo D está conectado en paralelo con el interruptor FET. Como la caída en el FET es pequeña, la tensión en los terminales del diodo será pequeña y mucho menor de los 0,7 V de muestreo. Es interesante observar que en este circuito el funcionamiento del FET es reversible o bilateral, en cuanto que fuente y drenaje son intercambiados cuando cambia la polaridad de la entrada. Muestreo de una señal de audio. Por definición, el muestreo es el registro parcial de un conjunto de datos. Aplicado al muestreo de una señal de audio, que varía con el tiempo, el muestreo consiste en la medición intermitente, discontinua, de la señal. Para simplificar, el tiempo transcurrido entre una observación y otra se hace constante. En la Fig. 5 se muestra el proceso básico seguido por una señal de audio (o cualquier otro tipo de señal) para ser convertida en una secuencia de sus muestras. A esta secuencia de muestras nosotros la conoceremos como señal modulada por amplitud de pulso, o sencillamente señal PAM (del inglés "Pulse Amplitud Modulation "). 5 Fig. 5 Modulación PAM. Observe ( Fig. 5) que la señal PAM podemos imaginar que se produce al meter a la señal de audio por un circuito de conmutación, controlado por las señales de muestreo y descarga. El proceso de muestreo se describe con más detalle en la Fig. 6. Cuando la señal de muestreo cierra al interruptor SW1 en t0, con SW2 abierto, el voltaje que en ese momento tenga la señal de audio carga al capacitor C. Luego, en t1, el interruptor SW1 se abre, y durante un tiempo el capacitor C se mantiene cargado, reteniendo el voltaje de la muestra. Posteriormente, en t2, el interruptor SW2 se cierra, descargando al capacitor C. El interruptor SW1 se mantendrá abierto y el interruptor SW2 se mantendrá cerrado hasta el 6 momento que se inicie el próximo ciclo de muestreo, en t3. Debido al comportamiento descrito, a los circuitos que se comportan como éste se les llama circuitos de muestreo y retención, abreviadamente S/H (del inglés, "Sample and Hold"). Fig. 6. - Proceso de muestreo y retención. Para generar una señal PAM como la mostrada en la Fig. 5. se requiere que el tiempo entre una muestra y otra sea constante, a este tiempo se le llama período de muestreo, Ts (del inglés, "Sampling Time"). Al valor inverso de este tiempo se le llama, consecuentemente, frecuencia de muestreo, fs (del inglés, "Sampling frequency"): fs = 1 / Ts Según veremos (inciso 2.3.1), la frecuencia de muestreo escogida en audio digital es de 44.1 KHz. 7 Observando a la señal PAM (Fig. 5) se hace evidente que la señal de audio original está contenida en la envolvente de los pulsos de voltaje. La señal PAM es cualitativamente semejante a la que se obtiene en un circuito recortador de señal AM ( Fig.7). Una señal AM recortada (Fig.7) también es una secuencia de pulsos. En una señal AM recortada la envolvente contiene la información de la señal original (de audio, por ejemplo). Esta envolvente puede ser recuperada haciendo pasar a la señal AM recortada por una red RC configurada como filtro paso bajo (Fig.7). 8 Fig. 7. - Demodulación de una señal AM. 9 Así mismo, como la señal AM recortada, la señal PAM puede hacerse pasar por un filtro paso bajo, de tal forma que se recupere su envolvente (Fig.8) Fig. 8. - Proceso básico de modulación y demodulación PAM. ELECCIÓN DE LA FRECUENCIA DE MUESTREO Cambiemos el tema - ¿Qué tal si hablamos de política? Al hacerse las votaciones para la elección de un presidente nacional es importante que vote la mayoría de los habitantes con derecho al voto, pero no es del todo necesario que voten todos. Y efectivamente es así, es imposible que voten todos. 10 Si el número de votantes resultara muy inferior al número de habitantes con derecho al voto, el liderazgo del presidente escogido sería cuestionable. Posiblemente la gente no votó porque no había candidatos aceptables, o alguna otra razón. Por este motivo, antes de las votaciones se lanzan campañas publicitarias en donde se invita a la gente a votar. Y más aún, existen países en donde constitucionalmente se establece que el número de votos captados por algún candidato debe ser superior a cierto porcentaje de la población. Las votaciones son en realidad un muestreo de opinión en donde se intenta descubrir lo que piensa la mayoría. Además, como hemos mencionado, para que tengan validez se requiere que el número de muestras (votantes) sea aceptable. Retomando nuestro tema - ¿O quiere seguir hablando de política? - Con respecto a las votaciones, en el muestreo de una señal de audio tenemos el mismo problema en cuanto al número de muestras que deberán ser tomadas. Afortunadamente todo el control lo tenemos nosotros y no tenemos que hacer campañas publicitarias. El número de muestras que se tomen en un proceso de muestreo está controlado por la frecuencia de muestreo. Mientras más frecuencia, más muestras. Por lo tanto, para que la señal muestreada (señal PAM) sea representativa requerimos establecer cuál debe ser esta frecuencia. Para deducir la regla que nos diga cuál ha de ser la frecuencia de muestreo, haremos algunos experimentos que describimos a continuación. 11 En la Fig.9 se presenta el muestreo de una señal de audio de 22 KHz por una señal de muestreo de 176 KHz. Note que la forma de la envolvente de la señal PAM resultante es bastante semejante a señal original. Fig. 9. - Muestreo a 176 KHz. En la Fig.10 se presenta a la misma señal de audio de 22 KHz muestreada ahora por una señal de 88 KHz. La forma de la envolvente de la señal PAM resultante sigue siendo 12 semejante a señal original. Fig. 10. - Muestreo a 88 KHz. 13 En la Fig. 11 se presenta a la misma señal de audio de 22 KHz muestreada ahora por una señal de 44 KHz. La forma de la envolvente de la señal PAM resultante sigue siendo semejante a señal original, aunque ahora el trazo de esta envolvente no es tan claro Fig. 11 - Muestreo a 44 KHz. 14 En la Fig. 12 se presenta a la misma señal de audio de 22 KHz muestreada ahora por una señal de 29.33 KHz. La forma de la envolvente de la señal PAM aparenta que la señal original tiene una frecuencia de 7.33 KHz. Con esta frecuencia de muestreo se genera una frecuencia nueva, inexistente en la señal original. Fig. 12 - Muestreo a 29.33 KHz. Habiendo comprendido la mecánica de estos experimentos, en la Fig 13 presentamos nuevamente a la señal de audio de 22 KHz muestreada a las frecuencias de 176 KHz, 15 88KHz, 44 KHz, 29.33 KHz y, además, se considera el muestreo a 22 KHz, 17.6 KHz y 14.66 KHz. Observe que la envolvente de la señal PAM resultante mantiene la frecuencia de la señal de audio original solamente si la frecuencia de muestreo es igual o superior a 44 KHz. Para frecuencias de muestreo inferiores a 44 KHz, la frecuencia aparente de la envolvente varía al variar la frecuencia de muestreo. A estas frecuencias aparentes, no contenidas en señal original, las llamaremos frecuencias seudónimas (en inglés, "alias frequency" o "foldover frequency"). Fig. 13. - Señal PAM resultante para diferentes frecuencias de muestreo. La frecuencia de muestreo de 44 KHz es dos veces la frecuencia de la señal de audio muestreada, de 22 KHz. Este experimento ilustra la más importante de las conclusiones relacionadas con el procedimiento de muestreo de una señal: 16 Para que la señal original pueda ser recuperada de su correspondiente señal PAM, la frecuencia de muestreo deberá ser mayor que el doble de la máxima frecuencia contenida en la señal original. Esta conclusión, llamada Teorema de Muestreo, puede que le haya parecido complicada. Realmente, su interpretación es muy sencilla. Considere el espectro de amplitud frecuencia de una señal arbitraria (de audio si gusta) que se muestra en la Fig.14 Fig. 14. - Espectro de amplitud - frecuencia de una señal de audio arbitraria. AMPLITUD 5 10 17 15 FRECUENCIA [KHz] Observe (Fig.14) que esta señal contiene armónicas de 5 KHz, 10 KHz y 15 KHz. La frecuencia máxima es, evidentemente, 15 KHz. Por lo tanto, para muestrear a esta señal se requerirá una frecuencia de muestreo superior a: 2 x 15 KHz = 30 KHz La señal podrá muestrearse con una frecuencia de muestreo de 50 KHz, por ejemplo. Como sabemos la percepción humana del sonido está entre las frecuencias de 20 Hz y 20000 Hz. Por lo tanto, si de alguna manera elimináramos a las frecuencias superiores a 20 KHz, la señal de audio resultante mantendrá casi que todas las propiedades audibles de la señal original (Fig.15). Siendo rigurosos, realmente la señal resultante pierde frecuencias que por sí solas no son audibles, pero que al formar parte de una señal compleja contribuyen a resaltar las frecuencias audibles, por el efecto de suma de sonoridades. Sin embargo, esta leve diferencia con respecto a la señal original sólo será percibida por personas con un vasto entrenamiento musical. 18 Fig. 15. - Eliminación de las componentes de frecuencia superiores a 20 KHz. El límite de frecuencia inherente a la percepción auditiva humana hace posible que definamos la frecuencia de muestreo usada en audio digital. Ya que en un sonido audible la frecuencia máxima a considerar es de 20 KHz, la frecuencia de muestreo de una señal de audio se especifica de 44.1KHz, mayor que 40 KHz (2 x 20 KHz). Para garantizar que la señal de audio muestreada no contenga componentes armónicas superiores a los 20 KHz, antes de muestrear se requiere filtrar a la señal original. Si no se filtrara, y si la señal original contuviera frecuencias arriba de 20 KHz, al detectar la envolvente de la señal PAM resultante obtendríamos componentes audibles de sonido que no existían en el sonido original. 19 Fig. 16. - Prevención contra la formación de falsas armónicas mediante la inclusión de un filtro pasa bajo previo al circuito de muestreo y retención. Al filtro paso bajo que evita la aparición de frecuencias seudónimas, por su función se le conoce como filtro contra frecuencias seudónimas (del inglés "antialiasing filter"). EJERCICIOS Y APLICACIONES 20 EJERCICIOS. EJERCICIOS RESUELTOS. 1. - Un circuito de muestreo y retención tiene un condensador de 50 pF y la corriente de fugas en modo de retención es de 1 nA. Si el intervalo de retención es de 50 µs y la tensión de retención es 1 V, hallar el porcentaje de caída. La resolución del ejercicio esta dirigida en la ecuación por la ecuación de la corriente en el condensador: Ic = C ⋅ ∆Vo ∆t (1) donde: Ic = 1[nA] . ∆t = 50[µs ] . C = 50[ pF ]. con estos valores reemplazándolos en la ecuación (1), se tiene: 10 −9 × 50 ⋅ 10 −6 ∆Vo = 50 ⋅ 10 −12 ∆Vo = 10 −3 [V ] Para obtener el porcentaje de caída, se tiene una simple regla de tres. 10 −3 × 100 1 %caida = 0.1% %caida = 21 2. - En un circuito dado de muestreo y retención el condensador es de 100 pF y la resistencia de fugas equivalente en el modo de retención es de 15 GΩ. Calcular el porcentaje de caída si el intervalo de retención es de 100 µs. En la solución de este problema se utiliza la ecuación del voltaje del condensador en el tiempo. Vc ( t ) = Vf + (Vi − Vf ) ⋅ e Donde: −t RC Vf = 0 Vi = Vo t = 100[µs ] R = 15[GΩ]. C = 100[ pF ]. Reemplazando los valores en la ecuación se tiene: Vc ( t ) = Vo ⋅ e − 100 ⋅10 −6 15 ⋅10 9 ⋅100 ⋅10 − 12 Vc ( t ) = 0 . 99993 Vo ∴ %caida = 0.007% De aquí se puede concluir que mientras más grande sea la resistencia de fugas en modo retención el circuito de SAMPLE & HOLD sigue con mayor precisión a la entrada. 3. - En el siguiente circuito, R1=R2=15 KΩ y en el intervalo de muestreo de 50 ns. Hallar C para que la salida siga a la entrada con una diferencia que no exceda de 0.1 por 100. 22 R1 R2 Va Muestra S C Vo (a) En la solución de este problema se ocupa la siguiente ecuación: Vo(t ) = Va −t R2 + (1 − e RC ) R1 donde: t = 50 µs R1 = R 2 = 15 KΩ Además se quiere que Vo = 0.9Va Reemplazando los valores se tiene: Vo(t ) = −Va(1 − e 1.9 = e − 50⋅10 − 9 −50⋅10 −9 15⋅103 ×C ) 15⋅103 ⋅C Aplicándole logaritmo natural a la ecuación para despejar C, se tiene: 23 ln(0.1) = C= − 50 ⋅ 10 −9 15 ⋅ 10 3 ⋅ C − 50 ⋅ 10 −9 15 ⋅ 10 3 ⋅ −2.3 C = 1.45[ pF ] EJERCICIOS PROPUESTOS. 1. – A propósito del estudio del tiempo de adquisición, demostrar que se requiere 9RgC para que Vo no se diferencie en mas de 0.01 por 100 de la entrada. 24 2. - En el siguiente circuito C=500 pF, R1=R2=15 kΩ y la corriente de polarización de entrada del operacional es 300 mA. Calcular el porcentaje de caída si el intervalo de retención es 1 ms y la tensión correspondiente es 1 V. R1 R2 Muestra S C Vo 25 CIRCUITOS DE APLICACIONES En las aplicaciones se tienen una infinidad de circuitos, en los cuales se tienen en sus diversas estructuras, ya sea como una simple malla R-C o en circuitos integrados como los de la serie LF198, LF298, LF398, de los cuales se muestran algunos a continuación: Generador de rampa con nivel variable de reset. 15V R1 8K2 -15V 4 R2* reset level imput 3 1 LF398 output 6 reset D1 LM112 1.2V 8 7 Ch* 5V 0V En este circuito la ecuación de diseño para el tiempo de la rampa es con R2 > 10K. Además se tiene: ∆V 1.2V = ∆T ( R 2) ⋅ (Ch) 26 Amplificador de reset estabilizado (ganancia =1000). 1K 1M V+ 7 V- 2 4 6 Q1 2n5116 imput output LH0042H 12K 1 3 5 200K -15 4 200K +15 1 30K 5 3 LM398 8 7 5V 0V 6 0.033uF reset pulse >2ms 4K7 Las ecuaciones de este circuito son: Vos ≤ 20 µ V Zin ≈ 1 M Ω ∆ Vos ≈ 30 µ V sec ∆t ∆ Vos ≈ 0 .1 µ V °C ∆T 27 Interruptor de dos canales. +15V -15V 1 "A" Imput 3 4 Output LF398 6 7 8 47K "A" select 5V "B" Imput 0V "B" select Tabla Nº2 Características de este circuito como interruptor de dos canales son: Gain Zin BW Crosstalk @ 1 kHz Offset A 1±0.02% 1010Ω ≈1MHz -90db B 1±0.2% 47kΩ ≈400kHz -90db ≤ 6mV ≤ 75 mV 28 Distribuidor de datos. 29 Distribuidor de datos. Amplificador sample and hold. 30 Detector de máximo peak de pulsos rápidos. Integrador de pulsos de ns. 31 Sistema de muestreo simultaneo de varios canales. 32 Sistema de restauración de nivel DC. Sensor remoto de temperatura de bajo costo. 33 Detector de peak. Vout TLC272 1N4148 Vin Además se puede notar que estas son una pequeña parte de las grandes aplicaciones que tienen este tipo de circuito como por ejemplo, en la instrumentación de equipos electrónicos de medición, en estos se encuentra una rama muy importante que es los equipos de mediciones medicas, que son muy importantes en la actualidad y en la vida de todos. Nota: Las aplicaciones propuestas fueron descargadas de los manuales de la NATIONAL y de la BURR – BROWN Burr-Brown WWW.NATIONAL.COM 34 35 36 37 BIBLIOGRAFIA 1. – Schilling, Donald L. Circuitos electrónicos: discretos e integrados. Madrid. McGraw-Hill. 963 p. Enc. Materia: CIRCUITOS ELECTRONICOS. CICUITOS DE TRANSISTORES. 2. - http://www.i-une.com/cgi-bin/go.cgi?0=http://obelix.umh.es/9900/teleco_sist/mpcm/public_html/nyquist.htm 3. – Burr-Brown 4. - http://www.biopsychology.org/tesis_esteve/confund/confund.htm 5.-http://svc.sony-Spa.com/TechSupport/Entrenamiento/Discocompacto/FIGURAS/2-1.htm 6. - WWW.NATIONAL.COM BIBLIOGRAFIA ANEXA 1. Nelson, Troy Nagle, Carroll, “Análisis y diseño de circuitos lógicos”, Prentice Hall 1996 2. Cuesta, Gil Padilla, Remiro, “Electrónica Digital”, McGraw Hill, 1996 3. Remiro, “Lógica Programable” McGraw Hill, 1994 4. Mano, “Logica digital y diseño de computadoras”, Prentice Hall, 1990 38