Final de Junio - Universitat de les Illes Balears

Anuncio

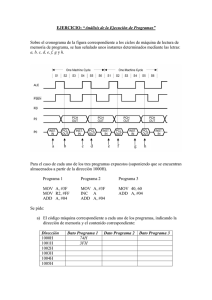

Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 22 de Junio de 2005 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Primer Parcial tiempo asignado: 2h 30’ 5 3P P1. Responder a las siguientes cuestiones sobre el manejo de la pila en los microcontroladores de la familia MCS-51: a) Tomando los valores por defecto del microcontrolador, ¿cuántas llamadas a subrutinas/interrupciones pueden ser recursivamente realizadas como máximo?. b) ¿Qué modo de direccionamiento se utiliza implı́citamente en las instrucciones PUSH y POP?. c) El fragmento de código mostrado en el cuadro 1 corresponde al de una rutina de servicio de interrupción. Se pide: 1) Describir matemáticamente su funcionalidad. 2) Añadir las instrucciones PUSH/POP necesarias para salvaguardar/recuperar el contexto del proceso que ha sido interrumpido. Tener en cuenta que dichas instrucciones sólo permiten el uso del modo de direccionamiento directo. Los registros DPL y DPH son los únicos que no deben salvaguardar su contenido ya que constituyen el output de la rutina. d ) En una rutina de servicio de interrupción, excepcionalmente, puede interesar continuar la ejecución del programa en un punto diferente a aquel donde habı́a sido interrumpido. Suponiendo la dirección de retorno almacenada en memoria RAM interna, escribir el código necesario para llevar a cabo la operación. ¿Se preserva siempre la capacidad útil de la pila tras este tipo de operaciones?. Justifica la respuesta apoyándote en varios ejemplos. Cuadro 1: Una rutina de servicio de interrupción. MOV 08h,00h MOV DPL,#0 MOV DPH,#0 LBL1: MOV A,08h MOV B,A MUL AB JB OV,LBL2 MOV R1,A MOV A,DPL ADD A,R1 MOV DPL,A MOV A,DPH ADDC A,#0 MOV DPH,A SJMP LBL3 5 3P LBL2: MOV R1,A MOV A,DPL ADD A,R1 MOV DPL,A MOV R1,B MOV A,DPH ADDC A,R1 MOV DPH,A LBL3: MOV A,08h DEC A MOV 08h,A JNZ LBL1 RETI P2. Se dispone de una red CAN con tres nodos conectados denominados A, B y C. El controlador del primero de ellos actúa de acuerdo a la especificación CAN 2.0B pasiva, si bien los nodos restantes se rigen por Extended CAN. En un determinado momento, el nodo A inicia la transferencia de un mensaje de tipo/clase 20 con los siguientes datos: 31, 97 y 251. Se pide: 1 a) Construir la trama de datos enviada por el controlador CAN de dicho nodo al bus. Para ello, tener en cuenta que el valor del CRC tras procesar el segundo byte de datos es 2F26h. b) Explicar con detalle el proceso de detección y tratamiento de errores para la siguiente situación de error: el nodo B recibe un bit de valor lógico complementario al hallado en el bus durante la recepción del decimoquinto bit. 5 3P P3. Responder a las siguientes cuestiones acerca del bus USB: a) ¿Qué tipo de topologı́a adopta el bus?. ¿Qué restricciones se han impuesto sobre la misma para acotar los tiempos de propagación de las señales entre el host y los dispositivos/funciones?. b) Describir el mecanismo de arbitraje utilizado. ¿Es, al igual que en CAN e I2C, ’no destructivo’ ?. c) Supón que en un determinado momento se lleva a cabo una transferencia de interrupción entre el host y el dispositivo 121 a través del endpoint 2. El host recibe del bus los siguientes datos: 23, 232 y 175. Detallar la estructura lógica y secuencia de todos los paquetes de los que consta dicha transferencia de acuerdo al cuadro 2. Finalmente, para el segundo de los paquetes, mostrar la secuencia de bits que viajará por el bus. Cuadro 2: Listado breve de identificadores de paquetes junto con su correspondiente valor numérico. Tipo PID IN OUT DATA0 DATA1 ACK NAK 2 Valor 9 1 3 11 2 10 Escuela Politécnica Superior Universitat de les Illes Balears Ingenierı́a Técnica Industrial 22 de Junio de 2005 EXAMEN FINAL DE INFORMÁTICA INDUSTRIAL Segundo Parcial tiempo asignado: 2h (2,5P) P1. Disponemos de una memoria cache con una función de correspondencia directa un tanto especial dada por la expresión i = (j / m) mod m, en donde j representa un número de bloque de memoria principal, m el número total de lı́neas de cache e i el número de lı́nea de cache en el que deberá ser ubicado dicho bloque de datos. Se pide: a) ¿Cómo se distribuyen los bloques en cache?. ¿Conducirá, en general, esta nueva función de correspondencia a mejores tasas de acierto (H)?. Justifica la respuesta. b) Para posibilitar la distribución previa de bloques, desde un punto de vista lógico, ¿cómo deberá ser interpretada una dirección de memoria?. c) ¿Se impone alguna restricción más severa en relación al tamaño mı́nimo que debe tener la memoria principal?. Comparar con el enfoque original. d ) ¿Puede el número de bloques asignado a cada lı́nea de cache ser diferente?. En cualquier caso, determina esa información suponiendo un m = 4, bloques de 8 palabras de 64 bits cada una y un tamaño de memoria principal de 1MB. (2,5P) P2. Considerar una memoria principal de 64 bits con un factor de entrelazado K = 4 y una capacidad total de 256MB. Los bancos de memoria tienen caracterı́sticas idénticas soportando, única y exclusivamente, módulos de memoria SO-DIMM. Por otro lado, la verificación de la integridad de los datos se lleva a cabo mediante un código tipo SEC basado en la codificación propuesta por Richard Hamming. A modo de recordatorio, la relación entre el tamaño M de la palabra/fragmento de palabra almacenada en el módulo de memoria y la longitud N del código viene dada por la expresión 2N − 1 ≥ M + N . Proponer un diseño detallado de memoria principal en donde el coste de cada SO-DIMM sea mı́nimo. Para ello, deberéis tener en cuenta la gráfica de la figura 1. Allı́ se muestra la evolución del coste unitario de los dos tipos de chips DRAM, 32K x 8 y 128K x 4, que pueden ser utilizados. Debéis encontrar a partir de la capacidad de cada módulo de memoria la combinación de chips de cada tipo que minimiza el coste. Coste ( ) 7,50 4,50 4,00 32K x 8 128K x 4 1,50 0,00 1 Unidades 1500 Figura 1: Coste unitario de dos chips DRAM dependiendo del número de unidades de compra. 3