4. evaluación - Universidad de Especialidades del Espíritu Santo

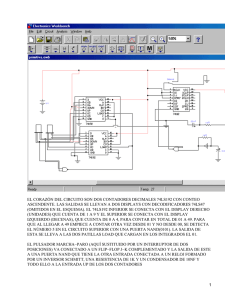

Anuncio

UNIVERSIDAD DE ESPECIALIDADES ESPIRITU SANTO FACULTAD DE SISTEMAS TELECOMUNICACIONES Y ELECTRONICA SYLLABUS MATERIA: PROFESOR(A): CRÉDITOS: PRE REQUISITOS: HORAS PRESENCIALES: Sistemas Digitales II Ing. Marcos Tobar Moran 3 48 H. HORARIO: SEMESTRE: DÍAS: AULA: HORAS NO PRESENCIALES: 48 H. 1. DESCRIPCIÓN SINTÉTICA (Course Description) El profesional de Ingeniería en Sistemas telecomunicaciones y electrónica debido al avance de la tecnología debe tener conocimientos de Hardware como son los circuitos integrados de pequeña, mediana, gran escala y elementos de memoria que se utilizan para construir sistemas digitales con lógica secuencial. Para ello debe tener una comprensión profunda de la forma en la que trabajan los sistemas digitales y ser capaz de aplicar sus conocimientos al análisis y detección de fallas de cualquier sistema digital en lo que respecta a circuitos lógicos secuenciales y sistemas que manejan un mayor numero de variables de control. El principal objetivo de la asignatura es el análisis, diseño e implementación de cualquier sistema digital, especialmente de sistemas de múltiple entrada-múltiple salida. El estudiante aprenderá a interconectar módulos de construcción (circuitos integrados de pequeña, mediana y gran escala) que funcionaran bajo la supervisión de un controlador secuencial que coordinara las diferentes acciones preestablecidas por un algoritmo de control con la finalidad de lograr un determinado trabajo. 2. METODOLOGÍA (Methodology) El dictado estará regido por el programa de estudio de la materia siguiendo el cronograma establecido, por lo cual el dictado de la materia se dará por terminado sólo si el material ha sido cubierto en su totalidad. La nota de evaluación en la materia deberá distribuirse de la siguiente manera: 50% el examen y el 50% restante correspondiente a lecciones, deberes, trabajos en clases. Es obligación del profesor entregar por escrito al estudiante las políticas de la materia, el cual contiene su ponderación y distribución del puntaje, fecha de exámenes y reglamentos concernientes al Sistema de Evaluaciones, Asistencia a Clases y Disciplina. NOTA: Los estudiantes deben adelantar la lectura comprensiva de los contenidos programados para cada sesión. Así la elaboración del conocimiento en la clase resultará rápida, consistente, significativa y gratificante. Los deberes y trabajos no entregados en la fecha señalada serán sancionados hasta con el 30% de la nota. 3. CONTENIDO PROGRAMÁTICO (COURSE OUTLINE) FECHA Unidad / Contenido Unidad 1: Fundamentos de la maquina secuencial Presentación de la asignatura. Entrega del programa y explicación de los criterios de evaluación al alumno. Presentación de textos guías y complementarios. Generalidades Conceptos de memoria. La celda binaria Tarea: Ejercicios Propuestos. Sesión 1 Sesión 2 Sesión 3 Sesión 4 Sesión 5 Horas no presénciales Evaluación Investigar sobre memoria y celda binaria Participación en clases Investigar sobre los Flip Flops Participación en clases. Los Flip Flop Tarea: Desarrollar ejercicios propuestos en clases. Investigar sobre Circuitos de reloj Participación en clases. Revisión de los E.P. en la clase anterior.(evaluación en el pizarrón). Los circuitos de reloj Tarea: Ejercicios propuestos en clases. Investigar sobre los tipos de Flip Flop Participación en clases. Los tipos de Flip Flop: El Flip Flop SET/RESET, El Flip Flor D , Desarrollo de ejercicios en clases. Tarea: Ejercicios propuestos en clases. Participación en clases Evaluación practica en clases. Sesión 6 Preparación para la lección escrita próxima clase Lección escrita en clases. Flip Flop T, Flip Flop J-K Tarea: Estudio y lectura de los temas tratados en clases. Tiempo estimado No presencial: Estudio y lectura. Sesión 7 Conversión de Flip Flop Ejercicios. Tarea: Desarrollar E.P. en clases. Trabajo en equipo. Desarrollo de E.P. (recoger próxima clase) Unidad 2: Análisis y diseño secuencial Sesión 8 Sesión 9 Sesión 10 Sesión 11 Investigar sobre conversión de Flip Flop Participación en clases. Investigar sobre los diagramas de estado Participación en clases. Investigar sobre Análisis de circuitos secuénciales sincrónicos Participación en clases. Investigar sobre maquinas secuénciales de estado finito Participación en clases. El diagrama de estado Ejercicios y trabajos en clases Análisis de circuitos sincrónicos. Tarea: Desarrollar EP. Lección escrita en clases. Maquinas secuenciales de estado finito Investigar sobre procedimiento tradicional para el diseño secuencial sincrónico. Participación en clases. Procedimiento tradicional para el diseño secuencial sincrónico Tarea: Desarrollar E.P. y entregar semana antes del examen. Investigar sobre reglas para reducir estado Participación en clases. secuénciales Sesión 12 Sesión 13 Sesión 14 Sesión 15 Reglas de reducción de estado. Clase Práctica. Tarea: Ejercicios propuestos Investigar sobre minimización del decodificador de estado siguiente. Participación en clases. . Participación en clases. . Participación en clases. Participación en clases. Minimización del decodificador de estado siguiente Desarrollo de ejercicios. Lección escrita en clases. Continuación. Ejercicios con vistas a prepararse para el examen. Tarea: Estudio para el examen del primer parcial. Examen del primer parcial. Revisión con los estudiantes del examen. Tarea: Lectura independiente del texto , revisión de los temas tratados, continuación. Investigar sobre contadores Participación en clases. Sesión 17 Contadores: Tarea: Ejercicios propuestos Investigar sobre contadores en modo simple Participación en clases . Sesión 18 Diseño de contadores en modo simple Participación en clases . Contadores multimodo. Tarea: Ejercicios propuestos. Tiempo estimado No presencial: Participación en clases . Sesión 19 Ejercicios de los temas tratados en las últimas dos clases. Ejemplos a desarrollar en clases. Participación en clases . Sesión 16 Sesión 20 Investigar sobre contadores en modo múltiple . Investigar sobre los contadores de Rizo. Sesión 21 Sesión 22 Contadores de rizo. Tarea: Realizar ejercicios propuestos de clases Investigar sobre los contadores de anillo Participación en clases . Recoger EP(evaluativo) Lección escrita. Contadores de anillo Investigar sobre registros de desplazamiento Participación en clases . Registros de desplazamiento. Tarea: Realizar ejercicios propuestos de clases Investigar sobre el procesador de datos. Lenguaje RTL Participación en clases . Participación en clases . Investigar sobre implementación de controladores. Método clásico Participación en clases . Investigar sobre implementación de controladores. Método de un Flip Flop por estado Participación en clases . Investigar sobre el uso de decodificadores y multiplexores en los controladores Participación en clases . Sesión 23 Unidad 3: Diseño de sistemas de múltiple entrada múltiple salida Sesión 24 El procesador de datos Lenguaje RTL Sesión 25 Sesión 26 Sesión 27 Ejercicios en clases. Controlador del sistema Diagrama ASM Tarea: Desarrollar E.P., para entregar el día del examen final. Prepararse para lección escrita clase próxima. Lección escrita. Implementación del controlador. Clásico Tarea: Estudiar lo visto en clases Método Implementación del controlador método de un Flip Flop por estado Ejercicios en clases. Tarea: Desarrollo de E.P. Entregar día del examen final (evaluativo) Investigar sobre el controlador del sistema. Diagrama ASM Sesión 28 Sesión 29 Sesión 30 Sesión 31 Utilización de decodificadores y multiplexores en la implementación de controladores Tarea: Desarrollo de E.P. (adicionar al deber final) Estudio independiente con vistas a la lección escrita próxima clase. Investigar sobre el uso de contadores en la implementación del controlador Participación en clases clases. Investigar sobre el uso de registros de desplazamiento en la implementación del controlador Participación en clases . Participación en clases . Participación en clases Lección escrita. Implementación del controlador utilizando contadores. Tarea: Desarrollo de E.P. (adicionar al deber final) Estudio independiente con vistas al examen final. Implementación del controlador utilizando registros de desplazamiento Clase práctica. Desarrollo de ejercicios varios con vistas a prepararse para el examen final. Tarea: Estudio independiente con vistas al examen final. Clase práctica. Desarrollo de ejercicios varios con vistas a prepararse para el examen final. Tarea: Estudio independiente con vistas al examen final. Sesión 32 Examen final 4. EVALUACIÓN 5 .- Actuación individual Elaboración de ejercicios Comprensión de lectura Trabajos de investigación 25 pts. 25 pts. 25 pts. 25 pts Evaluación Parcial 100 pts. . BIBLIOGRAFÍA BÁSICA (Books, Video, papers, software aplicativos) 1. Texto: Análisis y diseño de circuitos lógicos digitales de Víctor Troy Prentice Hall 2. Apuntes personales ( folleto) 3. Engineering Approach to digital design por William Fletcher Prentice Hal 6 .- BIBLIOGRAFIA COMPLEMENTARIA (Bibliography Complementary) 1. Sistemas digitales principios y aplicaciones por Ronald Tocci 6 edición Prentice Hall. 2. Principios de diseño lógico digital Norman baladanian y Bradley Carlson CECSA 3. Sistemas digitales de Morris Mano 7 .- DATOS DEL PROFESOR (Teacher´s Resume) NOMBRE: TITULO DE PREGRADO: TITULOS DE POSTGRADO: E-Mail: Marcos Tobar Moran Ingeniero Eléctrico especialización Electrónica (por obtenerla) [email protected]