Introducción a los DSP. La aritmética binaria en los DSP

Anuncio

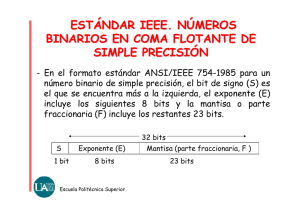

PROCESAMIENTO DIGITAL DE SEÑALES ORIGEN: DÉCADAS DE LOS 50 Y 60 INTERÉS EN SIMULAR EL COMPORTAMIENTO DE SISTEMAS ANALÓGICOS DE PROCESAMIENTO ANTES DE CONSTRUIR UN PROTOTIPO ENORMEMENTE CARO - LA HERRAMIENTA PARA ELLO FUE EL COMPUTADOR - NATURALEZA DEL COMPUTADOR: DIGITAL - UNA VEZ ESTABLECIDA LA BASE MATEMÁTICA ASÍ COMO LOS ALGORITMOS QUE PERMITEN EL PROCESAMIENTO DIGITAL, SE DIO EL PASO PARA DEFINIR ARQUITECTURAS DE COMPUTADORES QUE SE ADAPTASEN DE MODO IDÓNEO A LA IMPLEMENTACIÓN DE ESTOS ALGORITMOS - EN UN PRINCIPIO NO RESULTABA POSIBLE EL PROCESAMIENTO EN TIEMPO REAL Æ PROCESAMIENTO FUERA DE LÍNEA: PROCESADO CAPTACIÓN DE LA ALMACENAMIENTO (COMPUTADOR) SEÑAL - LOS SISTEMAS DSP TARDAN CONSIDERABLEMENTE MENOS TIEMPO EN EL PROCESAMIENTO DE LA SEÑAL QUE LOS SISTEMAS COMPUTADORES CON ARQUITECTURAS CONVENCIONALES PROCESADORES DIGITALES DE SEÑAL • PRIMEROS DSPs: • 1971: APARECE EL FDP (Fast Digital Processor). POSEE ARQUITECTURA VON NEUMANN CLÁSICA, Y ESTÁ COMPUESTO POR 10.000 COMPONENTES DISCRETOS • OTRO DSP ES EL LSP/2: POSEE ARQUITECTURA HARVARD. CUADRUPLICA LA VELOCIDAD DEL ANTERIOR, Y DIVIDE POR 3 EL NÚMERO DE COMPONENTES • DÉCADA DE LOS 70: APARECE LA TECNOLOGÍA VLSI, QUE PERMITE ELEVADÍSMOS NIVELES DE INTEGRACIÓN • AÑOS 1980-81: APARECE EL PRIMER DSP MONOPASTILLA TAL Y COMO HOY SE CONOCE: • AMI S2811 • NEC µPD7720 • TMS320C10 (en 1982) ¿POR QUÉ EL PROCESAMIENTO DIGITAL DE SEÑALES? • EL ENFOQUE ANALÓGICO ES: • MÁS RÁPIDO Æ MAYOR ANCHO DE BANDA • PERO (MUCHO) MÁS COMPLEJO • EN OCASIONES RESULTA INABORDABLE • NO ES ADAPTATIVO • EL ENFOQUE DIGITAL TIENE COMO VENTAJA: • PROGRAMABILIDAD: • ESTABILIDAD: • REPETITIBILIDAD: • FACILIDAD DE ALGORITMOS • POSIBILIDAD DE EMPLEO DE TÉCNICAS DE CORRECCIÓN DE ERRORES • POSIBILIDAD DE IMPLEMENTACIÓN FUNCIONES ESPECIALES: COMPRESIÓN ADAPTABLE DIVERSAS NO HAY DEPENDENCIA DE LOS COMPONENTES ANALÓGICOS (R, C, AOs) A FACTORES COMO TEMPERATURA, HUMEDAD, PRESIÓN, ENVEJECIMIENTO, TOLERANCIA SOBRE LOS VALORES NOMINALES. ASÍ, ES POSIBLE LA COMPENSACIÓN DE LA DERIVA DE LOS ELEMENTOS ANALÓGICOS RESULTADO IDÉNTICO INDEPENDIENTEMENTE DEL EQUIPO DSP CONCRETO QUE REALICE EL PROCESO IMPLEMENTACIÓN PÉRDIDA, FILTROS DE RANURA, ETC... • A TAREAS MENOR TAMAÑO DEL SISTEMA DE DE SIN RASGOS CARACTERÍSTICOS COMUNES DE LOS DSPs FRENTE A LOS µPs Y µCs • MULTIPLICACIÓN-ACUMULACIÓN (MAC) RÁPIDA • ARQUITECTURA CON MÚLTIPLES ACCESOS: MEMORIA QUE PERMITA - FLUJO SIMULTÁNEO DE INSTRUCCIONES Y DATOS - FLUJO SIMULTÁNEO DE VARIOS DATOS • MODOS DE DIRECCIONAMIENTO ESPECIALES PARA: - OPTIMIZAR LA MANIPULACIÓN DE MATRICES - OPTIMIZAR LA IMPLANTACIÓN DE FIFOs - OPTIMIZAR CIRCULARES - OPTIMIZAR CIERTOS ALGORITMOS MATEMÁTICOS (por ejemplo, la FFT directa e inversa) LA IMPLANTACIÓN DE REGISTROS • CONTROL DE PROGRAMA ESPECIALIZADO PARA LA: - OPTIMIZACIÓN DE GESTIÓN DE BUCLES - OPTIMIZACIÓN DE LA LATENCIA A LAS INTERRUPCIONES - MINIMIZACIÓN DEL IMPACTO DEL VACIADO DE LA CADENA DE SEGMENTACIÓN EN LAS BIFURCACIONES • PERIFÉRICOS INTEGRADOS E INTERFACES DE E/S FUNCIONES CARACTERÍSTICAS EN EL PROCESAMIENTO DIGITAL DE SEÑALES • EN EL PROCESAMIENTO DIGITAL DE SEÑALES SE USAN TÉCNICAS DE CONVOLUCIÓN, CORRELACIÓN, ETC... • MATEMÁTICAMENTE, SE REALIZAN PROCESOS DEL TIPO: N-1 Σ(ai.xi) i=0 • POR EJEMPLO, EN UN FILTRO TIPO FIR TENEMOS QUE: M yi = Σ(ak.xi-k ) k=0 xi-k = yi = ai = M = xi valor de la muestra “i-k” de la señal valor i-ésimo de la salida filtrada coeficiente i-ésimo de filtrado número de etapas del filtrado Z-1 ao X a 1 Z-1 X Σ a Z-1 2 X Σ a 3 X Σ yi LA REPRESENTACIÓN NUMÉRICA: COMA FIJA Y COMA FLOTANTE COMA FIJA ENTEROS 7 6 5 4 3 2 FRACCIONARIOS 1 0 B S 7 6 5 4 3 2 1 0 B S -27 26 25 24 23 22 21 20 -20 2-1 2-2 2-3 2-4 2-5 2-6 2-7 • RESOLUCIÓN: ENTEROS 1, FRACCIONARIOS 1/2n • RESULTADOS QUE EXCEDEN DE LA CAPACIDAD DE REPRESENTACIÓN: - REBOSAMIENTO Æ POSIBILIDAD DE ARITMÉTICA µP Y DSP) DE PRECISIÓN EXTENDIDA (µ - SATURACIÓN (DSP) • VALORES A PROCESAR QUE EXCEDEN LA CAPACIDAD DE REPRESENTACIÓN: - NECESIDAD DE ESCALADO • EN CONJUNTO: LA ARITMÉTICA ENTERA PUEDE REQUERIR MUCHA MAYOR COMPLEJIDAD ALGORÍTMICA LA REPRESENTACIÓN NUMÉRICA: COMA FIJA Y COMA FLOTANTE COMA FLOTANTE • REPRESENTACIÓN CON MANTISA Y EXPONENTE S MANTISA S EXPONENTE N = ±M.2±exp La mantisa es de coma fija fraccionaria, y se supone siempre implícito un bit entero a 1 El exponente es un entero de coma fija • LA DISTRIBUCIÓN DE LOS VALORES NO ES UNIFORME, AL CONTRARIO DEL CASO DE LA COMA FIJA • MAYOR PRECISIÓN EN LA REPRESENTACIÓN DE LOS VALORES: A VALORES PEQUEÑOS LAPSOS PEQUEÑOS, A VALORES GRANDES LAPSOS GRANDES. EL LAPSO ES DEL ORDEN DE 10-7 DE LAS MAGNITUDES REPRESENTADAS • MAYOR RANGO DINÁMICO QUE EN LA REPRESENTACIÓN EN COMA FIJA (A IGUAL NÚMERO DE BITS EMPLEADOS) • MEJOR RELACIÓN SEÑAL/RUIDO • MUCHO MAYOR COSTE DE DISPOSITIVOS MÁS COSTOSOS IMPLEMENTACIÓN ⇒ LA MULTIPLICACIÓN BINARIA 0110 x1101 0110 0000 0110 0110 1001110 CASO DE ENTEROS SIN SIGNO: 01102 ≡ 6 10 11012 ≡ 1310 6x13 = 78 ≡ 1001110 ⇒ RESULTADO CORRECTO CASO DE ENTEROS CON SIGNO: 01102 ≡ +610 11012 ≡ -310 (+6)x(-3) = -18 ≡ 1101110 ≠1001110 ⇒ RESULTADO INCORRECTO CASO DE FRACCIONARIOS SIN SIGNO: 01102 ≡ 0'37510 11012 ≡ 0'812510 ( 0'375)x(0'8125) = 0'3046875 ≡ 0100111 ≠ 1001110 ⇒ RESULTADO INCORRECTO CASO DE FRACCIONARIOS CON SIGNO: 01102 ≡ +0'7510 11012 ≡ -0'37510 (+0'75)x(-0'375) = -0'28125 ≡ 1101110 ≠ 1001110 ⇒ RESULTADO INCORRECTO CONCLUSIÓN: EXISTE LA NECESIDAD DE ALGORITMOS ESPECÍFICOS PARA LA ARITMÉTICA BINARIA ENTERA CON SIGNO, Y TAMBIÉN PARA LA ARITMÉTICA BINARIA FRACCIONARIA CON Y SIN SIGNO. MULTIPLICACIÓN BINARIA CON SIGNO (N bits) x (N bits) Æ (2N-1 bits) ENTEROS S S FRACCIONARIOS S S ∏ ∏ S S MSP LSP RESULTADO DE 2n-1 BITS Extensión del bit de signo (para cumplir la Ley de Conservación de bits) S MSP LSP 0 RESULTADO DE 2n-1 BITS Bit menos significativo a 0 (para cumplir la Ley de Conservación de bits) • VENTAJAS DE LA REPRESENTACIÓN FRACCIONARIA: - EL MSP (PARTE MÁS SIGNIFICATIVA DEL PRODUCTO) TIENE EL MISMO FORMATO DE LOS OPERANDOS. - EL LSP (PARTE MENOS SIGNIFICATIVA) PUEDE REDONDEARSE SIN NECESIDAD DE DESPLAZAR O ACTUALIZAR EL EXPONENTE (ÚTIL EN COMA FLOTANTE POR BLOQUES). - NO SE PIERDE UN BIT MÁS SIGNIFICATIVO DEBIDO A LA EXTENSIÓN DE SIGNO ⇒ MAYOR RANGO DINÁMICO. - CONVERSIÓN MÁS SENCILLA A REPRESENTACIÓN EN COMA FLOTANTE, DADO QUE LA MANTISA ES FRACCIONARIA. - LOS COEFICIENTES PARA EL FILTRADO DIGITAL SUELEN SER FRACCIONARIOS, LO CUAL SIMPLIFICA EL PROCESO. - SI RESULTA PRECISO EL PASO FRACCIONARIO Æ ENTERO, BASTA CON UN DESPLAZAMIENTO ARITMÉTICO A LA DERECHA . MULTIPLICACIÓN BINARIA CON SIGNO, CON REPRESENTACIÓN EN COMA FIJA IMPLEMENTACIÓN EN DSPs CASO 1 • LA ARQUITECTURA ES CAPAZ TANTO DE ARITMÉTICA ENTERA COMO FRACCIONARIA Æ NINGÚN PROBLEMA EN LA OBTENCIÓN DEL RESULTADO CASO 2 • LA ARQUITECTURA SÓLO ES CAPAZ DE ARITMÉTICA ENTERA CON SIGNO: SI SE OPTA POR REPRESENTACIÓN FRACCIONARIA ES PRECISO ADAPTAR O CORREGIR EL RESULTADO, MEDIANTE UN DESPLAZAMIENTO ARITMÉTICO A LA IZQUIERDA: Resultado entero y su corrección a fraccionario: S S Resultado fraccionario resultante: S 0 0 CASO 3 • LA ARQUITECTURA SÓLO ES CAPAZ DE ARITMÉTICA FRACCIONARIA CON SIGNO: SI SE OPTA POR REPRESENTACIÓN ENTERA ES PRECISO ADAPTAR O CORREGIR EL RESULTADO, MEDIANTE UN DESPLAZAMIENTO ARITMÉTICO A LA DERECHA: Resultado fraccionario y su corrección a entero: S 0 Resultado entero resultante: S S ALGORITMO DE MULTIPLICACIÓN CON SIGNO MULTIPLICACIÓN DE 2 NÚMEROS CON SIGNO, DE n BITS PRODUCTO (P) Å 0 iÅ0 no ¿BIT i DEL MULTIPLICADOR =1? si si no ¿i = n-1? M’ Å 2n-( MULTIPLICANDO<<i) (EXTENDIDO EN SIGNO HASTA LOS (2n)-1 BITS) M’ Å MULTIPLICANDO<<i (EXTENDIDO EN SIGNO HASTA LOS (2n)-1 BITS) P Å P+M’ ¿i = n-1? no i Å i+1 si entera ¿TIPO DE ARITMÉTICA? EXTENDER EL BIT DE SIGNO PARA COMPLETAR LOS 2n BITS DEL PRODUCTO (*) fraccionaria AÑADIR A LA DERECHA UN BIT DE MENOR PESO A 0 PARA COMPLETAR LOS 2n BITS DEL PR. (*) FIN (*) Ley de conservación de bits: (“n” bits) x (“n” bits) = (“2n” bits)