cronometro digital - Universidad Santiago de Cali

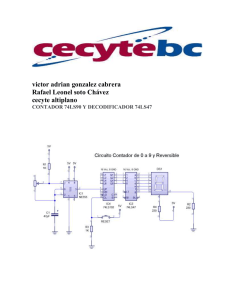

Anuncio

GUIAS ÚNICAS DE LABORATORIO CRONOMETRO DIGITAL AUTOR: ALBERTO CUERVO SANTIAGO DE CALI UNIVERSIDAD SANTIAGO DE CALI DEPARTAMENTO DE LABORATORIOS DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCRROONNOOM MEETTRROO DDIIGGIITTAALL CRONÓMETRO DIGITAL OBJETIVO Los contadores son uno de los circuitos digitales de mayor aplicación en la construcción de sistemas lógicos electrónicos. Éstos pueden ser sincrónicos o asincrónicos. Los contadores sincrónicos constituyen un caso particular de circuito secuencial sincrónico en donde los pulsos de entrada que se van a contar se inyectan a la entrada de reloj o de pulsos de todos los flip-flops que componen el contador, obligando a los flip-flops a cambiar de estado de forma simultánea con la sola diferencia en los tiempos de operación de los flip-flops individuales. El cambio de estado de cada uno de los flipflops será función de los valores lógicos presentes en las entradas de excitación (SR, JK o D) de cada uno de los flip-flops. A diferencia de los contadores sincrónicos, en los contadores asincrónicos los pulsos de cuenta no se inyectan a todas las entradas de reloj de los flip-flops de forma simultánea, causando una mayor simplicidad en el circuito del contador, pero una mayor lentitud en su operación. La presente práctica tiene como objetivo familiarizar al estudiante en la operación de los circuitos de contadores con el diseño de un circuito práctico como es el caso del cronómetro digital. PLANTEAMIENTO DEL PROBLEMA Diseñar el circuito de un cronómetro digital, con las señales que se muestran en el diagrama siguiente. El cronómetro deberá poder contar el tiempo en segundos desde 0 hasta 39 segundos en forma decimal. Contar CRONÓMETRO SALIDA Borrar DIGITAL reloj Al display de 7 segmentos Por tanto el cronómetro tendrá dos digitos decimales, el dígito de las unidades y el dígito de las decenas, los cuales deberán ser llevados al display de 7 segmentos para poder visualizar el número de segundos transcurridos desde que se arranca a contar al cronómetro hasta que se detiene. Los pulsos de reloj deben ser obtenidos del generador de frecuencias (27) y divisor de frecuencias (28) con la frecuencia apropiada. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCRROONNOOM MEETTRROO DDIIGGIITTAALL Las señal de “Contar “ será obtenida de un teclado (31) Cuando Borrar = 1, el contador se repone a 0 segundos. Cuando Contar = 1 el cronómetro arranca, y cuando Contar se regresa a 0 se detiene el cronómetro. Para el dígito de las unidades, utilice el circuito integrado del contador binario sincrónico (39) convertido en contador decimal (0...9) utilizando su entrada de cargar datos en paralelo. Para el dígito de las decenas utilice flip-flops JK. Para este dígito implemente un contador binario asincrónico de 0 a 3, ya que la velocidad del contador es muy lenta, y el contador asincrónico necesita menos circuitos para su realización que el sincrónico. Utilice como máximo dos compuertas AND/NAND, especificando muy bien todas las conexiones que se deben efectuar en el montaje del circuito en el laboratorio. SOLUCIÓN. El diagrama en bloques del cronómetro se muestra en el diagrama siguiente, el cual está compuesto de dos contadores: un contador decimal para el dígito de las unidades y un contador binario de 0 a 3 para el dígito de las decenas. Los pulsos de reloj con una frecuencia de 1 Hz (1 pulso por segundo) incrementan al contador de las unidades. Cuando ocurra el décimo pulso el dígito de las unidades pasa a 0 y produce una transición que provoca que el dígito de las decenas se incremente, etc. Cronómetro digital Decenas Unidades Contar reloj 8 4 2 1 8 4 2 1 Por ejemplo, si el número en el cronómetro es el 09 (0000, 1001), al ocurrir el flanco positivo del décimo pulso en la entrada del contador de las unidades este pasa a 0 (0000), la transición negativa de 1 a 0 del bit de mayor orden del contador de las unidades se aplica al contador de las decenas haciéndolo incrementar y pasando a 1 (0001). DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCRROONNOOM MEETTRROO DDIIGGIITTAALL La función de la compuerta NAND consiste en bloquear los pulsos de reloj cuando Contar =0. Si Contar = 0, la salida de la compuerta NAND =1 y no se aplican pulsos al cronómetro. Se muestra el circuito digital del cronómetro digital Display de 7 segmentos CTRDIV16 BORRAR CT=0 Contar 2+ G1 1- reloj 1 Hz G2 decenas unidades C3 2+/G1: entrada de pulsos para conteo creciente 1 2 4 8 C3: entrada asincrónica de carga que se activa con 0 CT=0: entrada asincrónica de borrado que se activa con 1 entrada bit mayor orden BORRAR 1J 1K R pulsador BORRAR 1 2 4 8 Q0 1J Q1 1K R 1 Observación: Con un nivel alto en la entrada (CT=0), se borra el contador En el circuito el contador binario de las decenas está compuesto por dos flip-flops, pués éste nada más debe contar de 0 a 3 (00 a 11) según las especificaciones. En el contador binario CTRDIV16, la entrada C3 es alimentada por una compuerta NAND para que cuando ocurra el décimo pulso y este contador pase a 1010 momentáneamente DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCRROONNOOM MEETTRROO DDIIGGIITTAALL la entrada C3 se haga 0 y se cargue el número presente en su entrada (0000). De esta forma se obliga a este contador a pasar del número 9 (1001) al 0 (0000). Finalmente la señal Borrar lleva a 0 a todo el cronómetro según la conexión efectuada. BIBLIOGRAFÍA 1. Víctor P. Nelson, H. Troy Nagle, Bill D. Carroll y J. David Irwin, “Análisis y Diseño de Circuitos Lógicos Digitales “, Prentice-Hall Hispanoamericana S.A., 1996 2. System Technick, “DIGI BOARD2 Descripción Técnica “ DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCRROONNOOM MEETTRROO DDIIGGIITTAALL