circuitos contadores - Universidad Santiago de Cali

Anuncio

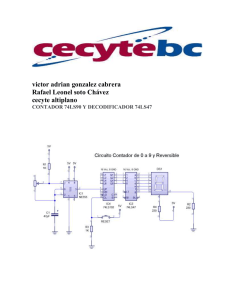

GUIAS ÚNICAS DE LABORATORIO CIRCUITOS CONTADORES AUTOR: ALBERTO CUERVO SANTIAGO DE CALI UNIVERSIDAD SANTIAGO DE CALI DEPARTAMENTO DE LABORATORIOS DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS CIRCUITOS CONTADORES Introducción El contador es un circuito específico de circuito secuencial, pudiendo ser sincrónico o asincrónico. El objetivo de esta práctica de laboratorio consiste en reforzar los conocimientos del estudiante en el análisis y diseño de circuitos contadores, tanto sincrónicos como asincrónicos, implementando y verificando los circuitos diseñados en el Módulo DIGI BOARD2 disponible en el laboratorio de la Universidad Santiago de Cali. Contador Sincrónico En un contador sincrónico, como en cualquier circuito secuencial sincrónico, los pulsos de reloj alimentan simultáneamente las entradas de reloj de todos los flip-flops que forman el contador, de forma tal que estos cambian de estado en forma simultánea con la única diferencia en las desigualdades en las demoras de cada uno de los flip-flops individuales. Los pulsos de entrada se aplican a la entrada de reloj del contador, incrementándose si es un contador que cuenta en sentido ascendente o decrementándose en caso contrario con cada pulso aplicado a la entrada. En la figura 1a se ha representado el esquema general de un circuito secuencial sincrónico con 3 flip-flops JK en el cual se ha dividido el bloque de lógica combinacional en dos: la lógica que produce las señales de salida y la lógica que produce las funciones de excitación a los flip-flops. En b se ha representado un caso específico de los contadores en que las señales de salida del circuito secuencial son directamente las señales de salida de los flip-flops. Así, en este último caso, si es un contador en el sistema binario, el estado 5 por ejemplo será el estado 101, es decir que C=1, B=0 y A=1, etc. En el caso b entonces únicamente será necesario encontrar las funciones de excitación JK de cada flip-flop en función del estado presente (las salidas de los flip-flops) y la señal de entrada. Las señales o la señal de entrada al contador puede ser por ejemplo una señal que le indique al contador que cuente en sentido ascendente o descendente. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS señal de entrada Lógica combinacional señales de salida C B A señales de salida Lógica combinacional señal de entrada Lógica combinacional A J A J A´ K A´ K B J B J B´ K B´ K C C´ C J K C´ PULSOS DE ENTRADA J K PULSOS DE ENTRADA Figura 1. Circuito secuencial. a.- caso general y b.- las salidas de los flipflops son directamente las salidas del circuito secuencial. En un contador, la señal de entrada puede no existir, obteniéndose el esquema que se representa en la figura 2. En este caso, las entradas de excitación de los flip-flops que determinan el estado siguiente dependerán únicamente del estado presente, es decir, de las salidas de los flip-flops que forman el contador. El primer circuito que se deberá diseñar corresponderá al esquema de la figura 2. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS señales de salida C B A Lógica Combinacional A A´ B B´ J K J K C J C´ K PULSOS DE ENTRADA Figura 2. Circuito secuencial de un contador sin señal de entrada externa. Planteamiento del primer circuito. Diseñar un contador que cuente en binario en sentido ascendente de 0 a 5 con flip-flops JK y compruebe el funcionamiento del mismo en el módulo DIGI BOARD2 del laboratorio llevando las salidas del mismo a un display de 7 segmentos y aplicándole pulsos con el pulsador. Solución. Como el contador tiene 6 estados: 0, 1, 2….5, se necesitarán 3 flip-flops que se denominarán C, B y A respectivamente. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS El primer paso será construir la tabla de estado presente y estado siguiente para encontrar las funciones de excitación JK de cada flip-flop. Esta tabla es muy simple y se muestra en la figura 3. Estado Estado presente siguiente CBA CBA 000 001 001 010 010 011 011 100 100 101 101 000 110 xxx 111 xxx JA KA JB KB JC KC 1 x 1 x 1 x x x x 1 x 1 x 1 x x 0 1 x x 0 0 x x x x 0 1 x x x x 0 0 0 1 x x x x x x x x 0 1 x x Figura 3. Tabla de estado presente y estado siguiente. Observe que los estados #6=110 y #7=111 son estados no usados, nunca ocurren, por lo que no importa los estados siguientes de los mismos. De la tabla de la figura 3 se pueden construir los mapas de Karnaugh que se muestran en la figura 4 para obtener las funciones simplificadas de la J y la K de cada uno de los flip-flops del contador. Con estas funciones se puede implementar el circuito del contador que se muestra en la figura 5, en el cual el pulsador se utiliza para aplicarle pulsos al contador, y la salida de éste es llevada a un display de 7 segmentos para verificar el número binario almacenado en el contador de acuerdo al número de pulsos aplicado. El diagrama de estados incluyendo los estados no usados 6 y 7 se muestra en la figura 6. Cuando el circuito tenga el número 6: CBA= 110, se tiene que: • JA=KA=1, por tanto el flip-flop A cambia de 0 a 1 • KB=AC´=0, por lo que el flip-flop B se queda en el estado 1 y • KC=A =0, por lo que el flip-flop C también se queda en el estado 1. De acuerdo a lo anterior, el circuito pasa del 6 al 7 cuando se le aplique un pulso. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS BA 00 01 11 10 C BA 00 01 11 10 C BA 00 01 11 10 C 0 1 x x 1 0 x 1 1 x 0 0 1 x x 1 1 x x x 1 x 1 x x 1 0 0 x x JA=1 KA=1 BA 00 01 11 10 BA 00 BA 01 11 10 0 x x 1 0 0 0 0 1 0 C 0 1 x x x x 1 x x x x 1 C C JB=AC´ KB= A ó AC´ 00 01 11 10 x x x x 0 1 x x JC=AB KC=A Figura 4. Mapas de Karnaugh J C J B J A K C´ K B´ K A´ display pulsador 1 +5v. pulsos de entrada 1 2 4 8 Figura 5. Circuito del contador DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS Igualmente, si por alguna razón el circuito tuviese almacenado el número 7 (CBA=111),se tiene que: • JA=KA=1, por lo que el flip-flop A cambiará de 1 a 0 • KB=AC´=0, por lo que el flip-flop B se queda en el estado 1 y • KC=A=1, por lo que el flip-flop C cambiará de 1 a 0 De acuerdo a lo anterior el circuito pasará del 7 al 2 cuando se le aplique un pulso. 5 estados inválidos 0 6 secuencia válida 4 1 7 3 2 Figura 6. Diagrama de estados Este diagrama de estados representa un contador “autocomenzante”, pués cuando se conecte la energía si el contador cae inicialmente en uno de los estados no-usados o inválidos, a los pocos pulsos aplicados, máximo 2 en este caso, cae en la secuencia válida y ya no sale de ésta. Coloque con las entradas asincrónicas de los flip-flops los números 6 y 7 en el contador y compruebe el estado siguiente de estos estados inválidos. Contador Asincrónico En un contador asincrónico a diferencia del contador anterior, los pulsos no se aplican simultáneamente al reloj de todos los flip-flops. Puesto que los flip-flops en el contador asincrónico no están bajo el mando de un solo pulso de reloj, es más lento que el contador sincrónico, aunque el hardware requerido es más simple. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS El más sencillo de todos los contadores asincrónicos es el contador binario, que cuente en binario hasta 2n – 1 (n estados), donde n es el número de flip-flops utilizado. Monte el circuito que se muestra en la figura 7 el cual consiste en un contador binario que cuenta de 0 (0000) a 15 (1111), por lo que tendrá 16 estados y 4 flipflos JK. +5v. H Q3 J Q2 J Q1 J Q0 J Q3 K Q2 K Q1 K Q0 K flip-flop de mayor orden flip-flop de menor orden pulsos de Q entrada 1 2 4 pulsador 8 (a) display pulsos de entrada 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Q0 Q1 Q2 Q3 0001 0010 0011 0100 0101 0110 estado inicial: Q3Q2Q1Q0 = 0000 0111 1000 1001 1010 1011 1100 1101 1110 1111 (b) Figura 7. Contador asincrónico binario (a) circuito (b) formas de onda DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS 0000 Este contador se implementa como se muestra en la figura 7 colocándo en 1 lógico la J y la K de todos los flip-flops. Los pulsos de entrada se inyectan al reloj del flip-flop de menor orden y la salida de cada flip-flop se conecta al reloj del siguiente. Como los flip-flops son de flanco negativo, debido a esta conexión el flip-flop Q0 cambiará de estado cuando ocurra un flanco negativo en los pulsos de entrada, el flip-flop Q1 cambiará de estado cuando ocurra un flanco negativo en Q0, y así sucesivamente. Como se puede observar de las formas de onda de las salidas de los flip-flops, el número binario almacenado en el contador corresponde al número de pulsos que se hayan inyectado en su entrada. Inyecte pulsos al contador con el pulsador y compruebe el número en el display. Conecte la salida negada de cada flip-flop al reloj del siguiente y compruebe que el contador se comporta como un contador binario que cuenta en sentido descendente. Circuitos integrados de contadores Debido al gran número de aplicaciones que tienen los contadores, existe una gran variedad de los mismos fabricados en forma de circuitos integrados. En la figura 8 se muestra un ejemplo disponible en el módulo DIGI BOARD2 del laboratorio. Consiste del circuito integrado 74LS193, el cual es un contador binario de 4 bits que puede contar en ambos sentidos: ascendente y descendente. El sentido de conteo del circuito depende a la entrada donde se apliquen los pulsos: Up o Down. Igualmente tiene una entrada asincrónica CLR, la cual al activarse con un 1 borra al contador y una entrada asincrónica LOAD´ la cual al activarse con un 0 almacena el número presente en sus entradas DCBA en el contador. Tiene dos salida para conectar estos circuitos en cascada si se necesita implementar un contador de un mayor número de bits: la salida de acarreo (carry´) para el conteo creciente y la salida de préstamo (borrow´) para conteo decreciente. Estas señales se muestran en la figura 9. En la misma se puede observar que si el contador se encuentra contando en sentido ascendente, en el pulso 16 pasa a 0 (0000). DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS entradas 9 5 4 14 11 CTRDIV16 10 D C Up Down 1 B Down A Carry 74LS193 CLR Borrow LOAD QD QC 7 QB 6 CLR Up 15 12 13 QA A Carry Borrow C3 QA 3D QB B entradas 3 2 LOAD CT=0 2+ 1ct = 15 G1 1G2 2ct = 0 salidas C D bit de mayor orden salidas (a) QC QD (b) CLR: entrada asincrónica de borrado, cuando se activa con un 1 se coloca al contador en 0000 Up: entrada de pulsos para conteo creciente, sensible al flanco positivo Down: entrada de pulsos para conteo decreciente, sensible al flanco positivo LOAD: entrada asincrónica que al activarse con un 0 se carga o almacena el número presente en las entradas Carry: salida de acarreo, al alcanzar el nº 15 (1111) esta salida cambia a 0 cuando la entrada Up=0 Borrow: salida de préstamo, al alcanzar el nº 0 (0000) esta salida cambia a 0 cuando la entrada Down=0 Figura 8 Contador sincrónico binario (a) símbolo estándar, (b) símbolo de la IEEE Sin embargo, la salida de acarreo se puede aplicar a la entrada Up de otro circuito haciendo que el mismo pase a 0001, y así tendríamos un contador de 8 bits con el número 00010000 (#16) almacenado, etc. 1101 1110 14 1111 15 0000 16 número almacenado pulsos aplicados a la entrada Up señal en la salida Carry La salida Carry se activa con un 0 cuando tiene el número 15 y UP=0 Figura 9. Señales en el contador DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS Alteración del conteo. La secuencia de conteo de un contador puede ser alterada para contar en una base diferente. Así por ejemplo, suponga que se desee obtener un contador decimal que cuente del 0 al 9 y en el décimo pulso regrese al 0 con el circuito integrado anterior. Este circuito se muestra en la figura 10 el cual debe ser montado en el laboratorio y comprobado su funcionamiento. CTRDIV16 pulsador Q CLR Up Down CT=0 2+ G1 1- G2 1ct=15 2ct=0 C3 LOAD A QA 1 B QB 2 C QC 4 D QD 8 display Figura 10. Contador decimal En el contador binario CTRDIV16 de la figura 10, la entrada de LOAD´ es alimentada por una compuerta NAND para que cuando ocurra el décimo pulso y este contador pase a 1010 momentáneamente la entrada LOAD´ se haga 0 y se cargue el número presente en su entrada (0000). De esta forma se obliga a este contador a pasar del número 9 (1001) al 0 (0000). Bibliografía 1. M. Morris Mano, “Lógica Digital y Diseño de Computadores”, Editorial Dossat S.A., 1982 2. Víctor P Nelson, H. Troy Nagle, Bill D. Carroll y J. David Irwin, “Análisis y Diseño de Circuitos Lógicos Digitales”, Prentice-Hall Hispanoamericana S.A., 1996 3. J. F. Wakerly, “Digital Design Principles and Practices”, 2ª ed., Englewood Cliffs, NJ: Prentice-Hall, 1984. DDEEPPAARRTTAAM MEENNTTOO DDEE LLAABBOORRAATTOORRIIOOSS GGUUIIAASS DDEE CCIIRRCCUUIITTOOSS CCOONNTTAADDOORREESS